(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1980 |

|

SU924853A2 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970678A1 |

| Преобразователь напряжения в код | 1979 |

|

SU828402A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1972 |

|

SU428546A1 |

| Преобразователь напряжения в код | 1976 |

|

SU577670A2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1972 |

|

SU432675A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1971 |

|

SU440784A1 |

Изобретение относится к вычислительной технике и может быть использовано для преобразования напряжения в код при построении цифровых приемных трактов. Известен преобразователь напряжения в код, содержащий источник преобразуемого напряжения, сравнивающий блок, преобразователи кода в напряжение (ПКН), регистры порядка и мантиссы, блок управления, генератор тактов, дешифратор, шифратор. Один из входовсравнивающего блока подключен к выходу источника преобразуе мого напряжения, другой - к выходу ПКН порядка, а выход - к однсму из входов блока управления, к другому входу последнего подключен выход генератора тактов, одни из выходов блока управления подключены ко входа регистра мантиссы, выходал которого подключены ко входам ПКН мантиссы, а другие выходы подключены ко вХодай регистра порядка, выходы которого через дешифратор подклк чены ко входам управления ПКН порядка, к инфор мационным входам этого ПКН подключен выход ПКН мантиссы l. Недостатком этого устройства является низкая точность преобразования сигналов малых уровней при большом динамическом диапазоне вход ных напряжений. Цель изобретения - повышение точности преобразования сигналов малых уровней при большом динамическом диапазоне входных напряжений. Поставленная цель достигается тем, что в преобразователь напряжения в код, содержащий источник преобразуемого напряжения, сравнийаюсцнй блок, преобразователь кода в напряжение, регистры мантиссы и порядка, шифратор и генератор тактов, включающий задающий генератор и триггер, при этом выходы регистра мантиссы соединены со входами преобразователя кода в напряжениеj выходы регистра порядка соединены со входами шифратора, а единичный выход триггера генератора тактов - со входом разрешения задающего генератора, введены распределители импульсов мантиссы и порядка, первый, второй и третий триггеры, первый, второй и третий элементы И, элемент ИЛИ, первый, второй и третий элементы задержки, делитель напряжения и коммутатор, причем источник преобразуемого напряжения последовательно соединен через

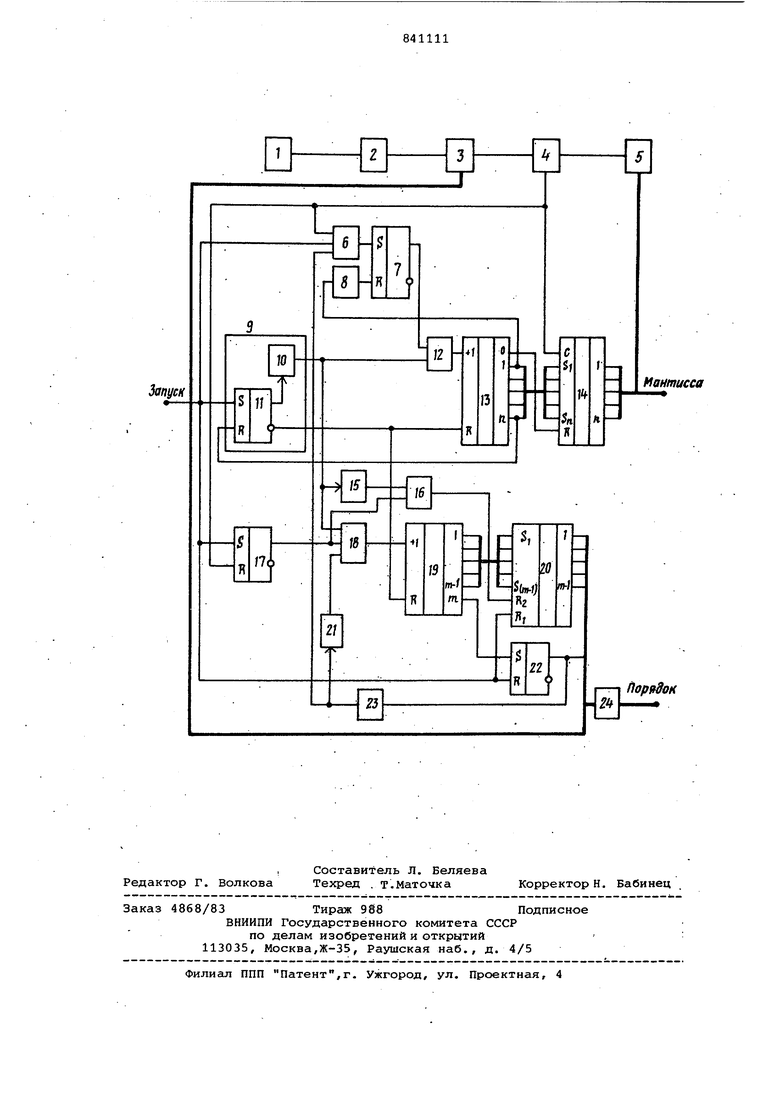

делитель напряжения и кор утатор с первым входом сравнивающего блока, ко второму входу которого подключен выход преобразователя кода в напряжение, а выход подключен ко входу элемента ИЛИ, к R-входу первого триггера и ко входу разрешения записи регистра мантиссы, при этом входная шина Запуск подключена к R-входам второго триггера и регистра порядка, к S-входу первого триггера и через элемент ИЛИ-к S-входу третьего триггера, а выход генератора тактов через первый элемент И подключен к счетному входу распределителя импульсов мантиссы, через второй элемент И к счетному входу распределителя импульсов порядка и через первый элемент задержки и третий элемент И ко второму R-входу регистра порядка, нулевой выход триггера генератора тактов подключен к R-входам распределителей импульсов порядка и мантиссы, а (m-l) выходы распределителя импульсов порядка подключены к (т-1) 5-в.ходам регистра порядка, при этом т-тый импульс подключен к Sв.хрду второго триггера, а выходы распределителя импульсов мантиссы подключены ко входам регистра мантиссы, кроме того, выход первого импульса ЭТОГО распределителя через второй элемент задержки подключен к R-входу третьего триггера, выход последнего импульса - к R-входу триггера генератора тактов, а выход нулевого импульса соединен с R-входом регистра мантиссы, единичные выходы регистра порядка и второго триггера подключены к управляющим входам коммутатора, кроме того единичный выход второго триггера через третий элемент задержки подключен к третьему входу элемента ИЛИ, а через инвертор подключен ко второму входу второго элемента И, единичный выход первого триггера подключен к третьему входу второго и второму входу третьего элементов И а единичный выход третьего триггера ко второму входу первого элемента И. На чертеже представлена блок-схема преобразователя напряжения в код.

Устройство содержит источник 1 преобразуемого напряжения, делитель 2 напряжения со ступенями деления, различающимися в два раза, коммутатор 3, сравнивающий блок 4, преобразователь кода в напряжение (ПКН) 5, элемент ИЛИ 6, триггер 7, элемент 8 задержки, генератор .9 тактов, включающий задающий генератор 10 и триггер 11, элемент И 12, распределитель 13 импульсов мантиссы, регистр 14 мантиссы, элемент 15 задержки, элемент И 16, триггер 17, элемент И 18, распределитель 19 импульсов порядка, регистр 20 порядка, инвертор 21, триггер 22, элемент 23 задержки, шифратор 24. Выход источника 1 преобразуемого напряжения через последовательно включенные делитель 2 напряжения и коммутатор подключен к одному из входов сравнивающего блока 4, к другому входу которого подключен выг ход ПКН 5, а выход сравнивающего блока 4 соединен со входом разрешения записи регистра 14 мантиссы, входом элемента ИЛИ бис R-входом триггера 17. Входная шина Запуск подключена Q к 5-входам триггеров 11, 17 и к Rвходам регистра 20 порядка и триггера 22, а к S-входу триггера 7 через элемент ИЛИ 6. Выходы регистра 14 мантиссы подключены ко входам ПКН 5 и к выходным шинам Мантисса, Выходы регистра 20 порядка и триггера 22 подключены к управлякмцим входам коммутатора 3 и через шифратор 24 к выходным шинам Порядок. Выход задающего генератора 10, генератора 9 0 тактов подключены через элемент И 12 к счетному входу распределителя 13 импульсов мантиссы, а через элемент И 18 к счетному входу распределителя 19 импульсов порядка и через элемент 5 15 задержки и элемент И 16 к R-входу регистра 20 порядка соответственно. Нулевой выход триггера 11 подключен к R-входам распределителей 13 и 19 импульсов Мантиссы и порядка соответQ ственно. Единичный выход триггера 17 подключен ко входам элементов И 16 и 18. Единичный выход триггера 7 подключен ко входу элемента И 12. Единичный выход триггера 11 подключен с ко входу разрешения задающего генератора 10. Единичный выход триггера 22 подключен через последовательно соединенные элемент 23 задержки и инвертор 21 ко входу элемента И 18. Выход элемента 23 задержки подклю0 чен ко -входу элемента ИЛИ б. Выходы распределителя 13 импульсов мантиссы подключены ко входам регистра 14 мантиссы. Кроме того, выход первого импульса распределителя 13 импульсов через элемент 8 задержки подключен к R-входу триггера 7, а выход последнего импульса - к R-входу триггера 11.

Устройство работает следующим 0 образом.

.Импульс запуска устанавливает триггеры 7, 11 и 17 в единичное состояние, а триггер 22 и регистр 20 - в исходное состояние. При

5 этом задающий генератор 10 формирует импульсы. Эти импульсы через элемент И 12 запускают распределитель 13 импульсов i Нулевой импульс этого распределителя импульсов устанавливает

0 в исходное состояние регистр 14,

а первый импульс устанавливает старший разрад регистра 14 в единичное состояние. В результате с выхода .ПКН 5 на второй вход сравнивающего блока 4 поступает напряжение, соответствующее напряжению старшего разряда ПКН 5. Кроме того, первый импульс распределителя 13 импульсов через элемент 8 задержки устанавливает триггер 7 в исходное состояние и импульсы задающего генератора 10 через элемент И 12 не проходят. Импульсы задающего генератора 10 через элемент И 18 также запускают распределитель 19 импульсов и через элемент 15 задержки и элемент И 16 поступают на второй R-вход регистра 20. Первый импульс распределителя 19 импульсов устанавливает триггер старшего разряда регистра 20 в состояние 1, включая тот ключ коммутатора 3, который подключает ступень делителя, соответствующую наибольшему ослаблению напряжения источника 1 преобразуемого напряжения. В результате на первый вход сравнивающего блока 4 поступает напряжение с наибольшим ослаблением. Если это напряжение меньше напряжения поступающего на второй вход сравнивающего блока 4, то последнее не срабатывает. В этом случае импульс, который переключает распределитель 19 импульсов, задержанный на время, определяемое временем задержки элемента 15 задержки, через элемент И 16 устанавливает триггер регистра 20 в исходное состояние. Следующий импульс задающего генератора 10 через элемент И 18 переключает распределитель 19 импульсов в следующее состояние, устанавливая следующий триггер регистра 20 в состояние 1. При этом включается следующий ключ коммутатора 3 и на первый вход сравнивающего блока 4 поступает напряжение а в два раза больше, чем на предьадущем такте. Если это напряжение меньше напряжения, поступающего на второй вход сравнивающего блока 4, то аналогично ранее рассмотренному, триггер регистра 20 устанавливается в исходное состояние.

Таким образом, устройство работае до того такта,-при котором напряжени поступающее с выхода коммутатора 3 на первый в-ход сравнивающего блока 4 меньше напряжения, поступающего на его второй вход с выхода ПКН 5. При срабатывании сравнивающего блока 4, его выходной импулЬс устанавливает триггер 17 в исходное состояние блокируя тем самым элементы И 16 и 18, и включенный в единичное состояние триггер регистра 20 остается в этом состоянии до поступления следующего импульса запуска. Состояние регистра 20 в этом случае соответствует унитарному коду порядка напряжения, поступающего с источника 1 преобразуемого напряжения. Этот код преобразуется шифратором 24 в двоичный код и поступает на выходные шины

Порядок. Тот же импульс сравнивающего блока 4 через элемент ИЛИ 6 устанавливает триггер в состояние 1. При этом импульсы с задающего генератора 10 проходят на вход распределителя 13 импульсов и начинается определение кода мантиссы напряжения, поступающего от источника 1 преобразуемого напряжения. Первый из этих импульсов устанавливает следующий триггер регистра 14 в состояние

10 1 (первый триггер регистра 14 уже переключен в состояние 1), подключая тем самым ко второму входу сравнивающего блока 4 напряжение, равное полови-не напряжения первого (старшего) 15 разряда ПКН 5. Если сумма этих двух напряжений больше напряжения, поступающего с выхода коммутатора 3 на первый вход сравнивающего блока 4, то второй триггер устанавливается в.ис20 ходное состояние, а е.сли сумма этих двух напряжений больше, то второй триггер также остается в состоянии 1.

На следующем такте производится уравновешивание следующего триггера

5 и т.д. В этом случае устройство работает как обычное устройство поразрядного уравновешивания. Если при включении младшего разряда регистра 20 сравнивающий блок 4 не сработает,

0 то все .триггеры регистра 20 устанав- ливаются в исходное состояние, а следующий импульс распределителя 19 импульсов устанавливает триггер 22 в состояние 1. Выходное н апряжение

5 этого триггера включает ключ коммутатора 3, подключенный к первому входу сравнивающего блока 4 выход дели-теля 2 напряжения с наименьшим коэффициентом деления. Это выходное на- о

0 пряжение, задержанное на время определяемое временем задержки элемента 23 и инвертируемое инвертором 21,блокирует прохождение импульсов через элемент И 18 на вход распределителя 19 импульсов. Кроме того, через эле5мент ИЛИ 6 это напряжение устанавливает в состояние 1 триггер 7, и тактовые импульсы, проходят через элемент И 12 на вход распределителя 13 импульсов, т.е. начинается опреде0ление кода мантиссы, соответствующей напряжению источника 1 преобразуемого напряжения, ангипогично рассмотренному, ранее. Последнийимпульс распределителя 13 импульсов устанавливает триггер 11 в исходное состояние 0. При этом задающий генератор 10 прекращает формировать импульсы, а распределители Импульсов 13 и 19 устанавливаются в состояние О. После окончания -преобразования Устройство находится в этом состоянии до прихода следующего импульса запуска.

В предлагаемом устройстве пOБ Jшeние точности преобразования, сигналов малых уровней при большом динамическом диапазоне входных напряжений достигается за счет, сжатия динамического диапазона входного напряжения на входе сравнивающего блока .ступенями, различающимися в два раза с эапсяиинанием числа ступеней,до величины, при которой напряжение на входе сравнивающего блока будет боль ше или равно напряжению, соответству щему 1 старшего разряда кода манти сы, а затем начинается определение кода мантиссы, как в обычных преобра зователях напряжения в код с поразря ным уравновешиванием. Сжатие динамического диапазона производится с помощью делителя, при чем максимальный входной сигнал делится в 2 раз (где m - число раз рядов регистра порядка), а минимальный входной сигнал - в 2 раз, т.е. минимальный сигнал на вход сравниваю блока проходит полностью. Величина напряжения младшего разряда в этом преобрезователе равна Uon/2 (где Uon напряжение источника опорного напряжения п число разрядов регистра мантиссы). Формула изобретения Преобразователь напряжения в код, содержёидий источник преобразуемого напряжения, сравнивающий блок, преоб разователь кода в напряжение, регист ра порядка и мантиссы, шифратор и генератор тактов, включающий задающий генератор и Tpifrrep, при этом вы ходы регистра мантиссы соединены со входами преобразователя кода в на. пряжение, выходы регистра порядка соединены со входами шифратора, а единичный выход триггера генератора тактов - со входом разрешения зада1ацего генератора, отличающийся тем что, с целью повыше ния точности преобразования сигналов малых уровней при большом динамическом диапазоне входных напряжений введены распределитель импульсов мантиссы, распределитель импульсов порядка, первый, второй и третий тр геры, первый, второй и третий элементы И, элемент ИЛИ, первый, второ и третий элементы задержки, делител напряжения и коммутатор, причем ист ник преобразуемого напряжения последовательно соединен через делитель напряжения и коммутатор с первым входом сравнивающего блока, ко второму -входу которого подключен выход преобразователя кода в напряжение, а выход подключен ко входу элемента ИЛИ, к R-ВХОДУ первого триггера и ко вхоДу разрешения записи регистра мантиссы, при этом входная шина Запуск подключена к В-входс1м второ.го триггера и регистра порядка, к S-входу первого триггера и через элемент ИЛИ к S-входу третьего триггера, а выход генератора тактов через первый элемент И подключен к счетному входу распределителя импулнсов мантиссы, через второй элемент И - к счетному входу распределителя импульсов порядка и через первый элемент задержки и третий элемент И - ко второму Rвходурегистра порядка, нулевой выход триггера генератора тактов подключен к R-входам распределителей импульсов порядка и мантиссы, а (гп-1) выходал распределителя импульсов.порядка подключены к (m-l) S-входам регистра порядка, причем т-тый импульс подключен к S-входу второго.триггера, а выходы распределителя импульсов мантиссы подключены ко входам регистра мантиссы, кроме того, выход первого импульса этого распределителя через второй элемент задержки подключен к R-входу третьего триггера, выход последнего импульса - к R-входу триггера генератора тактов, а выход нулевого импульса соединен с R-входом регистра мантиссы, единичные выходы регистра порядка и второго триггера подключены к управляющим входам коммутатора , кроме того, единичный выход второго триггера через третий элемент задержки подключен к третьему входу элемента ИЛИ, а через инвертор подключен ко второму входу второго элемента И, единичный выход первого триггера подключен к третьему входу второго и второму входу третьего элементов И, .а единичный выход третьего триггера - ко второму входу первого элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 364091, кл. Н 03 К 13/17, 22.12.70,

Мантисса

Порядок

Авторы

Даты

1981-06-23—Публикация

1979-09-28—Подача