1

Область использования изобретения - автоматика, измерительная и вычислительная техника.

Известны преобразователи аналоговых величин в код методом поразрядного уравновешивания, содержащие схему сравнения, первый вход которой соединен с источником преобразуемого напряжения, а второй - с выходом преобразователя кода в напряжение, в.ход которого подключен через регистр к выходу логического блока, управляющий вход которого соединен с первым выходом схемы сравнения, а входы - с выходами распределителя импульсов и входами первой схемы сборки.

Такое устройство характеризуется ограниченной скоростью преобразования, особенно при высокоточном преобразовании.

Цель изобретения - сокращение времени преобразования за счет того, что в зависимости от величины преобразуемого сигнала обеспечивается сокращение или пропуск некоторых тактов уравновещивания.

Сущность изобретения заключается в том, что в преобразователь введен блок сокращения тактов и сквозного перехода, причем он содержит дополнительно схемы «И, схемы сборки, триггеры, линии задержки, инверторы и выпрямитель, вход которого соединен со вторым выходом схемы сравнения, а выход через первую схему «И, второй вход которой через первый триггер подключен к выходу первой линии задержки и выходу первой схемы сборки, подключен ко входу второй схемы сборки, выход которой соединен с первым входом распределителя импульсов. Вход первого инвертора соединен с первым выходом схемы сравнения, а выход через вторую схему «И, второй вход которой подключен к нулевому выходу второго триггера, и третью

схему «И, второй вход которой соединен с выходом первой линии задержки, подключен ко входу второй схемы сборки, первый вход четвертой схемы «И соединен с первым выходом схемы сравнения, второй - с единичным выходом второго триггера, единичный вход которого соединен с выходом первой схемы сборки, а нулевой вход - с выходом третьей схемы сборки, входы которой подключены к выходам логического блока, а выход четвертой схемы «И через пятую с.хему «И, второй вход которой соединен с выходом первой линии задержки, соединен со входом второй схемы сборки, первый вход щестой схемы «И соединен с третьим выходом схемы сравнения, второй вход - с четвертым выходом схемы сравнения, а выход через второй инвертор и седьмую схему «И, второй вход которой соединен с выходом первой схемы сборки, подключен ко второму входу расиределителя импульсов и через восьмую схему «И, второй вход которой подключен к выходу второй линии задержки, вход которой соединен с выходом первой схемы сборки, подключен к третьему входу распределителя импульсов.

В данном преобразователе используется схема сравнения, которая в зависимости от соотношения компенсирующего напряжения UK преобразователя кода в напряжение (ПКН) и напряжения Ux источника преобразуемого сигнала обеспечивает выработку потенциальных сигналов на своем первом выходе, если напряжение UX,UK, выработку импульса на втором выходе в момент смены знака соотношения напряжений UK и U, выработку потенциальных сигналов на третьем выходе, если напряжение - А, и на четвертом, если напряжение + А- специальный распределитель импульсов, обеспечиваюш,ий помимо выработки последовательности распределенных во времени и пространстве импульсов ускоренную выработку очередного импульса или сквозного перехода к нахождению старшего разряда младшей группы по сигналам с блока сокращения тактов и сквозного перехода.

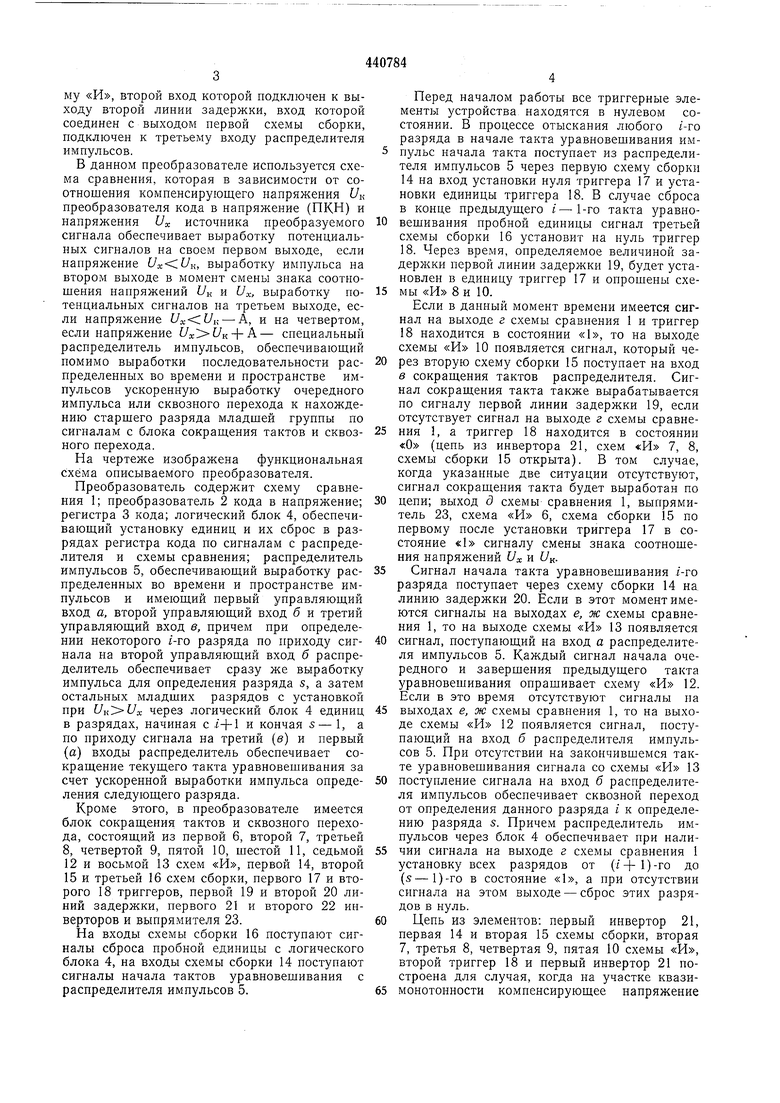

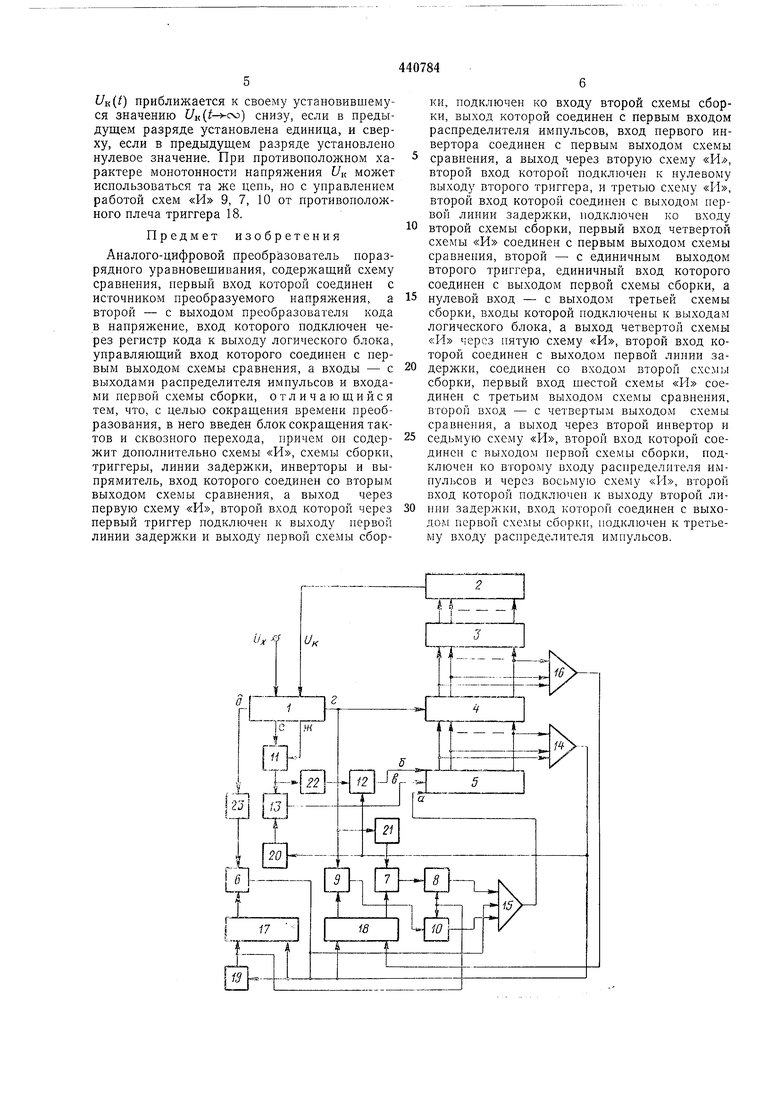

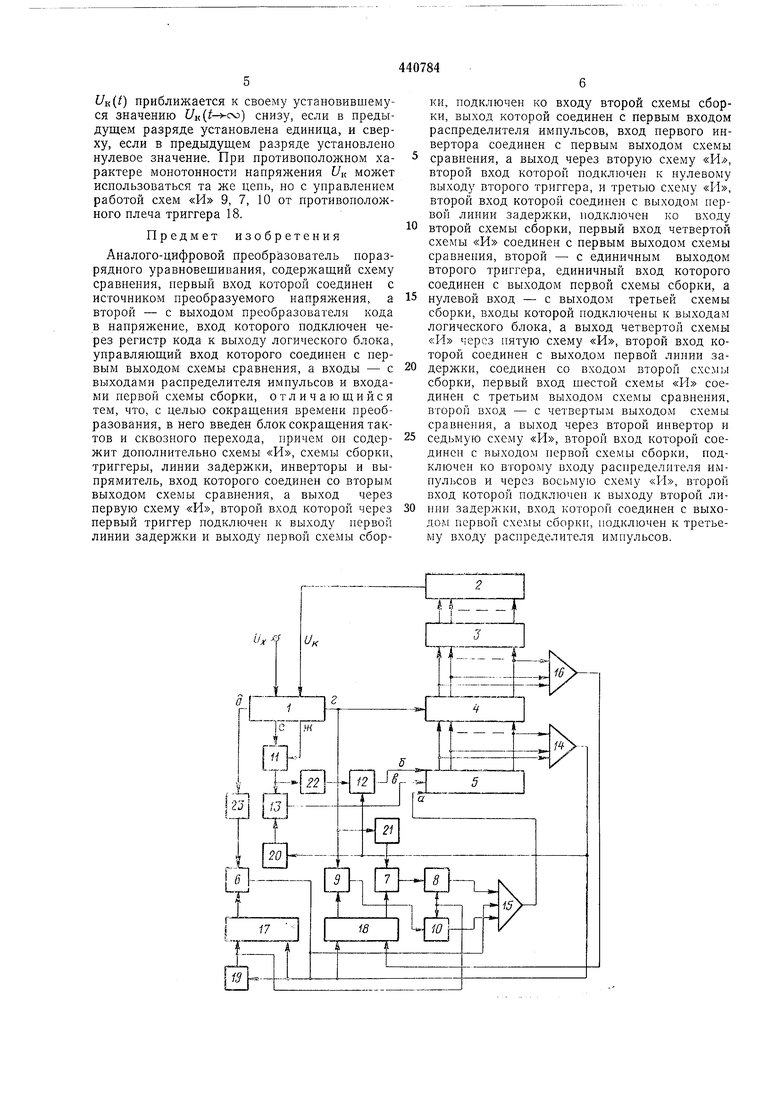

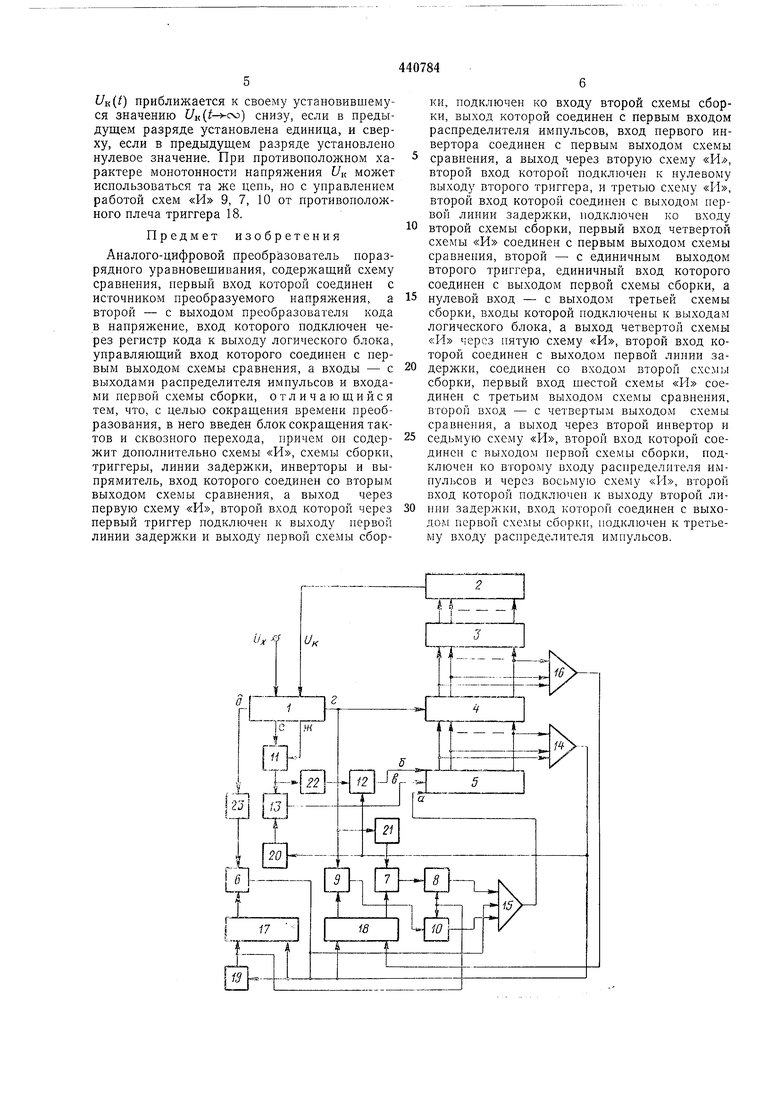

На чертеже изображена функциональная схема описываемого преобразователя.

Преобразователь содержит схему сравнения 1; преобразователь 2 кода в напряжение; регистра 3 кода; логический блок 4, обеспечивающий установку единиц и их сброс в разрядах регистра кода по сигналам с распределителя и схемы сравнения; распределитель импульсов 5, обеспечивающий выработку распределенных во времени и пространстве импульсов и имеющий первый управляющий вход а, второй управляющий вход б и третий управляющий вход в, причем при определении некоторого /-го разряда по приходу сигнала на второй управляющий вход б распределитель обеспечивает сразу же выработку импульса для определения разряда s, а затем остальных младших разрядов с установкой при через логический блок 4 единиц в разрядах, начиная с ,/+1 и кончая s- 1, а по приходу сигнала на третий (в) и первый (а) входы распределитель обеспечивает сокращение текущего такта уравновешивания за счет ускоренной выработки импульса определения следующего разряда.

Кроме этого, в преобразователе имеется блок сокращения тактов и сквозного перехода, состоящий из первой 6, второй 7, третьей 8, четвертой 9, пятой 10, шестой 11, седьмой 12 и восьмой 13 схем «И, первой 14, второй 15 и третьей 16 схем сборки, первого 17 и второго 18 триггеров, первой 19 и второй 20 линий задержки, первого 21 и второго 22 инверторов и выпрямителя 23.

На входы схемы сборки 16 поступают сигналы сброса пробной единицы с логического блока 4, на входы схемы сборки 14 поступают сигналы начала тактов уравновешивания с распределителя импульсов 5.

Перед началом работы все триггерные элементы устройства находятся в нулевом состоянии. В процессе отыскания любого /-го разряда в начале такта уравновешивания импульс начала такта поступает из распределителя импульсов 5 через первую схему сборки 14 на вход установки нуля триггера 17 и установки единицы триггера 18. В случае сброса в конце предыдущего /-1-го такта уравновешивания пробной единицы сигнал третьей схемы сборки 16 установит на нуль триггер 18. Через время, определяемое величиной задерл ки первой линии задержки 19, будет установлен в единицу триггер 17 и опрошены схемы «И 8 и 10.

Если в данный момент времени имеется сигнал на выходе г схемы сравнения 1 и триггер 18 находится в состоянии «1, то на выходе схемы «И 10 появляется сигнал, который через вторую схему сборки 15 поступает на вход в сокращения тактов распределителя. Сигнал сокращения такта также вырабатывается по сигналу первой линии задержки 19, если отсутствует сигнал на выходе г схемы сравнения 1, а триггер 18 находится в состоянии «О (цепь из инвертора 21, схем «И 7, 8, схемы сборки 15 открыта). В том случае, когда указанные две ситуации отсутствуют, сигнал сокращения такта будет выработан по

цепи; выход д схемы сравнения 1, выпрямитель 23, схема «И 6, схема сборки 15 по первому после установки триггера 17 в состояние «1 сигналу смены знака соотношения напряжений Их и UK.

Сигнал начала такта уравновешивания 1-го разряда поступает через схему сборки 14 на линию задержки 20. Если в этот момент имеются сигналы на выходах е, ж схемы сравнения 1, то на выходе схемы «И 13 появляется

сигнал, поступающий на вход а распределителя импульсов 5. Каждый сигнал начала очередного и завершения предыдущего такта уравновешивания опрашивает схему «И 12. Если в это время отсутствуют сигналы па

выходах е, ж схемы сравнения 1, то на выходе схемы «И 12 появляется сигнал, поступающий на вход б распределителя импульсов 5. При отсутствии на закончившемся такте уравновешивания сигнала со схемы «И 13

поступление сигнала на вход б распределителя импульсов обеспечивает сквозной переход от определения данного разряда i к определению разряда S. Причем распределитель импульсов через блок 4 обеспечивает при наличии сигнала на выходе г схемы сравнения I установку всех разрядов от (/+1)-го до (s-1)-го в состояние «1, а при отсутствии сигнала на этом выходе -сброс этих разрядов в нуль.

Цепь из элементов: первый инвертор 21, первая 14 и вторая 15 схемы сборки, вторая 7, третья 8, четвертая 9, пятая 10 схемы «И, второй триггер 18 и первый инвертор 21 построена для случая, когда на участке квазимонотонности компенсирующее напряжение

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код поразрядного уравновешивания с переменным временем определения отдельных разрядов | 1971 |

|

SU511693A2 |

| Преобразователь напряжения в код поразрядного кодирования | 1973 |

|

SU517999A1 |

| Многоканальное устройство для измерения температуры | 1984 |

|

SU1229599A1 |

| Уравновешивающая схема для аналогоцифрового преобразователя поразрядного уравновешивания | 1972 |

|

SU444319A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Устройство для измерения температуры | 1985 |

|

SU1315831A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1078608A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Система шахтной телесигнализации с дистанционным питанием | 1984 |

|

SU1243141A1 |

Авторы

Даты

1974-08-25—Публикация

1971-06-14—Подача