lii ю

ел

а

00

г

Изобретение относится к вычислительной технике и может быть использовано для преобразования напряжения код при построении цифровых прием- йых трактов систем управления и конт)ОЛЯ.

Целью изобретения является расширение области применения.

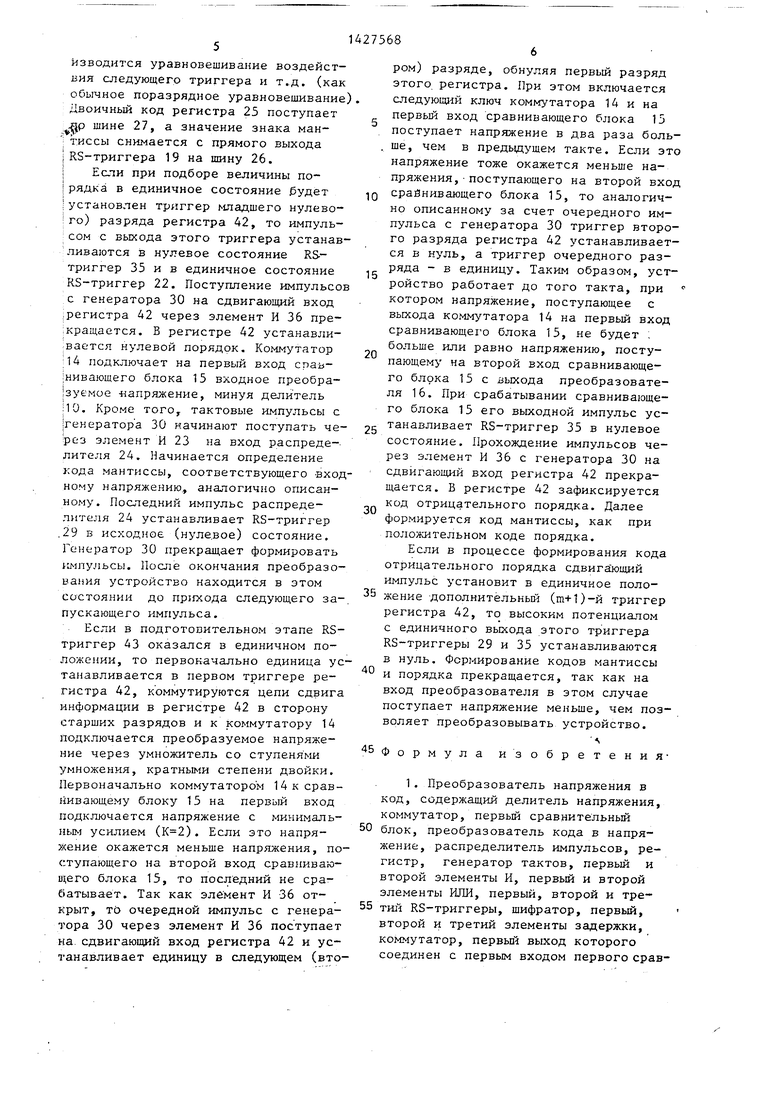

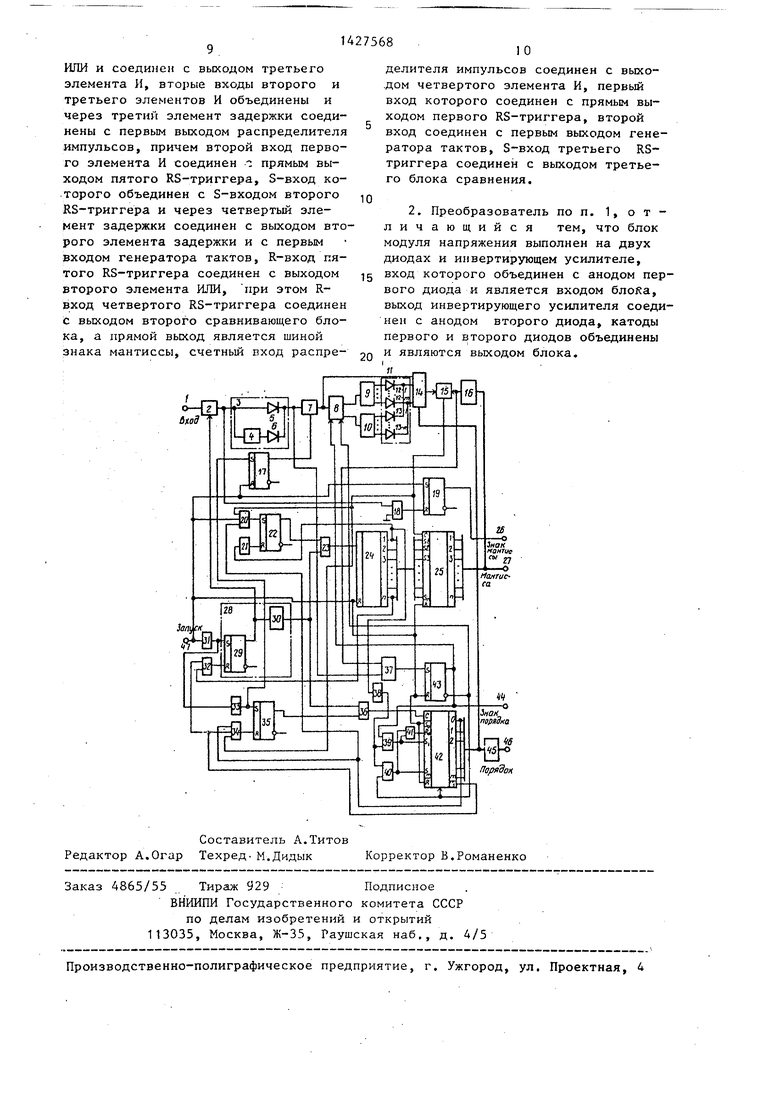

На чертеже приведена функциональная схема преобразователя.

Преобразователь содержит входную Шину 1 аналоговый ключ 2, блок 3 модуля напряжения, включающий инвертирующий усилитель 4 и диоды 5, 6 аналоговый ключ, аналоговый переклю- чатель 8, умножитель 9 напряжения со ступенями умножения, различающимися в два раза, делитель 10 напряжения с ступенями деления, различающимися в два раза, группу элементов ИЛИ 11, содержащую диоды 12 и 13, коммутатор ;1А, сравнивающий блок 15, преобразо- |ватель 16 кода в напряжение, RS- триггер 17, сравнивающий блок 18, RS-триггер 19, элемент ИЛИ.20, элемент 21 задержки, RS-триггер 22, элемент И 23, распределитель 24 импульсов, регистр 25, шину 26 знака мантиссы, шину 27 кода мантиссы, генератор 28 тактов, выполненный на RS- тригге)ре 29 и генераторе 30 импульсов, элемент 31 задержки, элемент ИЛИ 32, элемент 33 задержки, элемент ИЛИ 34, RS-триггер 35, элемент И 36, сравнивающий блок 37, элемент 38 задерж- ки, элемент И 39, элемент И 40, элемент ИЛИ 41, реверсивный сдвигающий регистр 42, RS-триггер 43, шину 44 знака порядка, шифратор 45, шину 46 кода порядка и шину 47 запуска.

Преобразователь работает следую- образом.

На входную шину 1 .подается преобразуемое напряжение. Импульс запуска, поступающий по шине 47, устанав- ливает RS-триггеры 19 и 22 в единичное состояние, распределитель 24, регистр 25 и RS-триггер 43 - в нулевое состояние, в реверсивном сдвигшощем регистре 42 нулевой разряд, вьссод в первой группе выходов устанавливается в единицу, а остальные - в нуль, что соответствует нулевому порядку кода числа. Высоким потенциалом с прямого выхода RS-триггера 22 .откры- вается элемент И 23. Задержанный элементом 31 на время переходных процессов в указанных узлах импульс за5

0

с c 35 40

45 50 55

пуска переводит RS-триггер 29 генератора 28 в единичное состояние. Высоким потенциалом с прямого выхода этого llS-триггера запускается генератор 30, и открывается аналоговый ключ 2. Преобразуемое напряжение с аналогового ключа 2 поступает на блок 3 и на сравнивающий блок 18. Если преобразуемое напряжение положительное, то срабатывает сравнивающий блок 18 и импульс с этого блока поступает на К-вход RS-триггера 19, устанавливая его в нулевое состояние (положительный знак мантиссы), а если преобразуемое напряжение отрицательное, то импульс на выходе блока сравнения 18 отсутствует и RS-триггер 19 остается в единичном состоянии (отрицатель- ньш знак мантиссы).

Импульс генератора 30 через элемент И 23 поступает на счетньй вход распределителя 24. С первого выхода распределителя 24 импульс устанавливает в старшем разряде регистра 25 единицу и, задержанный элементом 21, возвращает RS-триггер 22 в нулевое состояние, прекращая прохождение последующих импульсов генератора 30 через элемент И 23 на распределитель 24.

В соответствии с кодом мантиссы преобразователь 16 формирует напряжение, поступающее на сравнивающие блоки 15 и 37. Одновременно на вый вход сравнивающего блока 37 поступает преобразуемое напряжение с выхода блока 3. Если преобразуемое «апряжение будет меньше напряжения преобразователя 16, то на выходе сравнивающего блока 37 появляется импульс, который устанавливает RS- триггер 43 в единицу (отрицательный порядок числа). Высоким потенциалом с прямого выхода RS-триггера 43 откроется элемент И 39 и скоммутируют- ся цепи сдвига информации в реверсивном сдвигающем регистре 42 в сторону старших разрядов.

Если преобразуемое напряжение будет больше напряжения преобразователя 16, то на выходе сравнивающего блока 37 импульса нет, RS-триггер 43 остается в нулевом состоянии (положительный порядок). Откроется элемент И 40 и скоммутируются цепи сдвига информации в реверсивном сдвигающем регистре 42 в сторону младших разрядов. Кроме того, высоким потен- 1427568

циалом с прямого шш инверсного вы-коммутатора 14 и на первьш вход сравхода RS-триггера 43 входное преобра-кивающего блока 15 поступает напрязуемое напряжение с аналогового клю-жение в два раза больше,, чем в преча 7 через аналоговый переключательдыдущем такте. Если это напряжение 8 подключается к умножителю 9 или де- тоже меньше напряжения, поступающего

лителю 10. Задержанный элементом 38на второй вход сравнивающего блока

импульс с первого выхода распредели-15, то аналогично описанному за счет

теля 24 через элементы И 39 и 40 со-очередног о импульса с генератора 30

ответственно обнуляет нулевой разряд.jg (п1-1)-й разряд регистра 42 обнуляетреверсивного сдвигающего регистра 42ся, а (т-2)-й устанавливается в едии устанавливает единицу в первом илияичное состояние. Таким образом, устстаршем разряде этого регистра соот-ройство работает до того такта, при

ветственно (в зависимости от состоя-котором напряжение, поступающее с выния RS-триггера 43). К этому времени хода коммутатора 14 на первый вход

задержанньи- элементом 33 импульсом ссравнивающего блока 15, не будет

элемента 31 RS-триггеры 17 и 35 уста-больше или равно напряжению, постунавливаются в единичное состояние.пающему на второй вход сравнивающего

Высоким потенциалом с прямого выходаблока 15 с выхода преобразователя

RS-триггера 35 открывается элемент 16. При срабатывании сравнивающего

И 36, ас выхода RS-триггера 17 -блока 15 его выходной импульс устааналоговый ключ 7. Входное преобразу-навливает RS-триггер 35 в нулевое

емое напряжение через делитель 10 илисостояние, закрывая прохождение имумножитель 9 в зависимости от поло-пульсов -с генератора 30 на.сдвигаюжения RS-триггера 43 и аналогового25 Щий вход регистра 42.

переключателя 8 поступает на комм та-Регистр А2 остается в этом состоятор 14. В соответствии с кодом поряд-нии до поступления следующего импулька, определяемого состоянием ревер-са запуска. Состояние регистра 42 сосивного сдвигающего регистра 42, сответствует унитарному коду порядка

соответствующего входа коммутатора преобразуемого напряжения. Этот код

преобразуемое напряжение поступаетпреобразуется шифратором 45 в позина первьш вход сравнивающего бло-ционный двоичный код и поступает на

ка 15.шину 46. Знак порядка снимается с

Предположим, что KS-триггер 43 на-прямого выхода RS триггера 43 на шиходился в нулевом положении. Тогдану 4. Тот же импульс сравнивающего

аналоговый переключатель 8 подключает- блока 15 через элемент 20 ИЛИ уставходное напряжение к делителю 10.навливает RS-триггер 22 в состояние

В реверсивном сдвигающем регистреблока единицы. Прк этом импульсы с

42 первоначально единица будет уста-генератора 30 проходят через эле-%

новлена в старшем разряде, а следо-мент И 23 на счетный вход распреде- вательно, в коммутаторе 14 будет вклю- лителя 24 и начинается формирование

чей тот ключ, который подключает сту-кода мантиссы напряжения, поступаю-: пень делителя 10, соответствующую наи- щего через коммутатор 14 на первый

большему ослаблению напряжения источ-вход сравнир-Ющего блока 15.

ника преобразуемого напряжения. В ре-Первый из этих импульсов устанав зультате на первый вход сравнивающего ливает следующий триггер регистра 25

блока 15 поступает напряжение с наи-в единичное состояние (первьй был в

большим ослаблением. Если это напря-единичном состоянии), подключая к

жение меньше напряжения, поступающеговторому входу сравнивающего блока 15 на второй вход сравнивающего блока 15, дополнительное напряжение, равное пото последний не срабатывает. Так как ловине напряжения первого (старшего)

элемент И 36 открыт высоким потенциа-разряда преобразователя 16. Если сумлом с прямого вьпсода RS-триггера 35,ма этих напряжений больше напряжения,

то импульс с генератора 30 через эле-поступающего с выхода коммутатора 14

мент И 36 поступает на сдвигающийцд первый вход сравнивающего блока

вход регистра 42 и устанавливает еди-55 второй триггер регистра 25

ницу на следующем, (т-1)-м, разряде,устанавливается в исходное нулевое

обнуляя т-й разряд этого регистра.состояние, если нет, то он остается

При этом включается следующий ключg единичном. На след тощем такте про;-

изводи7 ся уравновешивание воздействия следующего триггера и т.д. (как обычное поразрядное уравновешивание) Двоичный код регистра 25 поступает Q шине 27, а значение знака мантиссы снимается с прямого выхода iRS-триггера 19 на шину 26. j Если при подборе величины по- i рядка в единичное состояние 0удет I установлен триггер младшего нулево- го) разряда регистра 42, то импуль- ;сом с выхода этого триггера устанавливаются в нулевое состояние RS- триггер 35 и в единичное состояние RS-триггер 22. Поступление импульсов с генератора 30 на сдвигающий вход ;регистра 42 через элемент И 36 пре- ;кра1цается. В регистре 42 устанавливается нулевой порядок. Коммутатор 114 подключает на первый вход сраъ- Ыивающего блока 15 входное преобра- зуемое напряжение, минуя делитель МО. Кроме того, тактовые импульсы с генератора 30 начинают поступать через элемент И 23 на вход распреде-- лителя 24. Начинается определение кода мантиссы, соответствующего -входному напряжению., аналогично описанному. Последний импульс распреде- ЛИТШ1Я 24 устанавливает RS-триггер .29 в исход)1ое (нуле.вое) состояние. Генератор 30 прекращает формировать и мпульсы. После окончания преобразования устройство находится в этом состоянии до прихода следующего запускающего импульса.

Если в подготовительном этапе RS- триггер 43 оказался в единичном положении, то первоначально единица устанавливается в первом триггере регистра 42, коммутируются цепи сдвига информации в регистре 42 в сторону старших разрядов и к коммутатору 14 подключается преобразуе -1ое напряжение через умножитель со ступенями умножения, кратными степени двойки. Первоначально коммутатором 14 к сравнивающему блоку 15 на первый вход подключается напряжение с минимальным усилием (). Если это напряжение окажется меньше напряжения, поступающего на второй вход сравнивающего блока 15, то последний не срабатывает. Так как элемент И 36 открыт, то очередной импульс с генератора 30 через элемент И 36 поступает на сдвигающий вход регистра 42 и устанавливает единицу в следующем (вто

5

0

ром) разряде, обнуляя первый разряд этого, регистра. При этом включается следующий ключ коммутатора 14 и на первьш вход сравнивающего блока 15 поступает напряжение в два раза больше, чем в предыдущем такте. Если это напряжение тоже окажется меньше напряжения, поступающего на второй вход сравнивающего блока 15, то аналогично описанному за счет очередного импульса с генератора 30 триггер второго разряда регистра 42 устанавливается в нуль, а триггер очередного разряда - в единицу. Таким образом, устройство работает до того такта, при котором напряжение, поступающее с выхода коммутатора 14 на первый вход сравнивающего блока 15, не будет ; больше или равно напряжению, поступающему на второй вход сравнивающего блока 15 с выхода преобразователя 16. При срабатывании сравнивающего блока 15 его выходной импульс устанавливает RS-триггер 35 в нулевое состояние. Прохождение импульсов через элемент И 36 с генератора 30 на сдвигающий вход регистра 42 прекращается. В регистре 42 зафиксируется код отрицательного порядка. Далее формируется код мантиссы, как при положительном коде порядка.

Если в процессе формирования кода отрицательного порядка сдвиггОоший импульс установит в единичное поло- 5 жение дополнительный (т+1)-й триггер регистра 42, то высоким потенциалом с единичного выхода этого триггера RS-триггеры 29 и 35 устанавливаются в нуль. Формирование кодов мантиссы

5

0

0

И порядка прекращается, так как на

вход преобразователя в этом случае поступает напряжение меньше, чем позволяет преобразовывать устройство.

«, Формула изобретения1. Преобразователь напряжения в код, содержащий делитель напряжения, коммутатор, первьй сравнительный блок, преобразователь кода в напряжение, распределитель импульсов, регистр, генератор тактов, первый и второй элементы И, первый и второй элементы ИЛИ, первый, второй и тре- SS ТШ1 RS-триггеры, шифратор, первый, второй и третий элементы задержки, коммутатор, первьш выход которого соединен с первым входом первого срав50

нивающего блока, второй вход которого соединён с выходом преобразователя кода в напряжение, входы которого соединены с соответствующими выходами регистра и являются шиной кода мантиссы, выход первого сравнивающего блока соединен с входом разрешения записи регистра, информационные входы которого соединены с соответствующими выходами распределителя импульсов, S-вход первого RS-триггера соединен с выходом первого элемента ИЛИ, R-вход соединен с выходом первого элемента задержки, вход которого соединен с первым выходом распределителя импульсов, первый вход первого элемента ИЛИ соединен с выходом первого сравнивающего блока, второй вход является шиной запуска, первый выход генератора тактов соединен с первым входом первого элемента И, выходы шифратора являются шиной кода порядка, а входы объединены с соответствующими управляющими входами коммутатора, отличающийся тем, что, с целью расширения области применения за счет преобразования напряжений различной полярности и упрощения вида формируемого кода, в него введены второй и третий сравнивающие блоки, четвертый и пятый RS-триггеры реверсивный сдвигающий регистр, третий и четвертый элементы ИЛИ, третий и четвертый элемент И, четвертьй элемент задержки, аналоговый переключа- тель, умножитель напряжения, группа элементов ИЛИ, блок модуля напряжения, два аналоговых ключа, информационный вход первого аналогового ключа является входной шиной, управляющий вход соединен с вторым выходом генератора тактов, а выход первого аналогового ключа подключен к входу блока модуля напряжения и к первому входу второго сравнивающего блока, второй вход которого является общей шиной, выход блока модуля напряжения подключен к информационному входу . второго аналогового ключа и первому входу третьего сравнивающего блока, к второму входу которого подключен выход преобразователя кода в напряжение, управляющий вход второго ана логового ключа подключен к прямому выходу второго RS-триггера, выход второго аналогового ключа подключен к первому входу коммутатора и к информационному входу аналогового переключателя, первый и второй управляющие входы которого подключены соответственно к прямому и инверсному выходам третьего RS-триггера, первый

выход аналогового переключателя подключен к входу умножителя напряжения, а второй - к входу делителя напряжения, соответствующие выходы умножителя и делителя напряжений через rf уппу элементов ИЛИ подключены к соответствующим вторым входам коммутатора, управляющие входы которого подключены к соответствующим выходам

группы выходов реверсивного сдвигающего регистра, первый выход группы выходов которого подключен к третьему входу первого элемента ИЛИ и к первому входу второго элемента ИЛИ, вы

ход реверсивного сдвигающего регистра

подключен к второму входу второго элемента ИЛИ и к первому входу третьего элемента ИЛИ, к второму входу коюро- го подключен последний выход распреде- лителя импульсов, третий вход второго элемента ИЛИ соединен с выходом первого сравнивающего блока, управляющий вход сдвига в сторону старших разрядов реверсивного сдвигающего регистра

объединен с первым входом второго элемента И и соединен с прямым выходом третьего RS-триггера и является шиной знака порядка, управляющий вход сдвига в сторону младших разрядов реверсивного сдвигающего регистра

объединен с перзым входом третьего элемента И и соединен с инверсным выходом третьс-.го RS-триггера, вход сдвига реверсивного сдвигающего регистра соединен с выходом первого

элемента И, первый, установочный вход реверсивного сдвигающего регистра соединен с выходом четвертого элемента ИЛИ, второй установочный вход и первый информационньм вход реверсивного

сдвигающего регистра, R-вход третьего RS-триггера, установочные входы распределителя импульсов и регистра, вход второго элемента задержки, R- вход второго RS-триггера, S-вход

четвертого RS-триггера объединены и являются шиной запуска, второй информационный вход реверсивного сдвигающего регистра объединен с первым входом.четвертого элемента ИЛИ и сое-

динен с выходом второго элемента И, третий информационный вход реверсивного сдвигающего регистра объединен с вторым входом четвертого элемента

ИЛИ и соединен с выходом третьего элемента И, вторые входы второго и третьего элементов И объединены и через третий элемент задержки соединены с первым выходом распределителя импульсов, причем второй вход первого элемента И соединен : прямым выходом пятого RS-триггера, S-вход которого объединен с S-входом второго RS-триггера и через четвертый элемент задержки соединен с выходом второго элемента задержки и с первым входом генератора тактов, R-вход пятого RS-триггера соединен с выходом второго элемента ИЛИ, при этом R- вход четвертого RS-триггера соединен с выходом второго сравнивающего блока, а прямой выход является шиной знака мантиссы, счетный вход распре0

5

0

делителя импульсов соединен с выходом четвертого элемента И, первый вход которого соединен с прямым выходом первого RS-триггера, второй вход соединен с первым выходом генератора тактов, S-вход третьего RS- триггера соединен с выходом третьего блока сравнения.

2. Преобразователь по п. 1, отличающийся тем, что блок модуля напряжения выполнен на двух диодах и инвертирующем усилителе, вход которого объединен с анодом первого диода и является входом блока, выход инвертирующего усилителя соединен с анодом второго диода, катоды первого и второго диодов объединены

и являются выходом блока,

I гг

г

ГП W

rrfr

Порядок

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Преобразователь напряжения в код | 1980 |

|

SU924853A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

Изобретение относится к вычислительной технике и может быть использовано для преобразования напряжения в код в цифровых трактах систем управления и контроля. Изобретение позволяет расширить функшюнапь- ные возможности. Это достигается тем, что в преобразователь, содержащий делитель напряжения, коммутатор, сравнивающий блок, преобразователь кода в напряжение, распределитель импульсов, регистр, генератор тактов, элементы И, элементы ИЛИ, триггеры, шифратор, элементы задержки, введены сравнивающие блоки, триггеры, реверсивный сдвигающий регистр, три элемента ИЛИ, элементы И, элемент задержки, аналоговые ключи, аналоговый переключатель, умножитель напряжения, блок модуля напряжения и группа эле- ментов ИЛИ. 1 з.п. ф-лы, 1 ил. §

| I БИБЛИОТЕКА | 0 |

|

SU364091A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1987-01-21—Подача