(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1978 |

|

SU748863A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU953721A2 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790285A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифроаналоговый преобразователь | 1981 |

|

SU1005298A1 |

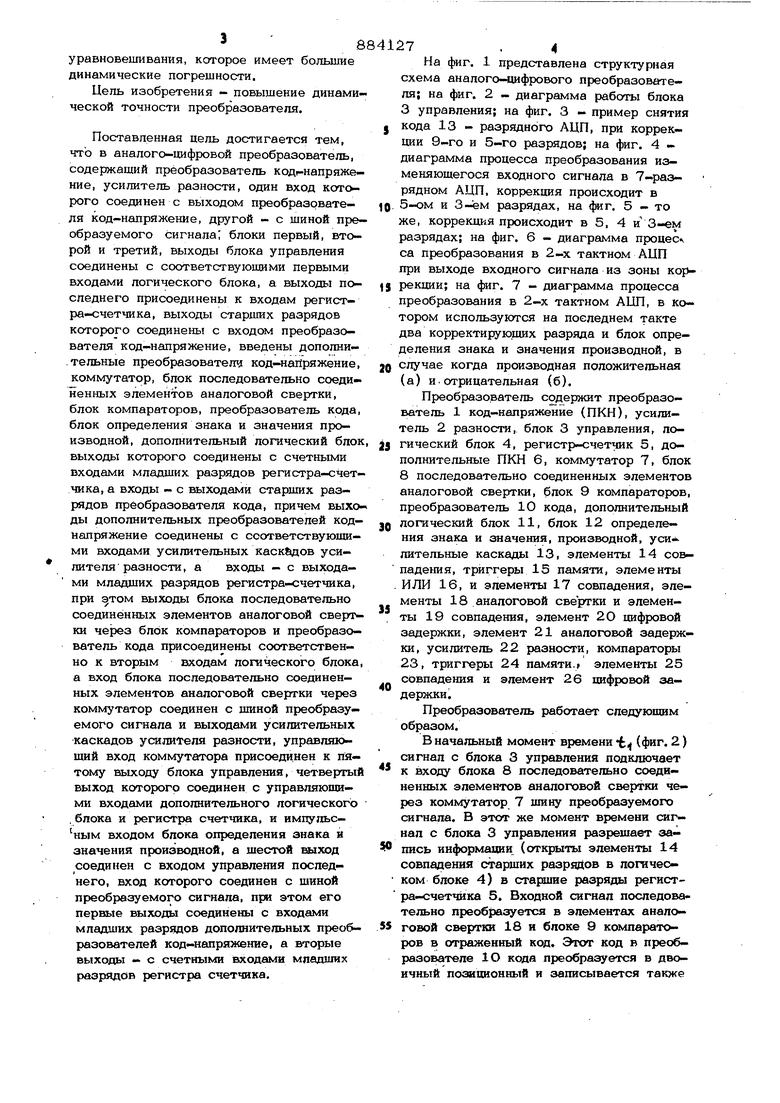

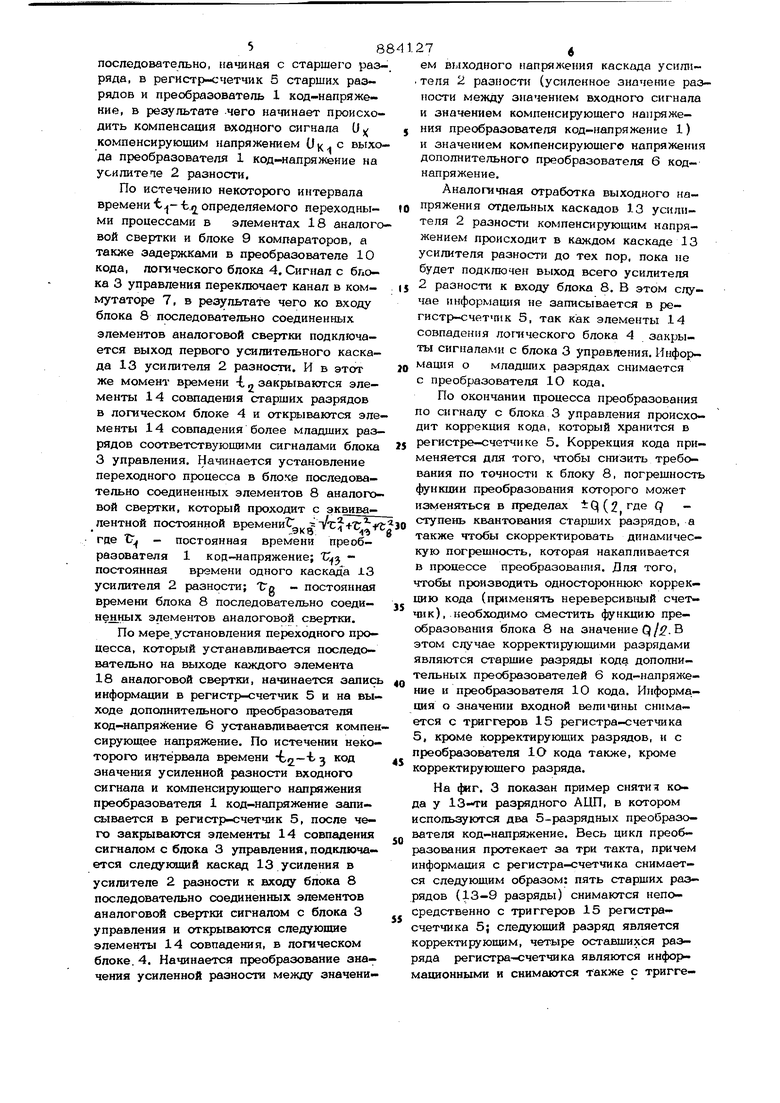

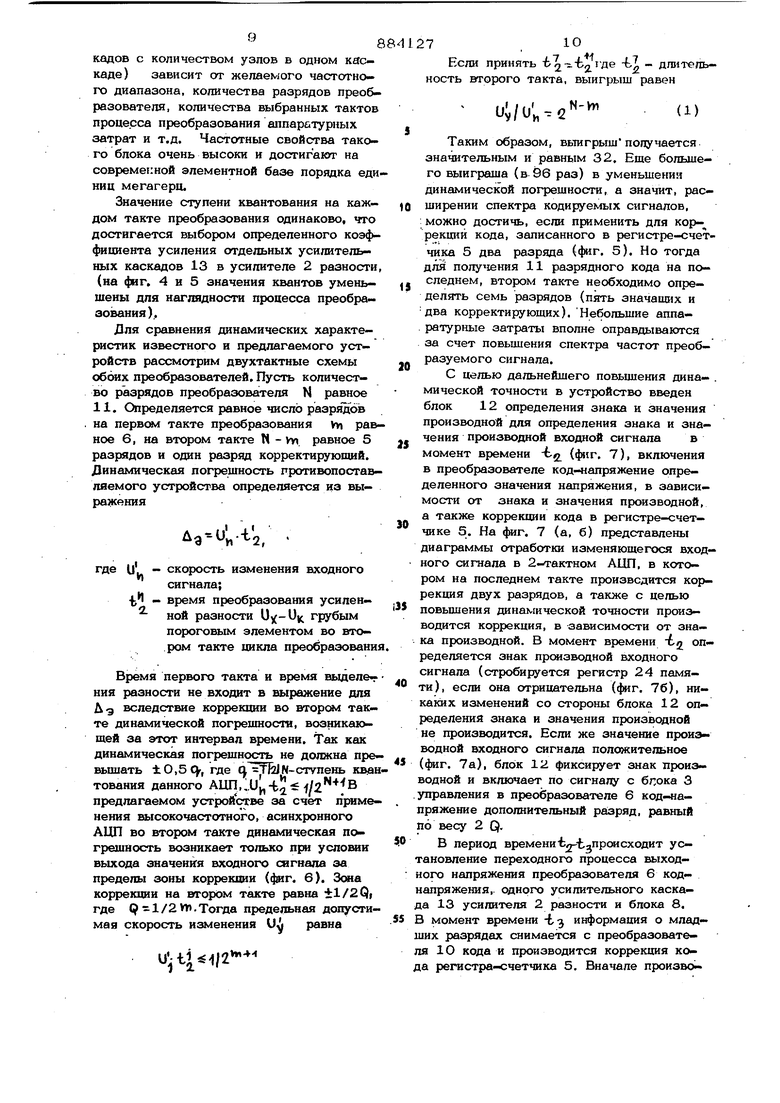

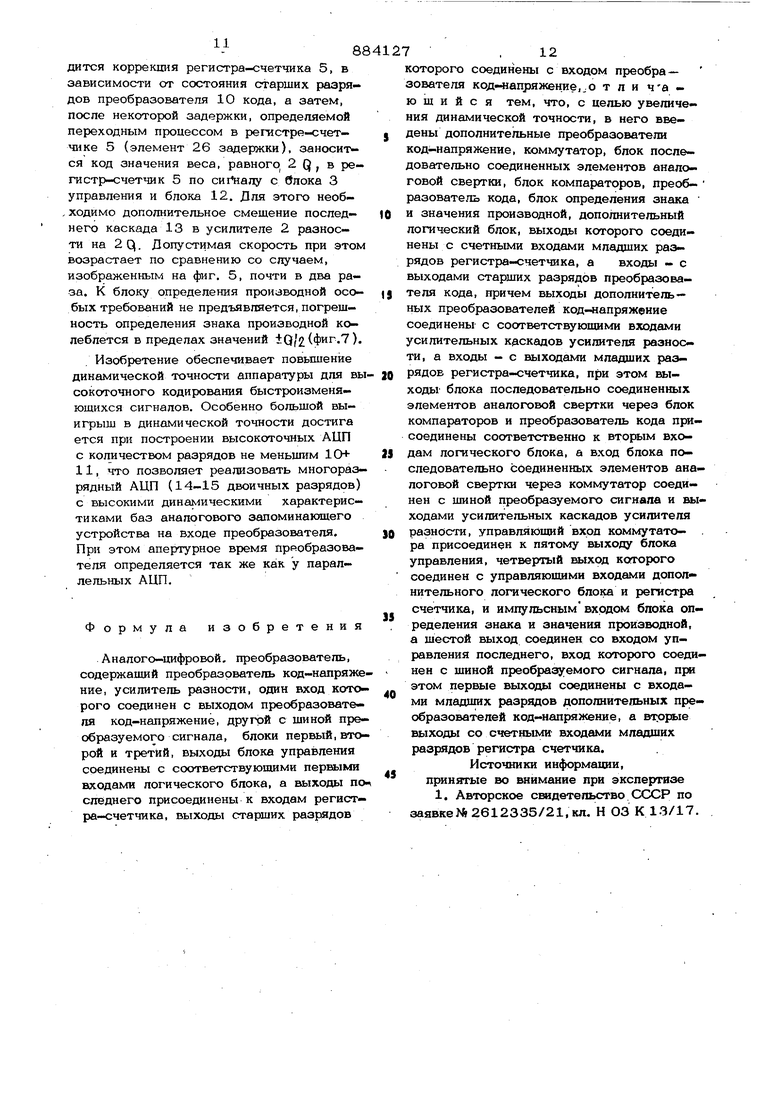

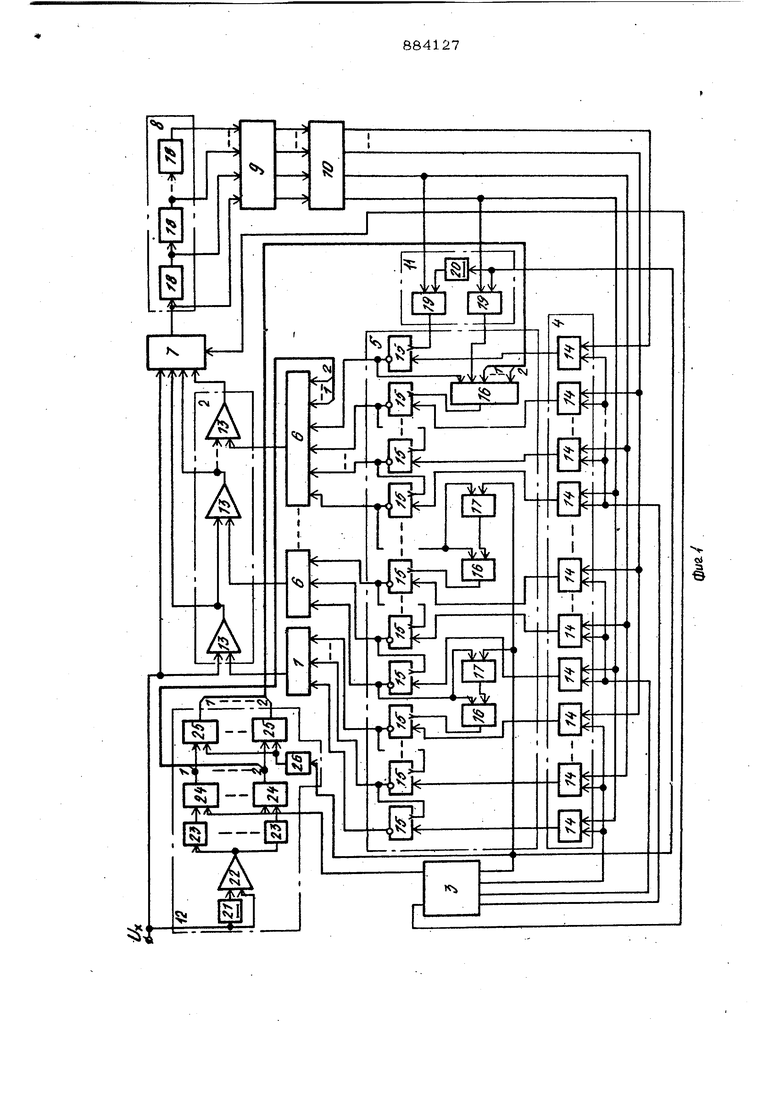

Изобретение относится к измерительной -и вычислительной технике и может быть использовано для преобразования аналоговых сигналов в код. Известен аналого-цифровой преобразователь, содержащий два пороговых элемен та, преобразователь код-напряжение, регистр, логический блок, распределитель импульсов, элемент запрета и генератор импульсов, выход которого посредством элемента запрета соединен с входом раопределителя импульсов, выходы последнего через логический блок и регистр соединены с входами преобразователя коднапряжение, причем выход преобразователя код-напряжение присоединен к соответствующим входам пороговых элементов, усилитель разности, переключающий блок, триггер, дополнительный преобразователь код-напряжение, регистр-счетчик, дополни тельный логический блок, причем входы усилителя разности присоедине1Па1 соответ ственно к выходу дополнительного преоб разователя код-напряжение и входу одноГО из пороговых элементов, соединенному с шиной преобразуемого сигнала, а выход усилителя разности присоединен к второму входу другого первого элемента, выходы пороговых элементов через переключающий блок, управляющие входы которого соединены с «ыходами триггера, вход которого подключен к выходу распределителя импульсов, присоединены к входу логического блока, один из выходов триггера, соединен с управляющим входом элемента запрета и входом дополнительного логического блока, другие входы последнего присоединены к входам распр делителя импульсов, а выхода регистра через дополнительный логический блок и регистр-счетч11К соединены с входами дополнительного преобразователя код-напряжение i. Однако известный преобразователь обладает низкими динамическими свойствами, так как преобразование в каждом такте происходит по методу поразрядного уравновешивания, которое имеет большие динамические погрешности. Цель изобретения - повышение динамической точности преобразователя. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержаший преобразователь кодг-напряжение, усилитель разности, один вход которого соединен с выходом преобразователя код-напряжение, другой - с шиной преобразуемого сигнала; блоки первый, второй и третий, выходы блока управления соединены с соответствующими первыми входами логического блока, а выходы последнего присоединены к входам регистра-счетчика, выходы старших разрядов которого соединены с входом преобразователя код-напряжение, введены дополни. тельные преобразователе код-напряжение, коммутатор, блок последовательно соединенных элементов аналоговой свертки, блок компараторов, преобразователь кода, блок определения знака и значения производной, дополнительный логический блок выходы которого соединены с счетными входами младших разрядов регистра-счетчика, а входы - с выходами старших разрядов преобразователя кода, причем выхо ды дополнительных преобразователей коднапряжение соединены с соответствующими входами усилительных каскйдов усилителя разности, а входы - с выходами младших разрядов регистра-счетчика, при том выходы блока последовательно соединенных элементов аналоговой свертки через блок компараторов и преобразователь кода присоединены соответственно к вторым входам логического блока а вход блока последовательно соединенных элементов аналоговой свертки через коммутатор соединен с шиной преобразуемого сигнала и выходами усилительных каскадов усилителя разности, управляющий вход коммутатора присоединен к пятому выходу блока управления, четвертый выход которого соединен с управляющими входами дополнительного логического ,блока и регистра счетчика, и импупьс- ным входом блока определения знака и значения производной, а шестой выход соединен с входом управления последнего, вход которого соединен с щиной преобразуемого сигнала, при этом его первые выходы соединены с входами младших разрадов дополнительных преобразователей код-напряжение, а вторые выходы - с счетными входами мпадших разрядов регистра счетчика. На фиг. 1 представлена структурная схема аналого-цифрового преобразователя; на фиг. 2 - диаграмма работы блока 3 управления; на фиг. 3 - пример снятия кода 13 - разрядного АЦП, при коррекции 9-го и 5-го разрядов; на фиг. 4 диаграмма процесса преобразования изменяющегося входного сигнала в 7-разрядном АЦП, коррекция происходит в 5-ом и 3-ем разрядах, на фиг. 5 - то же, коррекция происходит в 5, 4 и 3-ем разрядах; на фиг. 6 - диаграмма процес, са преобразования в 2-х тактном АЦП при выходе входного сигнала из зоны кор рекции; на фиг. 7 - диаграмма процесса преобразования в 2-х тактном АЦП, в котором используются на последнем такте два корректирующих разряда и блок определения знака и значения производной, в случае когда производная положительная (а) и отрицательная (б). Преобразователь содержит преобразователь 1 код-напряжение (ПКН), усилитель 2 разности, блок 3 управления, логический блок 4, регистр-счетчик 5, дополнительные ПКН 6, коммутатор 7, блок 8 последовательно соединенных элементов аналоговой свертки, блок 9 компараторов, преобразователь 10 кода, дополнительный логический блок 11, блок 12 определения знака и значения, производной, уси лительные каскады 13, элементы 14 совпадения, триггеры 15 памяти, элементы ИЛИ 16, и элементы 17 совпадения, элементы 18 аналоговой свертки и элементы 19 совпадения, элемент 2О цифровой задержки, элемент 21 аналоговой задержки, усилитель 22 разности, компараторы 23, триггеры 24 памяти.; элементы 25 совпадения и элемент 26 цифровой задержки. Преобразователь работает следующим образом. В начальный момент времени -t (фиг. 2) сигнал с блока 3 управления подключает к входу блока 8 последовательно соединенных элементов аналоговой свертки через коммутатор 7 шину преобразуемого сигнала. В этот же момент времени сиг нал с блока 3 управления разрешает запись информации (открыты элементы 14 совпадения старших разрядов в логическом блоке 4) в старщие разряды регистра-счетчика 5. Входной сигнал последовательно преобразуется в элементах анало- ГОБОЙ свертки 18 и блоке 9 компараторов в отраженный код. Этот код в преобразователе 1О кода преобразуется в двоичный позиционный и записывается также 58 последовательно, начиная с старшего раз ряда, в регистр-счетчик 5 старших раэ радов и преобразователь 1 код-напряжение, в результате чего начинает происхо дить компенсация входного сигнала О компенсирующим напряжением О.с выхо да преобразователя 1 код-напряжение на усилитепе 2 разности. По истечению некоторого интервала времени .,ji определяемого переходными процессами в элементах 18 аналого вой свертки и блоке 9 компараторов, а также задержками в преобразователе 10 кода, логического блока 4, Сигнал с бпока 3 управления переключает канал в коммутаторе 7, в результате чего ко входу блока 8 последовательно соединенных элементов аналоговой свертки подключается выход первого усилительного каскада 13 усилителя 2 разности, И в этот же момент времени -(, п закрываются элементы 14 совпадения старших разрядов в логическом блоке 4 и открываются эле менты 14 совпадения более младших раз рядов соответствуюЕШМи сигналами блока 3 управления. Начинается установление переходного процесса в блоке последовательно соединенных элементов 8 аналого вой свертки, который проходит с эквиваленткой постоян1ной времени) V-cJ+tr -K где Т/ - постоянная времени преобразователя 1 код-напряжение; Т постоянная времени одного каскада 13 усилителя 2 разности; ТГп - постоянная времени блока 8 последовательно соеди- элементов аналоговой свертки. По мере установления переходного процесса, который устанавливается последовательно на выходе каждого элемента 18 аналоговой свертки, начинается запис информации в регистр-счетчик 5 и на вы ходе дополнительного преобразователя код-напряжение 6 устанавливается компе сирующее напряжение. По истечении некоторого интервала времени 4-2- 3 значения усиленной разности входного сигнала и компенсирующего напряжения преобразователя 1 код-напряжение записывается в регистр-счетчик 5, после чего закрываются элементы 14 совпадения сигналом с блока 3 управления, подключается следующий каскад 13 усиления в усилителе 2 разности к входу блока 8 последовательно соединенных элементов аналоговой свертки сигналом с блока 3 управления и открываются следующие элементы 14 совпадения, в логическом блоке. 4. Начинается преобразование значения усиленной разности между значени276ем выходного напряжения каскада усилн. теля 2 разности (усиленное значение разности между значением входного сигнала и значением компенсирующего напряжения преобразователя код-напряжение 1) и значением компенсирующего напряжения дополнительного преобразователя 6 коднапряжение. Аналогичная отработка выходного напряжения отдельных каскадов 13 усилителя 2 разности компенсирующим напряжением происходит в каждом каскаде 13 усилителя разности до тех пор, пока не будет подключен выход всего усилителя 2 разности к входу блока 8. В этом случае информация не записывается в регистр-счетП1К 5, так как элементы 14 совпадения логического блока 4 закрыты сигналами с блока 3 управления. Информация о младших разрядах снимается с преобразователя 1О кода. По окончании процесса преобразования по сигналу с блока 3 управления происходит коррекция кода, который хранится в регистре-счетчике 5, Коррекция кода применяется для того, чтобы снизить требования по точности к блоку 8, погрешность функции преобразования которого может изменяться в пределах i G| ( 2, гДе Q ступень квантования старших разрядов, а также чтобы скорректировать динамическую погрешность, которая накапливается в процессе преобразовав я. Для того, чтобы производить одностороннюю коррекцию кода (пр41менять нереверсивный счетчик), лгеобходимо сместить функцию преобразования блока 8 на значение Q /j. В этом корректирующими разрядами являются старшие разряды кода дополнительных преобразователей 6 код-напряи ение и преобразователя 10 кода. Информация о значении входной велншны снимается с триггеров 15 регистра-счетчика 5, кроме корректирующих разрядов, и с преобразователя Ю кода также, кроме корректирующего разряда, На фиг, 3 показан пример снятия кода у 13--ГИ разрядного АЦП, в котором используются два 5-разрядных преобразователя код-напряжение. Весь цикл преобразования протекает за три такта, причем информация с регистра-счетчика снимается следующим образом: пять старших разрядов (13-9 разряды) снимаются непосредственно с триггеров 15 регистрасчетчика 5; следующий разряд является корректирующим, четыре оставшихся разряда регистра-счетчика являются инфо1 мационными и снимаются также с триггеов 15 регистра-счетчика 5, младшие азряды снимаются с преобразователя 10 ода, кроме его старшего разряда, котоый является корректирующим для более тарших разрядов.

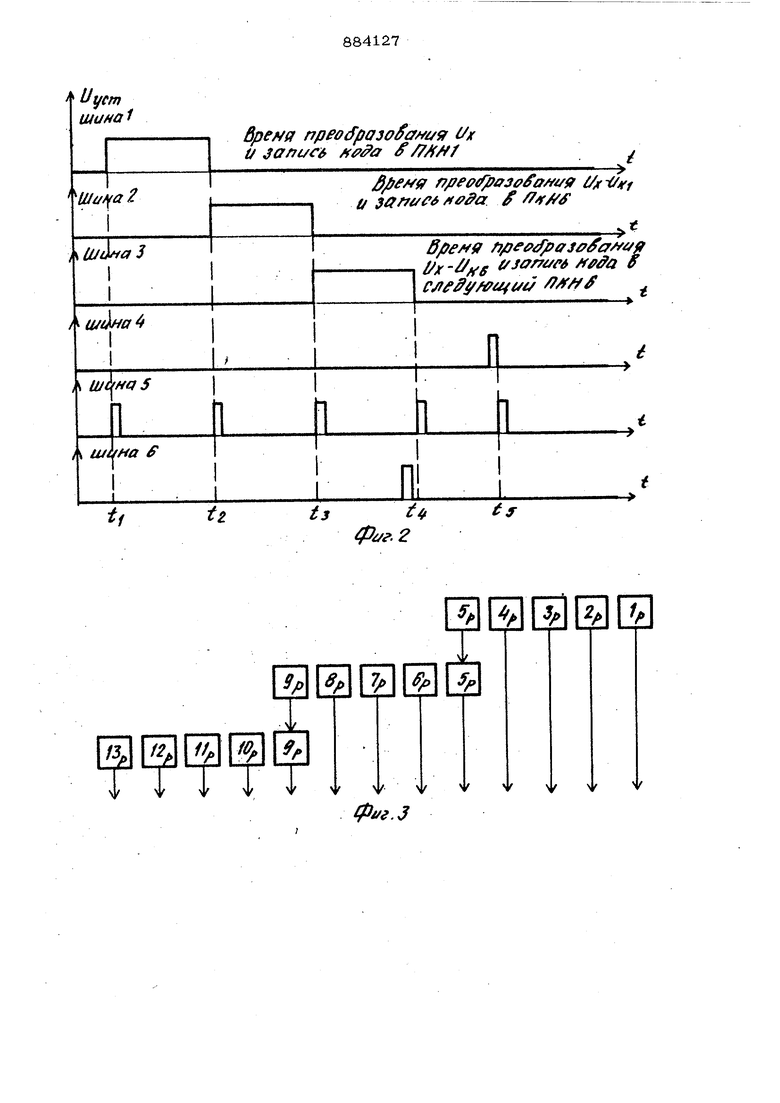

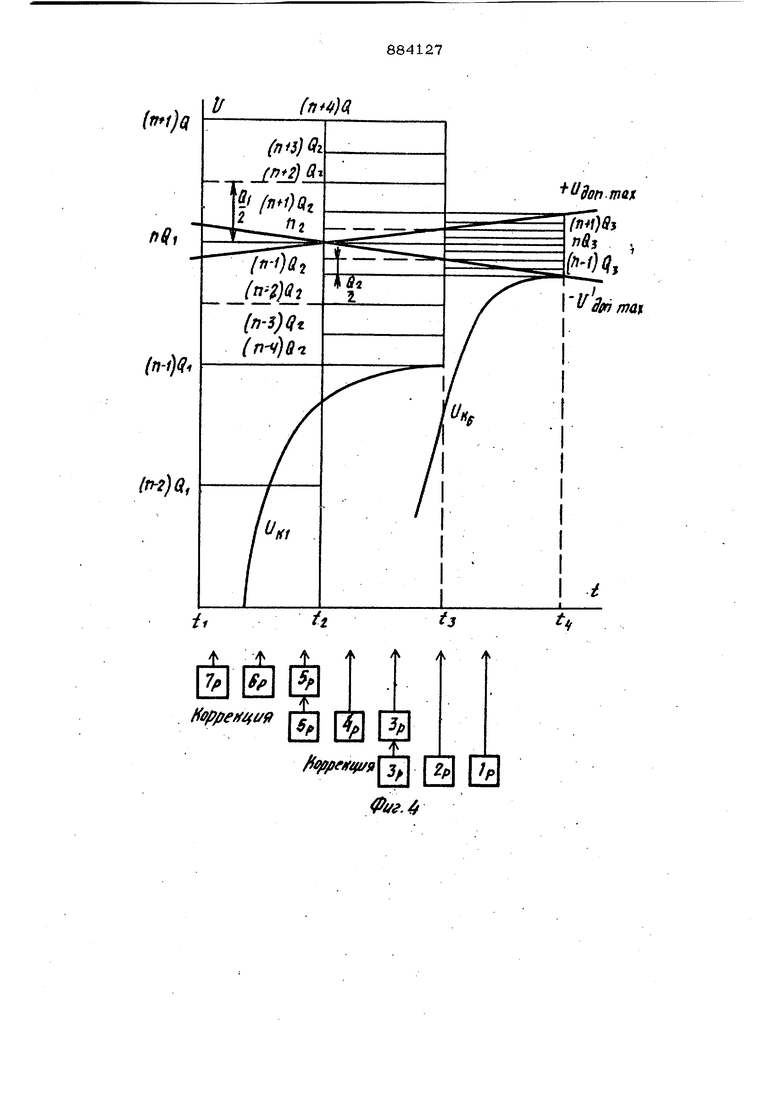

На фиг. 4 изображена диaгpa Iмa опейепения кода значений входного сигнаа, имеющего положительную и отрицательную производную. Процесс преобразования ротекает в три такта, причем на каждом акте определяются три разряда. На втором и третьем тактах старшие разряы являются корректирующими, а не информационными. Таким образом, выходной код-семиразрядный, двоичный. На первом такте fc/| -fca определяются три старших разряда и одновременно начинает устанавливаться напряжение на выходе первого п образователя код-напряжение Uj.B момент 4-2 информация о fpe старших разрядах полностью записана в регистр-счетчик 5, и схемы 14 совпадения этих разрядов в логическом блоке 4 закрываются а открываются следующие схемы совпадения. Во втором такте Ь -ЬзПротекает переходный процесс в каскаде усилителя 2 разности и блоке 8, и, одновременно, по мере определения разрядов, информа - ция о их значении записывается в ре - гастр-счетчик 5, и значит, и в преобразователь 6 код-напряжение, т.е. происходит установление компенсируюШего напряжения UK.

В момент времени -Ь т закрываются элементы 14 совпадения в логическом блоке 4 и через некоторое время происходит установление переходного процесса в последнем усилительном каЬкаде 13 усилителя 2 разности и блоке 8 и И1 формацию о младших разрядах можно снимать с преобразователя 10 кода (кроме корректирующего разряда) в момент времени t., В этот же момент времени производится коррекция кода в старших разрядах. На фиг. 4 показаны максимально допустимые значения скорости изменения входного сигнала при отрицательной и положительной производных. При отртцатель- ной производной .входного сигнала коррекция не производится. При положительной производной производится коррекция как старших, так и более младших -разрядов, так как значение входной величины на BTOpovi такте пересекает значение кванта hQ старших разрядов, а код регистрасчетчика 5 соответствует (Vt-1) Q,f -значению кванта. Это видно по установлению компенсирующего напряжения U).. На третьем такте значение входной величины также больше значения кванта И G) а код регистра-счетчика 5 соответствует (1 -1) Q значению кванта. Поэтому по сигналу с блока 3 управления через элементы 17 совпадения регистра-счетчика 5 происходит коррекция кода в старших разрядах (добавляется единица) и через элемент 19 совпадения в дополнительном логическом блоке в более млад- щих разрядах (также добавляется единица) регистра-счетчика 5. Корректируется не только динамическая погрешность, а и другие виды погрешностей, т.е. сумма статической и динамической погрешностей, что позволяет повысить частотные свойства блока 8 за счет использования грубых узлов элементов аналоговой свертки, а эначит более высокочастотных.

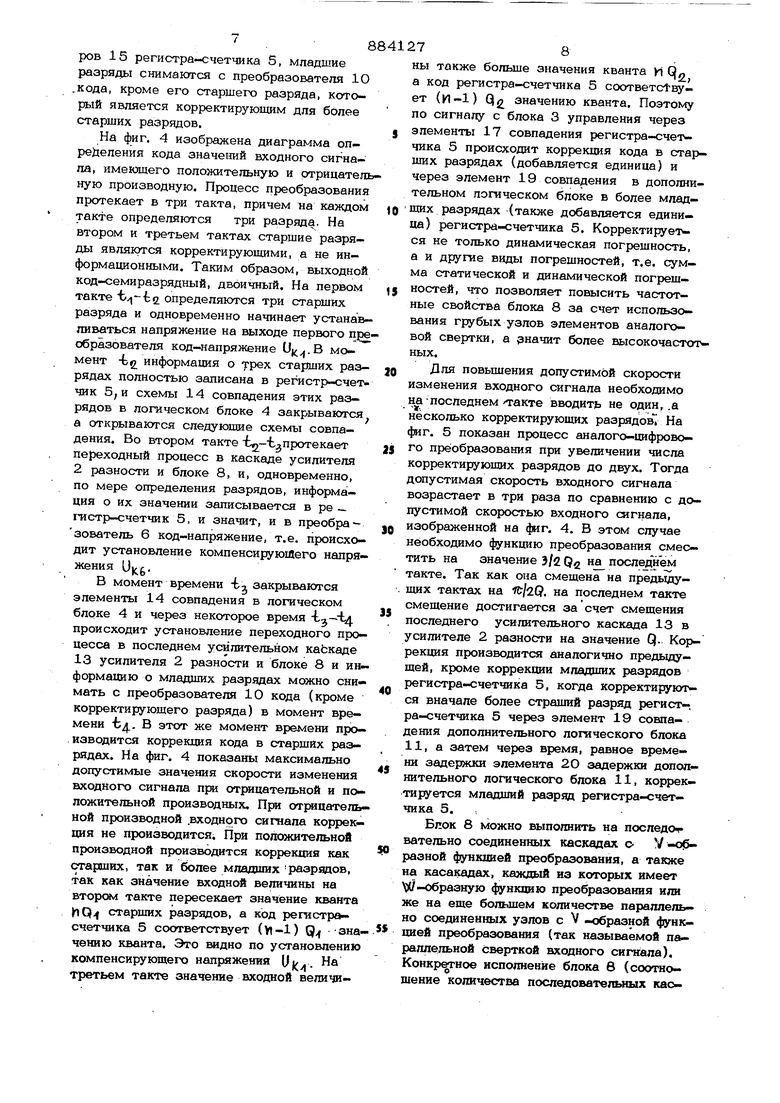

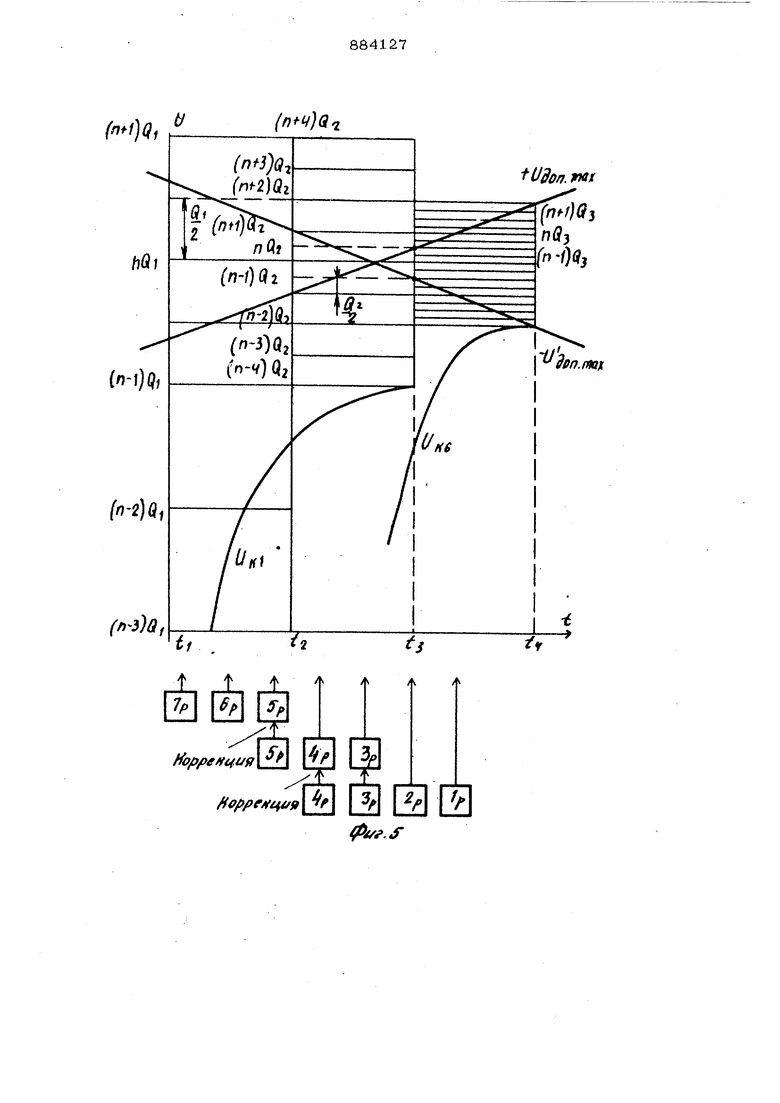

Для повьш1ения допустимой скорости изменения входного сигнала необходимо на -последнем -такте вводить не один, .а несколько корректирующих разрядов7 На фиг. 5 показан процесс аналого-цифрового преобразования при увеличении числа корректирующих разрядов до двух. Тогда допустимая скорость входного сигнала возрастает в три раза по сравнению с допустимой скоростью входного сигнала, изображенной на фиг. 4. В этом случае необходимо функцию преобразования сместить на значение Э/2 Q «. последи такте. Так как она смещена на предыду. щих тактах на Л/2(. на последнем такте смещение достигается за счет смещения последнего усилительного каскада 13 в усилителе 2 разности на значение Q. Коррекция производится аналогично предыдущей, кроме коррекции младших разрядов регистра-счетчика 5, когда корректируются вначале более страший разряд регист-, ра-счетчика 5 через элемент 19 совпадения дополнительного логического блока 11, а затем через время, равное времени задержки элемента 2 О задержки дополнительного логического блока 11, корректируется младший разряп регистра-счетчика 5.

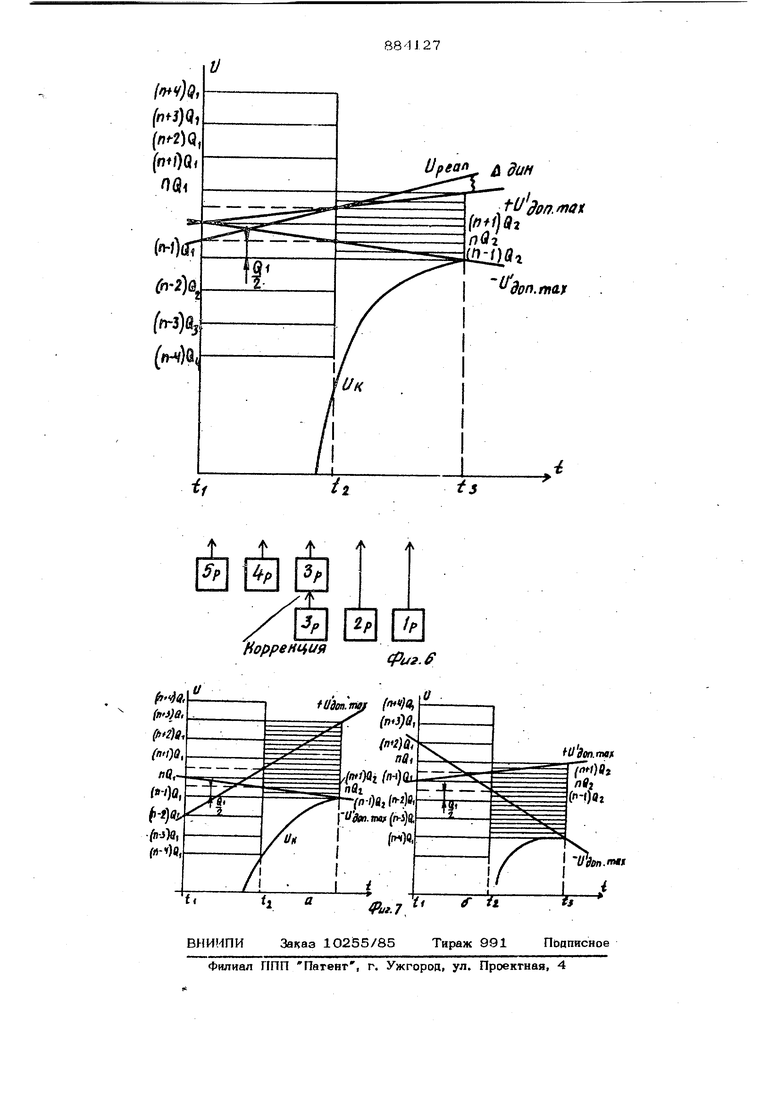

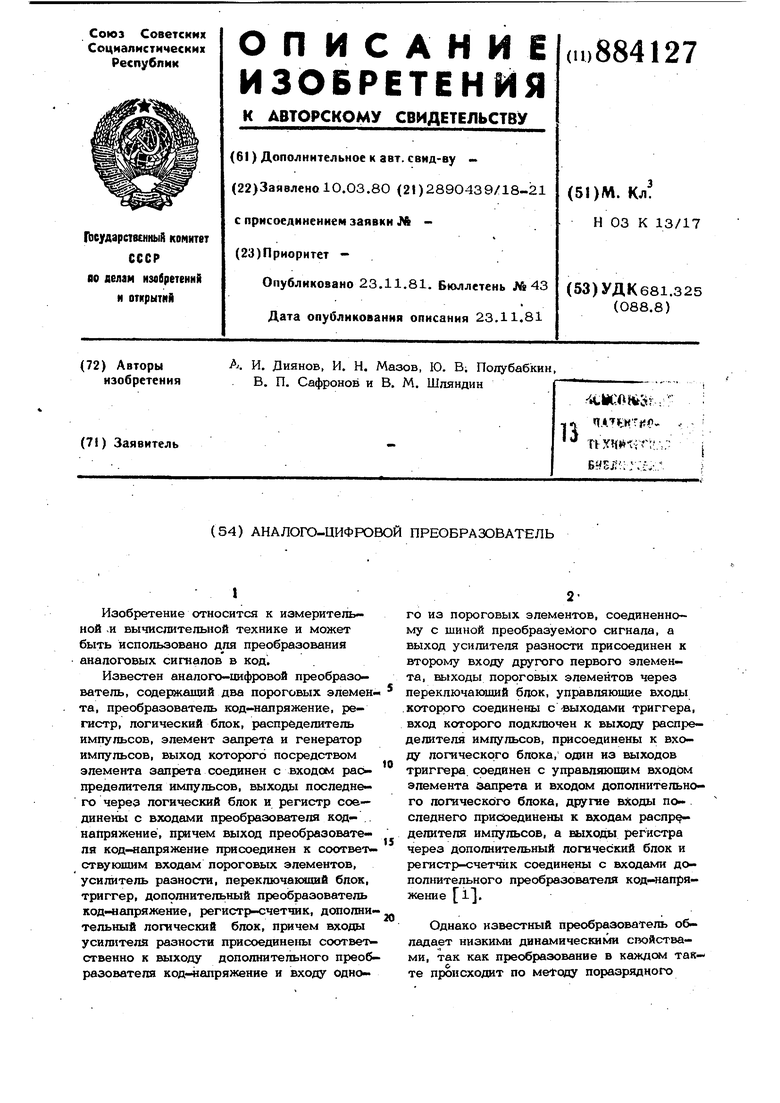

Бпок 8 можно выполнить на последочвательно соединенных каскадах о V-o(5разной функцией преобразования, а также на касакадах, каждый из которых имеет |(/-образную функцию преобразования или же на еще большем количестве параллельно соединенных узлов с V -образной функцией преобразования (так называемой параллельной сверткой входного сигнала). Конкретное исполнение блока в (соотношение количестве последоввтельиых као®кадов с количеством уапов в одном каскаде) зависит от желаемого частсггно- го диапазона, количества разрядов преобразователя, количества выбранных тактов процесса преобразования аппаратурных затрат и т.д. Частотные свойства такого блока очень высоки и достигают на соврюметгной элементной базе порядка еди ниц мегагерц. Значение ступени квантования на каждом такте преобразования одинаково, что достигается выбором определенного коэффициента усиления отдельных усилительных каскадов 13 в усилителе 2 разности (на фиг. 4 и 5 значения квантов уменьшены для наглядности процесса преобразования). Для сравнения динамических характеристик известного и предлагаемого устройств рассмотрим двухтактные схемы обоих преобразователей. Пусть количество разрядов преобразова;теля Ы равное 11. Определяется равное число разрядов на первом такте преобразования Wi рав ное 6, на втором такте N - Уу равное 5 разрядов и один разряд корректирующий. Динамическая погрешность противопостав ляемого устройства определяется из выражения, где U. скорость изменения входного сигнала; , - время преобразования усилен- ной разности Uj(-U|t грубым noporoBbDvi элементом во втором такте цикла преобразовани Время первого такта и время вьшеления разности не входит в выражение для Дд вследствие коррекции во вторсм такте динамической погрешности, возникак щей за этот интервал времени. Так как динамическая погрешность не должна пре вьппать ±О,5Су, где q, T|2JN-ступень ква тования данного ALin,,2 f/2 B предлагаемом устройстве за счет нения высокочастотного, асинхронного АЦП во втором такте динамическая погрешность возникает только при услош1и выхода значения входного сигнала за пределы зоны коррекции (4air. 6). Зона коррекции на втором такте равна ±l/2Qi где Q -1 / 2 W. Тогда предельная допустимая скорость изменения U равна U,,10 Если принять 1 ДЛ гсПЬность второго такта, выигрыш равен и;/и;. 2 Таким образом, выигрышполучается значительным и равным 32. Еше большего выиграша (в 96 раз) в уменьшении динамической погрешности, а значит, расширении спектра кодируемых сигналов, можно достичь, если применить для коррекций кода, записанного в регистре-счетчика 5 два разряда (фиг. 5). Но тогда для получения 11 разрядного кода на последнем, втором такте необходимо определять семь разрядов (пять значащих и два корректирующих). Небольшие аппаратурные затраты вполне оправдываются за счет повьш1ения спектра частот преобразуемого сигнала. С целью дальнейшего повьш1ения дина- . мической точности в устройство введен блок 12 определения знака и значения производной для определения знака и значения производной входной сигнала в момент времени -t (фнг. 7), включения в преобразователе код-напряжение определенного значения напряжения, в зависимости от знака и значения производной, а также коррекции кода в регистре-счетчике 5. На (|шг. 7 (а, б) представлены диаграммы отработки изменяющегося входного сигнала в 2-аактном АЦП, в котором на последнем такте производится коррекция двух разрядов, а также с целью повышения динамической точности производится коррекция, в зависимости от знака производной. В момент времени -tj определяется знак прсжзводной входного сигнала (стробируется регистр 24 памяти), если она отрицательна (фкг, 76), никаких изменений со стороны блока 12 определения знака и значения производной не производится. Если же значение производной входного сигнала положительное (фиг. 7а), блок 12 фиксирует знак производной и включает по сигналу с бг,ока 3 управления в преобразователе 6 код-напряжение дополнительный разряд, равный по весу 2 Q. В период времени ановление переходного процесса выходого напряжения преобразователя 6 кодапряжения, одного усилительного каскаа 13 усилителя 2 разности и блока 8. момент времени -t 3 информация о младих разрядах снимается с преобразоватея 10 кода и производится коррекция коа регистра-ч:четчика 5. Вначале произво- дится коррекция регистра-счетчика 5, в зависимости от состояния старших разрядов преобразователя 10 кода, а затем, после некоторой задержки, определяемой переходным процессом в регистре-счетчике 5 (элемент 26 задержки), заносит ся код значения веса, равного 2 Q, в регистр-счетчик 5 по сигналу с блока 3 управления и блока 12. Для этого необ, ходимо дополнительное смешение последнего каскада 13 в усилителе 2 разности на 2Q. Допустимая скорость при этом возрастает по сравнению со случаем, изображенным на фиг. 5, почти в два раза. К блоку определения производной особых требований не предъявляется, погрешность определения знака производной колеблется в пределах значений lQ,2(.7). Изобретение обеспечивает повышение динамической точности аппаратуры для вы сокоточного кодирования быстроизменяющихся сигналов. Особенно большой выигрыш в динамической точности достига ется при построении высокоточных АЦП с количеством разрядов не меньшим 10+ 11, что позволяет реализовать многоразрядный АЦП (14-15 двоичных разрядов) с высокими династическими характеристиками баз аналогового запоминающего устройства на входе преобразователя. При этом апертурное время преобразователя определяется так же как у параллельных АЦП, Формула изобретения Аналого-цифровой, преобразователь, содержащий преобразователь код-напряже ние, усилитель разности, один вход которого соединен с выходом преобразователя код-напряжение, другой с шиной преобразуемого сигнала, блоки первый, вто рой и третий, выходы блока управления соединены с соответствующими первыми входами логического блока, а выходы по следнего присоединены к входам регистра-счетчика, выходы старших разрядов которого соединены с входом преобразователя код-напряжение,о тли ча ю щ и и с я тем, что, с целью увеличения динамической точности, в него введены дополнительные преобразователи код-напряжение, коммутатор, блок последовательно соединенных элементов аналоговой свертки, блок компараторов, преоб- разователь кода, блок определения знака и значения производной, дополнительный логический блок, выходы которого соединены с счетными входами младших разрядов регистра-счетчика, а входы - с выходами старших разрядов преобразователя кода, причем выходы дополнительных преобразователей код-напряжение соединены с соответствующими входами усилительных каскадов усилителя разности, а входы - с выходами младших разрядов регистра-счетчика, при этом выходы блока последовательно соединенных элементов аналоговой свертки через блок компараторов и преобразователь кода присоединены соответственно к вторым входам логического блока, а вход блока последовательно соединенных элементов аналоговой свертки через коммутатор соединен с шиной преобразуемого сигнапа и выходами усилительных каскадов усилителя разности, управляющий вход коммутато- . ра присоединен к пятому выходу блока управления, четвертый выход которого соединен с управляющими входами дополнительного логического блока и регистра счетчика, и импульсным входом блока определения знака и значения производной, а шестой выход соединен со входом управления последнего, вход которого соединен с шиной преобразуемого сигнала, при этом первые выходы соединены с входами младших разрядов дополнительных преобразователей код-напряжение, а вторые выходы со счетными входами младших разрядов регистра счетчика. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство озер по заявкам 2612335/21, КЛ.Н ОЗ К 13/17.

tz

t3

tl

и

fy

.2 (( , Hop/ effifi ft Фиг. doti тпйк n&y -, (t, 1 ..,/ agn mui (ni-yjQ. (пф ()Q2 (-3)Q2 (n-v)a (n- (n2)Q, (f)-3)Qt N

Ж1 L

Hof / fffi4f . W/ ()(i3 nQy -.( wn.mi

Ho/ peffni Vff 2n

f.S

Авторы

Даты

1981-11-23—Публикация

1980-03-10—Подача