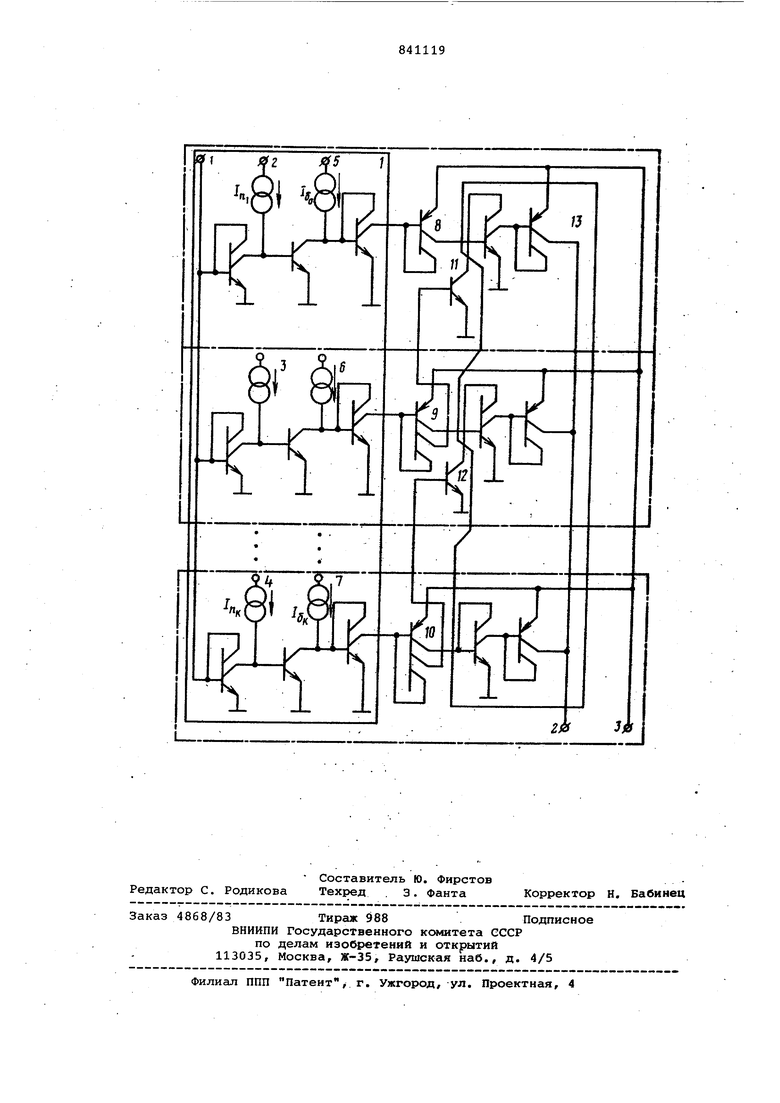

рабатывания, при помощи источников ока 5,6 и 7 регулируется выходной ток, первые дополнительные транзисторы 8, 9 и 10 первого, второго, К-каналов, базы которых соединены с выходами соответствующих дискриминаторов. и первыми коллекторами, втоые коллекторал транзисторов 8 и 9 соединены с вторым коллектором втоых дополнительных транзисторов 11 12 первого и второго каналов и соответствующими входами выходного ноговходового сумматора 13, причем базы транзисторов 11 и 12 соединены соответственно с третьими коллекторами транзисторов 9 и 10.

Устройство функционирует следующим образом.

На вход поступает входной ток, в зависимости от его величины срабатывает тот из дикриминаторов, для которого выполняется условие 1 , где IBX-входной ток, 1пк ток,задаваемый источником тока, определяющим порог срабатывания. При этом в базу первого дополнительного транзистора втекает ток, равный базисному току, задаваемому выходным током дискриминатора. Коллекторный ток этого транзистора открывает второй дополнительный транзистор, благодаря чему выходаой ток предьвдущего канала перестает поступать на выход устройства.

Задавая величины базовых токов, в предлагаемом устройстве реализуется все множество функций одной переменной многозначной логики, количество которых определяется величиной N К, где К - число каналов.

Кроме того, приведенные связи позволяют реализовать многозначный логический элемент, а также реализовать значность более высокую по сравнению со значностью, реализуемой известным элементом (), так как в зависимости от величны шага дискрета (расстояния между двумя соседними значениями многозначного кода, выраженного в амплитуде тока) приращения Ijy для двух смежных значений кода при величинах приращений токов порядка десятков микроампер предлагаемьам

элементом реализуется значность порядка 10+16 и более.

Применение метода базисных токов исключает возможность накопления ошибок при реализации на элементах дан, ного вида сложных комбинационных схем, тем самым, устраняется необходимость введения дополнительных корректирующих устройстви вычислительных структур на многозначных элемен- - тах, так как в каждом элементе ошибки устраняются источником базисных токов.

Формула изобретения

Универсальный многозначный логический элемент с промежуточным пространственным преобразованием информации инжекционного типа, содержащий входной многоканальный блок дискриминаторов с регулируемыми порогами срабатывания и величинами выходных токов , выходной многовходовой сумматор токов, выход которого соединен с выходом устройства, отличающийс я тем, что, с целью увеличения

5 значности расширения функциональных возможностей, в каждый идентичный канал введены первый и второй дополнительные транзисторы, база первого дополнительного транзистора соединена с его первьлм коллектором и выходом соответствующего дискриминатора, эмиттер - с шиной питания, второй коллектор - с базой второго дополнительного транзистора предыдущего канала, третий коллектор - с входом выходного многовходового сумматора и коллектором второго дополнительного транзистора данного канала, эмиттер которого соединен со второй общей шиной, база - с третьим коллектором

0 первого дополнительного транзистора еледущего канала.

Источники информации, принятые во внимание при экспертизе с 1. Заявка ФРГч 2627574, кл. Н 03 К 14/08; 13.01.77.

2. Авторское свидетельство СССР по заявке № 2584175,кл. Н03 К 19/08, -1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный многозначный логический элемент инжекционного типа /его варианты/ | 1980 |

|

SU890558A1 |

| Умножитель четверичный инжекционного типа | 1980 |

|

SU928651A1 |

| Устройство для вычисления полинома | 1983 |

|

SU1179323A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| Универсальный многозначный логический элемент | 1978 |

|

SU746904A1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546078C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕСТРОГОГО СРАВНЕНИЯ НА НЕРАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2547233C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ «ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ТРИ» | 2022 |

|

RU2786945C1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

Авторы

Даты

1981-06-23—Публикация

1978-11-04—Подача