(54) УНИВЕРСАЛЬНЫЙ МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мостовой диодный коммутатор | 1986 |

|

SU1370773A1 |

| Устройство для формирования разрядных токов записи | 1988 |

|

SU1550581A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Устройство для измерения тока | 1981 |

|

SU1000926A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ПРЯМОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693639C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2547225C1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Входное устройство схемы сранения токов | 1985 |

|

SU1363452A1 |

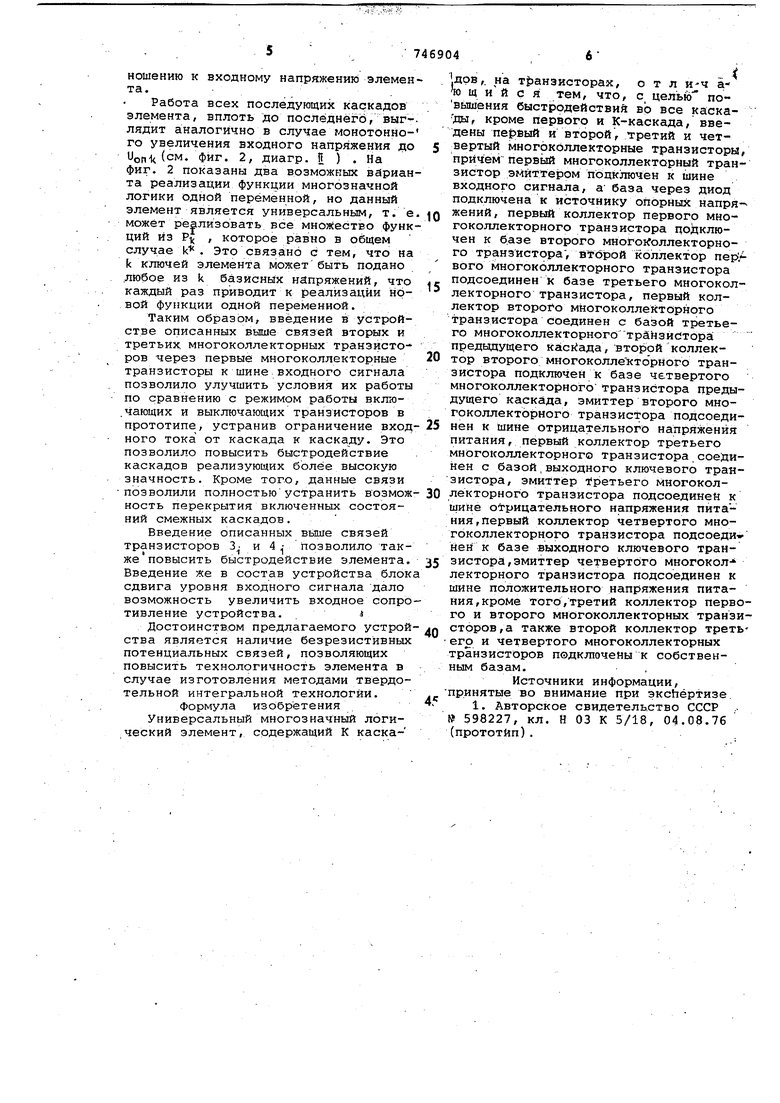

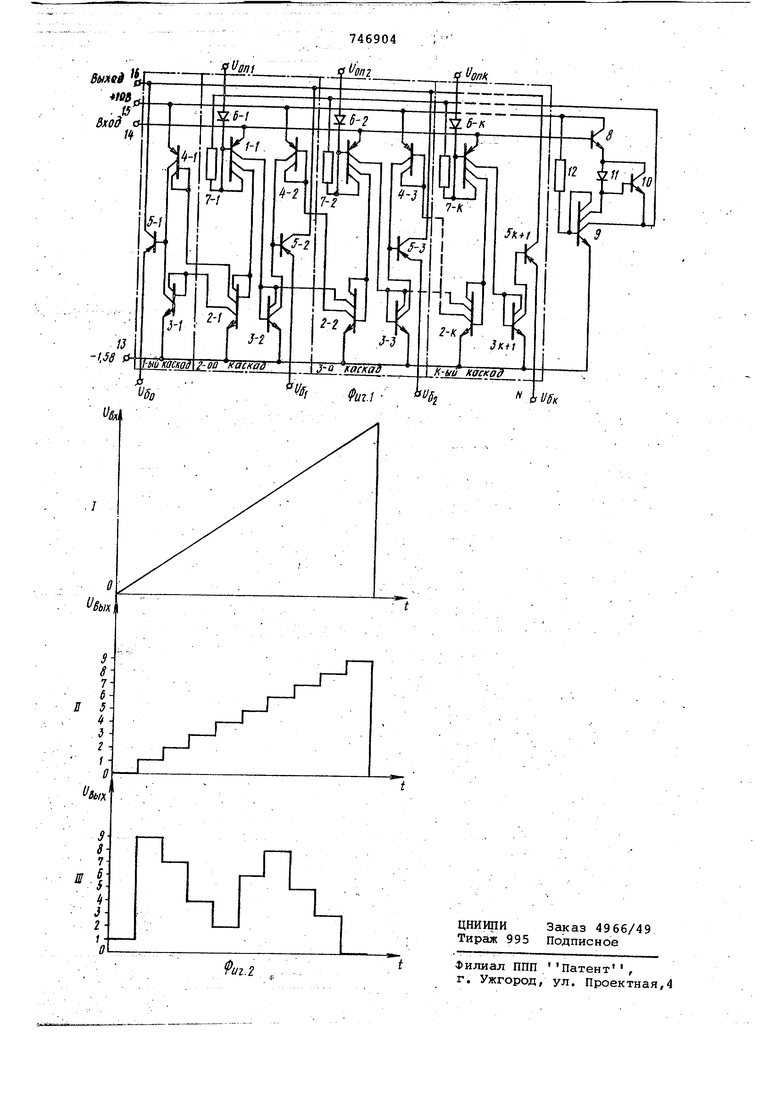

Изобретение относится к области вычислительной техники и может быть использовано в цифровых, аналоговых и гибридных вычислительных устройствах. Известен универсальный многозначньй логический с лемент, содержащий К-каскадов на транзисторах, в каждом каскаде, кроме последнего, по,одному включающему транзистору и одному выключающему, а также диодный делитель, определяющий пороги срабатывания транзисторов, причем базы выключающих транзисторов каждого каскада соединены с диодным делителем последующего каскада, а базы включающих транзисторов - с диодным делителем данного каскада l. К недостаткам амплитудного анализатора следует отнести низкое быстро действие , вызванное тем, что питание баз включающих и выключающих тра зисторов с помощью диодного делителя приводит к падению тока приходящегося на каждый последующий транзисторный каскад с ростом их числа ; кроме того, наличие в схеме амплитудного анализатора значительного количества резистивных связей снижает техиологичность устройства при его изготовлении методами твердотельной интегральной технологии. Целью изобретения является повышение быстродействия . Для достижения указанной цели в универсальный многозначный логический элемент, содержащий К каскадов на транзисторах, во все каскады, кроме первогои К-каскада, введены первый, второй, третий и четвертый многоколлекторные транзисторы, причем первый многоколлекторный транзистор эмиттером подключен к шине входного сигнала, а база через диод подключена к источнику опорных напряжений, первый коллектор первого многокоЛлекторного транзистора подключен к базе второго многоколлекторного транзистора, второй коллектор первого многоколлекторного транзистора подсоединен к ;базе третьего многоколлекторного транзистора, первый ко.ллвктор второго многоколлекторного транзистора соединен с базой третьего многоч коллекторного транзистора предыдущего каскада, второй коллектор второго многоколлекторного транзистора под-. к.гаочен к базе четвертого многоколлекl-dpHoro транзистора предыдущего каскада, эмиттер второго многоколлектор нрго транзистора подсоединен к шине отрицательного напряжения питания, кбллектбр третьего многрколлекторного транзистора соединён с ба зой выходного ключевого транзистора, эмиттер третьего миргбколлекторного транзистора подсоединен к шине отрицательного напряжения питания, первый коллектор четвертого многоколлекторного транзистора подсоединен к базе выходного ключевого транзистора, эмит тер четвертого многоколлекторного транзистора подсоединен к шине положительного напряжения питания, кроме того, третий кбллектор первого и второго многоколлекторных транзисторов, а также второй коллектор третьего и четвертого многоколлекторных транзисторов подключены к собственным базам -На фиг. 1 представлен электрическая принципиальная схема устройства, а на фиг. 2 - диаграммы входного линейно изменяющегося напряжения - диаграмма I , вЫз одйогойапрйжения устройства в случае реализации им повторительной функции - диаграмма Е , а выходное напряжение, в случае реализации элементов 10 значной функций одной переменной вида Ч 1974268530 - диаграмма Ш. Устройство содержит в каждом каскаде, кроме первого, первый многокрдлекто|рнь1й транзистор 1х -1к, второй многоколлекторный транзистор 2 2к третий мнргоколлекторный транзистор .четвертый многоколлекторный транзистор , выходной ключевой транзистор 5 -5 . Кроме того и каждом каскаде содержатся Диоды ; ( и резисторы; 7 -7, . Устройство содержит блок сдвига уровня вход ного сигнала, сформированный на тран зисторах 8, 9 и 10, диоде 11, резисторе 12, клеммы 13-16.. При этом клемма 14 является входом, а клемгта 16 выходом устройства. Устройство работает следующим образом. . ../ В исходном состоянии, когда на вх де 14 устройства входное напряжение .Нулю, транзистор первого кйска да 3;, открыт за счет подачи нулевого потенциала в его базу с коллектора . транзистора 2 и отрицательного потенцигша 1,5 В, поданного в эмиттер. При этом на базу транзистора 5 посту пает отпирающее напряжение - 1,5 В и на выходе 16 устройства поступает нап ряжение Uffe от источника базисных нап ряженйй через эмиттер-коллекторный переход открытого транзистора 5 . В этом.состоянии .четвертый многрколлёк торный транзистор первого каскада 4;, dakpiarr , так как закрыты тр1айзис трра 1 послеДукедего каскада устройства. Транзистор 1 эаКрйт пЪданным через диод 6 в его базу запирающим напряжением +Uppn , кото рое и определяет уровень отпирания Транзистора 1 в момент сравнения входного напряжения с UQ. Когда входное напряжение сравнивается с уровнем отпирания траьГзистора 1 (Up) ,он открывается и открывает транзистор 4 , закрывая при этом/ за счет открывания транзистора 2 , транзистор 3 . В результате напряжение на базе ключевого выходного. . транзистора с отпирающего (1,5 В), станобится закрывающим (+10 В) .Необходимость подачи закрывающего напряжения обусловлена тем, что при закрывании транзистора 3 и отсутствии транзистора 4 происходит медленное переключение находящегося в насыщении выходного ключ вого транзистора 5 в закрытое состояние. Подключение же в момент запирания транзистора 3 запирающего напряжения к базе транзистора 5 через транзистор. 4 обеспечивает высокое быстродействие элемента за счет быстрого выведения выходного ключевого транзистора из состояния насыщения в выключенное состояние. В этот же момент происходит включение транзистора 32 и подключение к база выходного ключевого транзистора 5 второго каскада отПиракндего напряжения -1,5 В. При этом на выходе 16 устройства поя;вляется напряжение U(f (фиг. 2, Диагр. И ) . Одновременно С увеличением входного напряжения до U блока уровня входного напряжения в базу транзистора Т через резистор 7 поступает уйе.ньшенное на падение напряжения на диоде 11 входное напряжение. При этом величина отпирающего сигнала, поступанадего в базу порогового транзистора 1, равна разности входного сигнала i| сигнала с блока сдвига уровня. Данцая разност.ь возникает вследствие того, что сигнал с блока сдвига уровня, входной сигнал и опорное напряжение, слагаясь между собой, приводят к разнице напряжения, равной в любом случае величине падения напряжения на диоде 11. Это позволяет уменьшить ВХОДНОЙ ток, проходящий через коллекторный переход транзистора 1-Г, и тем самым увеличить входное сопротивление элемента. Блок сдвига уровня представляет собой эмйттерный повторитель, нагрузкой которого служит диод 11 и транзистор 9. Транзистор 10 линеаризует вйходной сигнйл блока сдвига уровня входного сигнала. В результате падения; амплитуды входного напряжения на диоде 11 сигнал с выхода блока сдвига уровня входного сигнала имеет амплитудное значение, в каждый момент времени/ меньше чем входной сигнал, и .таким образом как бы сдвинут по отношению к входному напряжению элемен та. Работа всех последующих каскадов элемента, вплоть до последнего, выглядит аналогично в случае монотонного увеличения входного напряжения до Uon-k (см. фиг. 2, диагр, J ) . На фиг. 2 показаны два возможных вариан та реализации функции многозначной логики одной переменной, но данный элемент является универсальным, т. е можёт реализовать все множество функ ций ИЗ Р , которое равно в общем случае k . Это связано d тем, что на k ключей элемента можетбыть подано любое из k базиснь1Х напряжений, что каждый раз приводит к реализации новой функции одной переменной. Таким образом, введение в устройстве описанных выше связей вторых и третьих, многоколлекторных транзисторов через первые многоколлекторные транзисторы к шине входного сигнала позволило улучшить условия их работы по сравнению с режимом работы вклю.чающих и выключающих транзисторов в прототипе, устранив ограничение вход ного тока от каскада к каскаду. Это позволило повысить быстродействие каскадов реализующих более высокую значность. Кроме того, данные связи позволили полностью устранить возмож ность перекрытия включенных состояний смежных каскадов. Введение описанных выше связей транзисторов и 4 - позволило такжеповысить быстродействие элемента. Введение же в состав устройства блок сдвига уровня входного сигнала дало возможность увеличить входное сопро тивление устройства. 1 Достоинством предлагаемого устрой ства является наличие безрезистйвных потенциальных связей, позволяющих повысить технологичность элемента в случае изготовления методами твердотельной интегральной технологии. Формула изобретения Универсальный многозначный логический элемент, содержащий К каскадрв,. на т|)анзисторах, о т л и-ч аю щ и и с я тем, что, с целью повышения быстродействия во все каскады, кроме первого и К-каскада, введены пе|)Вый и второй, третий и четвертый многоколлекторные транзисторы, причемпервый многоколлекторный транзистор эмиттером подключен к шине входного сигнала, а база через диод подключена к источнику опорных напря-жений, первый коллектор первого многоколлекторного транзистора подключен к базе второго мноГо1 оллекторного транзистора , второй коллектор nepl вого многоколлекторного транзистора подсоединен к базе третьего многоколлекторного транзистора, первый коллектор второго многоколлекторного транзистора соединен с базой третьего многоколлекторного транзистора предьшущего кackaдa, второй коллектор второго многоколлекторного транзистора подключен к базе четвертого многоколлекторного транзистора предыдущего каскада, эмиттер второго многоколлекторного транзистора подсоединен к шине отрицательного напряжения питания, первый коллектор третьего многоколлекторного транзистора,соеДинен с базой,выходного ключевого транзистора, эмиТтер третьего многоколлекторного транзистора подсоединен к шине отрицательного напряжения питания, первый коллектор четвертого многоколлекторного транзистора подсоеди нен к базе выходного ключевого транзистора,эмиттер четвертого многокол- лекторного транзистора подсоединен к шине положительного напряжения питания, кроме Tord,третий коллектор первого и второго многоколлекторных транзисторов,а также второй коллектор треть его и четвертого многоколлекторных транзисторов подключены к собственным базам., Источники информации, принятые во внимание при эксЬёртизе. 1. Авторское свидетельство СССР 598227, кл. Н 03 К 5/18, 04.08.76 (прототип)..

Авторы

Даты

1980-07-23—Публикация

1978-06-29—Подача