Изобретение относится к автоматик и вычислительной технике, в частност к элементам пороговой логики.

Известен многопороговый логический элемент, содержащий линейный сумматор с прямым и инверсным выходами, подключенный к резистивному делителю, соединенному с многопороговым дискриминатором Г

Недостатком этого.элемента является низкое быстродействие, определяемое временем распространения сигнала через цепочку последовательно включенных однопороговых дискрими-. наторов.

Наиболее близким по технической сущности к изобретению является многопороговый логический элемент, содержащий многопороговый дискрими«натор и линейный сумматор с парафазным выходом, состоящий из входных транзисторов, объединенные коллекторы которых через первый резистивный делитель соединены с положительным полюсом источника питания, э.миттер Ксокдого из входных транзисторов через резистор, определяющий вес . входа, подключен к отрицательному полюсу источника питания и соединен с соответствующим эмиттером многоэмиттерного транзистора, база которого связана с источником опоркого сигнала, а коллектор через второй резистивный делитель подключен к положительному полюсу источника питания. Резисторы цепи, включенной в инверсном выходе линейного с кматора этого элемента рассчитываются таким образом,iчтобы присоединенные к ним транзист ы срабатывали на второй, четвертый, шестой и т.д., т.е. четные значения порога. Резисторы цепи, включенной в прямом выходе линейного сумматора, рассчитываются на нечетные значения порогов. Известно, что поро-; ги срабатывания элемента из инверсной ветви линейного сумматора вычисляются по формуле

V

(1)

де ш - вес 1-го входа элемента; 50 Т: - значение порога,, полученное по формальному аяго. ритму синтеза многопорого- вого логического элемента.

Анализ формулы (1 ) показывает, 55 то четные пороги, величина которых.

п

ULcoj+l удовлетворяет условию .

i 2

уменьшаются, по сравнению с полу- 60 ченными в результате формгшьного синтеза, а все остальные пороги с четными номерги и увеличиваются t2.

Однако данный элемент позволяет {Реализовать только те переключа-65

тельные функции, которым соответствуют полученные в результате формального синтеза нечетные пороги, не превышающие величины 5 и пере-г считанные по формуле (1 ) пороги с четными номерами, значения которых также не должны превышать 5. Например, с помощью подобного элемента нельзя реализовать функцию f (х.х-. . . ,xg) . .5)xg, для которой определенные в результате формального синтеза веса и пороги

rUJj... «} равны: ш

4,

3, Т,

2,

1, т 8.

Это 7, Т, 6,

Т5 5,

объясняется тем, что нечетный порог Т-, 5 и пересчитанный четный порог f также больше 5. Указанный недостаток сужает функциональные воз1«южности многопорогового логического элемента вследствие ограничения числа переключательных функций,которые можно реализовать одним элементом

Цель изобретения - расширение функциональных возможностей.

поставленная цель достигается . тем, что в многопороговый логичегский элемент, содержащий.многопороговый дискриминатор и линейный сумматор с парафазным выходом, состоящий из входных транзисторов, объединенные коллекторы которых через первый резистивный делитель соединешл с положительным полюсом источника питания, эмиттер каждого из входных транзисторов через резистор подключен к отрицательному полюсу .источника питания и соединен с согответствующим эмиттером многоэмиттерного транзистора, база которого связана с источником опорного сигнала, а коллектор через второй резистивный делитель подключен к положительному полюсу источника питания, введены группы из двух параллельно включенных дискриминаторов с последовательными порогами срабатывания и многовходовой логический элемент ИЛИ выход которого подключен к выходной клемме многопороговрго логического элемента, а каждый-вход -соединен с выходом срответствукицей группы из двух параллельно включенных дискриминаторов, образованных соединением коллекторов двух транзисторов, база первого и эмиттер второго транзисторов подключены к выходам.соответствующего резистивного делителя, эмиттер первого транзистора подключен к отрицательному полюсу источника питания, база второго транзистора соединена через резистор с положительным,полюсом источника питания, причем дискриминаторы с порогами срабатывания

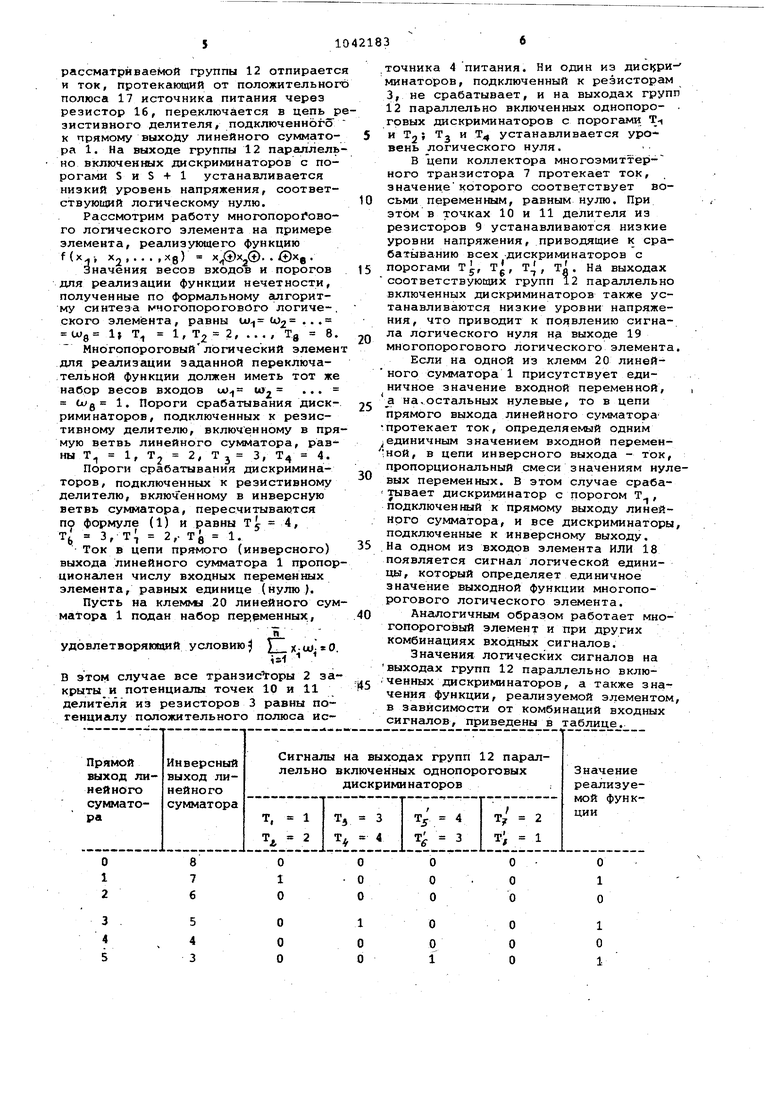

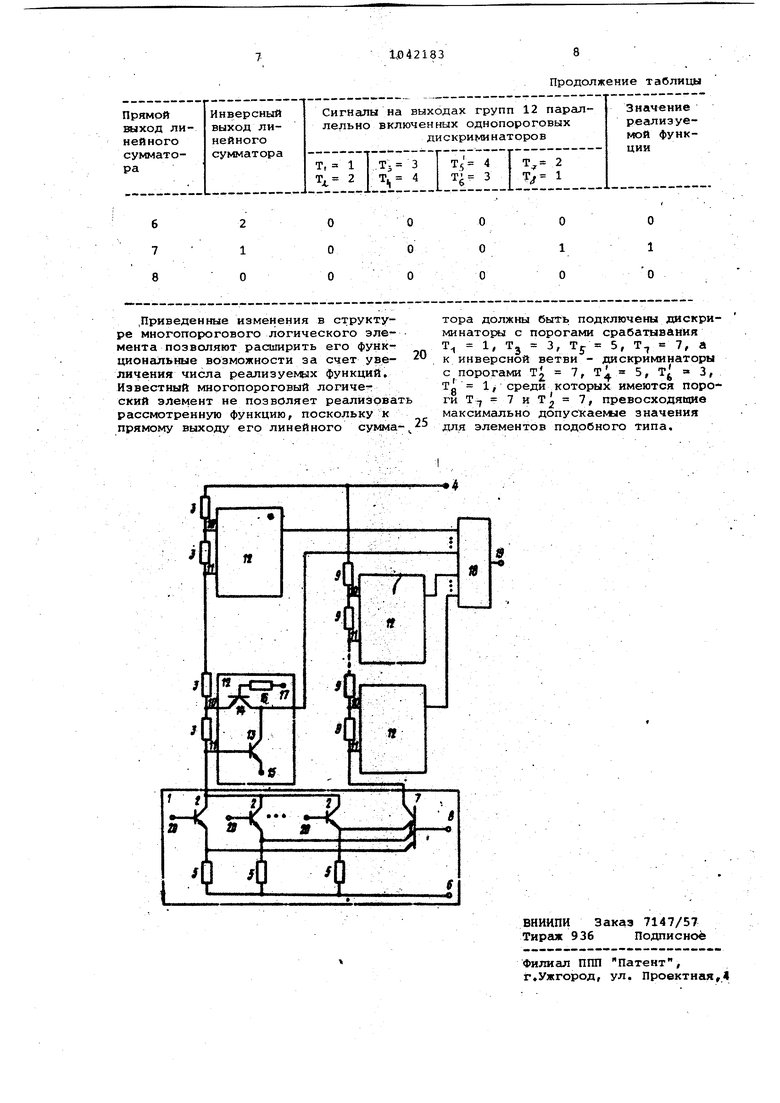

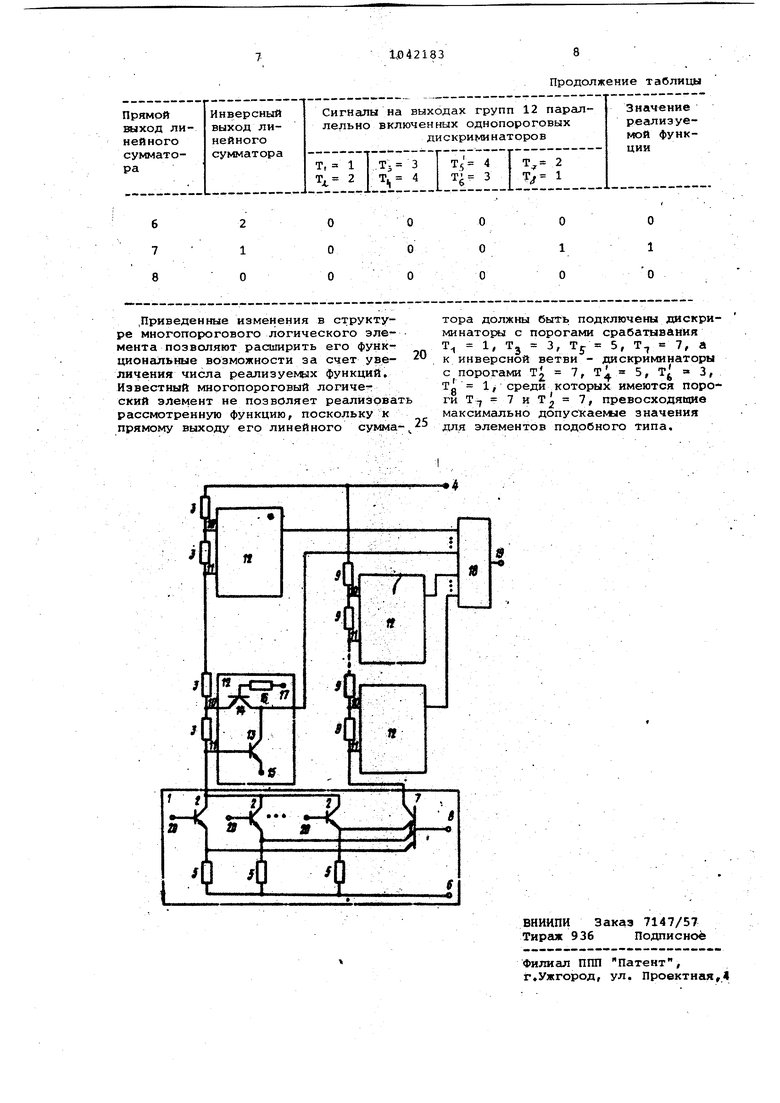

T.dtu,..,}{2, где Т; - значение порога срабатыва. . ния, полученное по формаль ному сшгоритму синтеза мно гопорогового 1огического элемента; вес i -го входа многопорогового логического элемент i 1,,..,п, соединены с выходами первого резистивного делителя, а остальные дискриминаторы соединены с выходами вт рого резистивного делителя. Изменения в структуре многопорогового логического элемента позволяют расширить функциональные возможности элемента, поскольку появляется возможность уменьшения больших величин порогов как с четными, так и нечетными номерами, за счет Подключения соответствующих дискриминаторов, к резистивному делителю, соединенному с инверсным выходом линейного сумматора. На чертеже приведена принципиальная схема .многопорогового логического элемента. Многопороговый логический элемент содержит линейный сумматор -1 с парафазным выходом, состоящий из входных транзисторов 2, коллекторы которых .объединены и соединены через резистивный делитель из резисторов 3 с положительным полюсом источника 4 питания. Эмиттеры входных транзисторов 2 через резисторы 5, определяющие веса входов, подключены к отрицательному полюсу источника 6 питания и к эмиттерс1М многоэмиттерного транзистора 7, база которого подключена к клемме источника 8 опорного сигнала, а коллектор через резистивный делитель из резисторов 9 подключен к положительному полюсу источника 4 питания. Точки 10 и 11 каждой гру пы 12 из двух параллельно включенных дискриминаторов на транзисторах 13 и 14 соединены с соответствующим последовательными выходами одного из резистивных делителей из резисто ров 3 или 9. Эмиттер транзистора 13 каждой группы 12 параллельно вклю черных дискриминаторов соединен с отрицательным полюсом 15 источника питания. База транзистора 14 через резистор 16 подключена к положитель ному полюсу 17 источника питания. Объединенные коллекторы транзисторо 13 и 14 образуют выход группы 12 параллельно включенных дискриминато ров, который связан с одним из входов элемента ИЛИ 18. Выход элемента ИЛИ 18 подсоединён к выходу 19 многопорогового логического элемента. Клем1«1 20 являются входами многопорогового логического элемента. Каждая группа 12, содержащая па1раллельно включенные однопорогоШ1е дискриминаторы с последовательны т значениями порогов, работает следующим образом. Порог срабатывания однопорогового дискриминатора на транзисторе 13 на меньше порога срабатывания дискриминатора на транзисторе 14. Пусть в рассматриваемой группе 12 пороги срабатывания дискриминаторов составляют соответственно S и S + 1. Пусть также рассматриваемая группа 12 параллельно включенных дискриминаторов соединена с резистивным делителем, подключенным к прямому выходу линейного сумматора 1. Если для комбинации двоичных сигналов, поступивших на клеммы 20 линейного сумматора 1, выполняется условие я - - ; lIlx. то ток, протекающий ; V через резистивный делитель, включенный в прямую ветвь линейного сумматора 1, создает в точках 11 и .10 падения напряжения, которые не вызывают срабатывания дискриминатора на транзисторах .13 и 14 с порогами S и S + 1.. При этом эмиттерный переход транзистора 14 заперт и ток от положительного полюса 17 источника питания через резистор 16 и коллек- . торный переход транзистора 14 по.ступает через открытый транзистор 13 к отрицательному полюсу 15 источнй- . ка питания. На выходе рассматриваемой группы 12 присутствует низкий уровень напряжения, соответствующей логическому нулю. Если выходной набор переменных многопороговогр эле I мента удовлетворяет условию J y,j,-g то через резис.тивный делитель, . включеннйй в цепь прямого выхода линейного сумматора, протекает ток, больший тока для комбинации входных -Переменных, удовлетворякжщй условию и .u).iS. приводит к понижеir1 . н1ий потенциалов в точках 10 и 11 резистивного делителя и срабатыванию дискриминатора с порогом S, Транзистор 13 рассматриваемой группы 12 параллельно включенйых дискриминаторов закрывается, и на ее выходе . устанавливается уровень Нё1пряжени|(, соответствующий логической единице. -Если для входного набора много- ,, порогового логического элемента.со-, П; , блюдаётся условие IZKio-7/s+-ffoi потенциал в точке 10 резистивного делителя понижается до величины, до- . статочной для с| абатывания дискрн- , минатора с порогом S + 1. Прн этом эмиттерный переход транзистора 14 рассматриваемой группы 12 отпираетс и ток, протекающий от положительно полюса 17 источника питания через резистор 16, переключается в цепь эистивного делителя, подключенного к прямому выходу линейного сумматора 1. На выходе группы 12 параллель но включенных дискриминаторов с порогами S и S + 1 устанавливается низкий уровень напряжения, соответствующий логическому нулю. Рассмотрим работу многопоро оного логического элемента на примере элемента, реализующего функцию Mxj, X2,...,xg) , .©Xg. Значения весов входов и порогов для регшиэации функции нечетности, полученные по формальному гшгоритму синтеза мчогопорогового логичеси (0 ского элемента, равны Ij Т, 1, Т2 2, . . . , Тд Многопороговый логический элемен для реализации заданной переключа.тельной функции должен иметь тот же набор весов входов и) 2 tJLg 1. Пороги срабатывания дискриминаторов, подключенных к резистивному делителю, включенному в пря мую ветвь линейного сумматора, равны Т 1, Т 2, Т 3 3, Т4 4. Пороги срабатывания дискриминаторов, подключенных к резистивному делителю, включенному в инверсную ветвь сумматора, пересчитываются по формуле (1) и равны Ту 4, Т 3, т; 2,. Т 1. Ток в цепи прямого (инверсного) выхода линейного сумматора 1 пропор ционсшен числу входных переменных элемента, равных единице (нулю). Пусть на клемкы 20 линейного сум матора 1 подан набор переменных. It удбвлетворяюлшй условию ). х-ю-«О В этом случае все транзисторы 2 за крыты и потенциалы точек 10 и 11 делителя из резисторов 3 равны погенцигшу положительного полюса источника 4 питания. Ни один из дис1$риминаторов, подключенный к резисторам 3, не срабатывает, и на выходах групп 12 параллельно включенных однопоро- . грвых дискриминаторов с порогами T и Т,; Tj и Т устанавливается уровень логического нуля. В цепи коллектора многоэмиттер- ного транзистора 7 протекает ток, значениекоторого соответствует восьмк переменным, равным нулю. При этом в точках 10 и 11 делителя из резисторов 9 устанавливаются низкие уровни напряжения, приводящие к срабатыванию всех дискриминаторов с порогами , т1, Т, Тп. на выходах 5 е 7 соответствующих групп 12 параллельно включенных дискриминаторов также устанавливаются низкие уровни напряжения, что приводит к появлению сигнала логического нуля на выходе 19 многопорогового логического элемента. Если на одной из клемм 20 линейного сумматора 1 присутствует единичное значение входной переменной/ а на,остальных нулевые, то в цепи прямого выхода линейного сумматора протекает ток, определяемый одним единичным значением входной переменной, в цепи инверсного выхода - ток, пропорциональный смеси значениям нулевых переменных. В этом случае срабатывает дискриминатор с порогом Т, подключенный к прямому выходу линейного сумматора, и все дискриминаторы, подключенные к инверсному выходу. На одном из входов элемента ИЛИ 18 появляется сигнал логической единицы, который определяет единичное значение выходной функции многопорогового логического элемента. Аналогичным образом работает многопороговый элемент и при других комбинациях входных сигналов. Значения логических сигналов на выходах групп 12 параллельно включенных дискриминаторов, а также значения функции, реализуемой элементом, в зависимости от комбинаций входных сигналов, приведены в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1984 |

|

SU1223359A1 |

| Многопороговый логический элемент | 1975 |

|

SU573883A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

МНОГОПОРРГОВЫЙ ЛОГИЧЕСКИЙ v ЭЛЕМЕНТ, содержащий многопороговый дискриминатор и линейный сумматор с парафазным выходом, состояпшй из . входных транзисторов, объединенные: коллекторы которых через первый : резистивный делитель соединены е положительным полюсом источника пи- тания, эмиттер каждого из входных транзисторов через резистор подключ/еЙ к отрицательному ПОЛЮСУ источника , питания и соединен с соответствующим эмиттером мно-гоэмиттерного транзис-;, тора, база которого связана с источником опорного сигнала, а коллектор через второй резистивный делитель подключен к положительному полюсу источника, питания, о т л и ч а ю щ и и с я тем, что, с целью расши-рения функциональных возможностей, он дополнительно.содержит группы из .двух параллельно включенных дис- криминаторов с последовательными порогами срабатывания и многовходовой логический элемент ИЛИ, выход которого подключен к вьоходной клемме многопорогового логического элемента, а Кс1жлый вход соединен с выходом соответствукяцей группы -из двух параллельно включенных дискриминаторов, образованных соединением коллекторов двух транзисторов, база первого и эмиттер второго транзисторов подключены к выходам соответствующего резистивного делителя, эмиттер первого транзистора подключен к отрицательному полюсу источника питания, база второго транзист ора соеди нена через резистор с положительным г полюсом источника питания, причем дискриминаторы с порогами срабаты(Л . вания , (t, т.

5 4 3

О

О О

О

О О О

О 1

Продолжение таблицы

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 2954891/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-15—Публикация

1982-04-16—Подача