. J

Изобретение относится к логическим схемам, а именно к умножителю четверичного инжекционного типа.. Известен универсальный многозначный логический элемент инжекционного типа, содержащий блок дискриминаторов с регулируемыми порогами срабатывания, дополнительные транзисторы и выходной многовходовый сумматор 1.11.

Недостаток устройства - узкие функциональные возможности.

Известен также универсальный многозначный логический элемент ижекционного типа, содерх ащий два входных многоканальных блока дискриминаторов, состоящих из многоколлекторных отражателей тока и пороговых транзисторов, дополнительные транзисторы, многовходовые сумматоры токов и выходной отражатель тока 2 ,

Недостатком известного устройства ЯВЛЯЮТСЯ узкие функциональные возможности, так как оно выполняет только логические операции и, следовательно, не формирует сигнал переноса.

Цель изобретения - расширение функциональных возможностей устройства, т.е. выполнение функции умножения по модулю с формированием сигналов произведения и переноса.

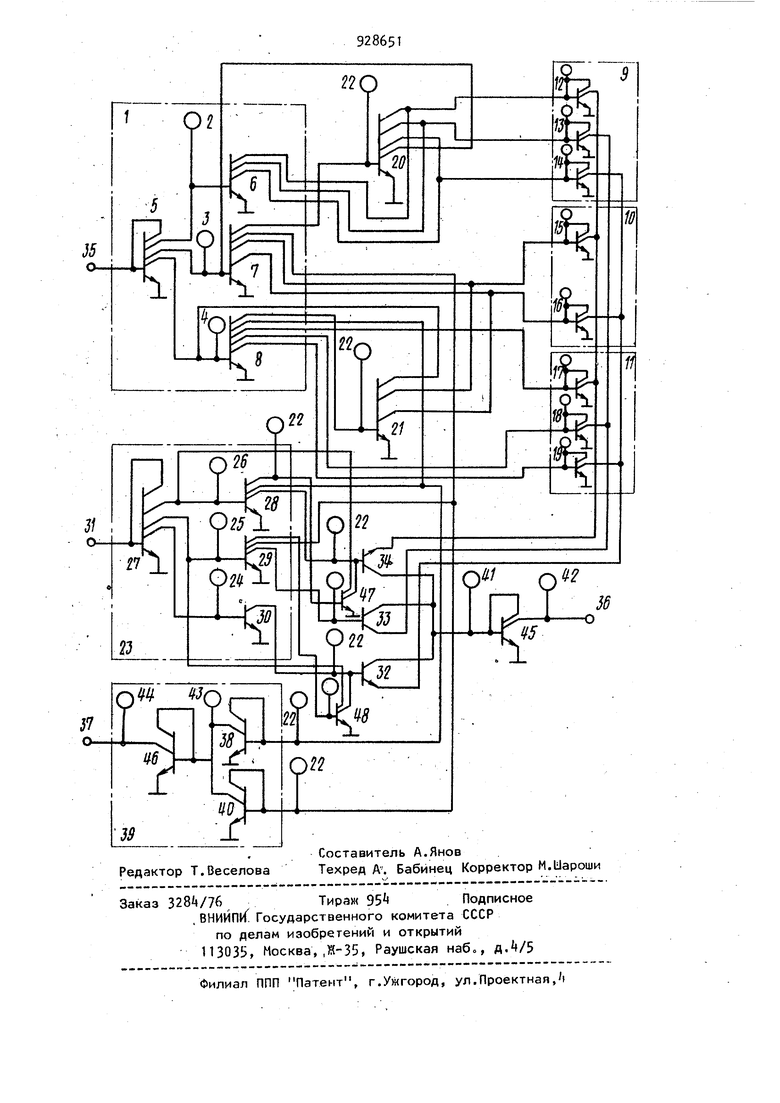

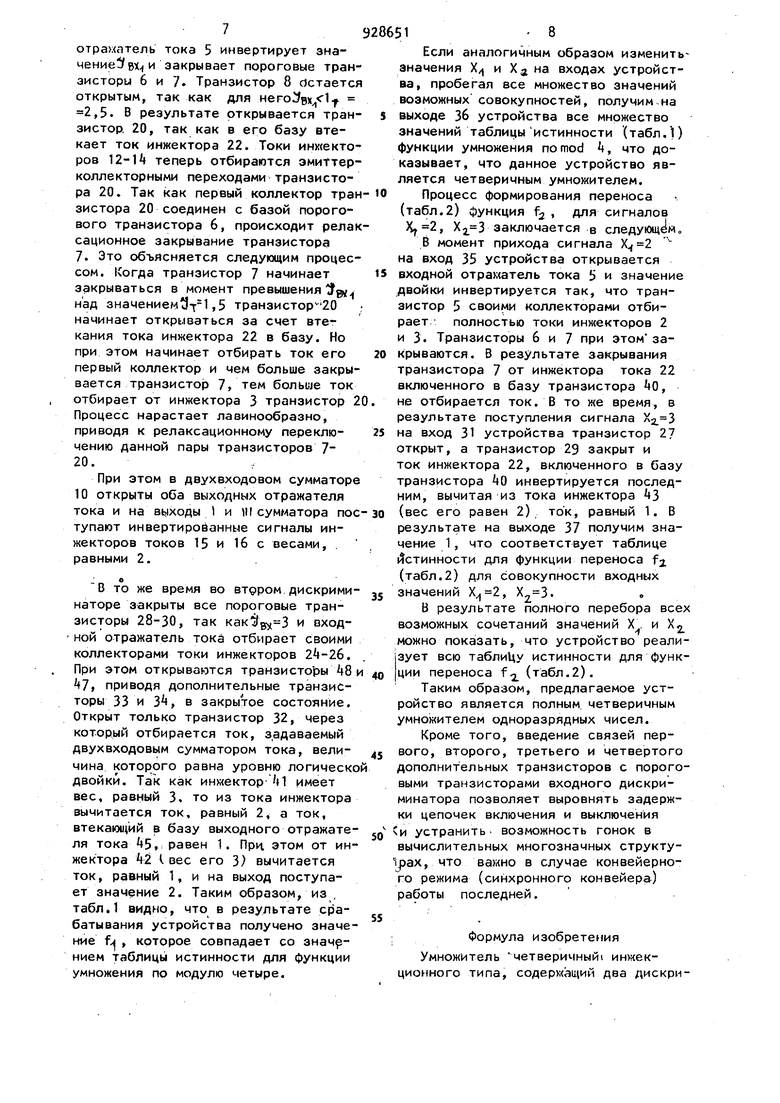

Для достижения поставленной цели в умножитель четверичный инжекционного типа, содержащий два дискрими10натора, состоящие из трехколлекторных отражателей тока, базы которых подключены ко входам устройства, а коллекторы - к пороговых транзисторов, в первом канале перво15го дискриминатора коллекторы порогового транзистора соединены со входами первого трехвходового сумматора тока, во втором канале первого дискриминатора два коллектора поро20гового транзистора соединены со входами двухвходового сумматора тока, а третий коллектор соединен с базой первого дополнительного транзистора, 3 . 9 три коллектора которого подключены к входам первого трехвходового сумматора тока, в третьем канале первого дискриминатора три коллектора порогового транзистора соединены со входами второго трехвходового сумматора тока, а четвертый коллектор соединен с базой второго дополнитель ного транзистора, два коллектора которого соединены с входами двухвходового сумматора тока, первые коллек торы пороговых транзисторов второго и третьего каналов второго дискриминатора подключены соответственно к базам третьего и четвертого дополнительных транзисторов, первые коллекторы которых подключены соответ-; ственно к второму и первому коллекто рам пороговых транзисторов первого и третьего каналов второго дискриминатора, первый и вторые коллекторы пороговых транзисторов первого, второго и третьего каналов второго диск риминатора подключены к базам пятого шестого и седьмого дополнительных транзисторов, эмиттеры которых подключены соответственно к первым, вто рым и третьим выходам каналов трехвходовых и двухвходового сумматоров тока, а Коллекторы через выходной отражатель тока подключены к выходу произведения устройства, введены два транзистора формирователя перено са , база первог.о транзистора формирователя переноса подключена соответственно к пятому и третьему кол. лекторам пороговых транзисторов третьих каналов первого и второго дискриминаторов, база второго транзистора формирователя переноса подключена соответственно к четвертому и третьему коллекторам пороговых транзисторов вторых каналов первого и второго дискриминаторов, коллекторы транзисторов формирователя переноса через дополнительный отражатель тока подключены к выходу переноса устройства, дополнительные коллекторы nepaof-o и второго дополнительных тра зисторов подключены соответственно к базам пороговых транзисторов вто рого и третьего каналов первого диск риминатора, дополнительные коллекторы третьего и четвертого дополнитель ных транзисторов подключены к базам пороговых транзисторов третьего и второго каналов второго диcкpим 1нaтора. 1 На чертеже представлена электрическая схема четверичного умножителя инжекционного типа. Устройство содержит первый дискриминатор 1. с регулируемыми при помощи источников 2-k тока инжекторов 0,5Г 1,5; 2,5 порогами срабатывания, входной отражатель тока 5 и пороговые многоколлекторные транзисторы 6-8, входящие в состав первого дискриминатора, трехвходовые и двухвходовые сумматоры 9-11 с регулируемыми инжекторами тока 12-19 с весами, равными 1, 2, 3,, 2,2 и 3, 2, 1 соответственно, первый и второй допол- . нительные транзисторы 20 и 21 с инжекторами тока 22 с весами, равными единице, второйдискриминатор 23 с регулируемыми порогами срабатывания 214-26, с весами 0,5, 1,5,2,5 соответственно, входной отражатель тока 27 и пороговые транзисторы 28-30, входящие в состав второго дискриминатора, вход второго дискриминатора 23 подключен ко второму входу 31 устройства, пятый,;шестой и седьмой дополнительные транзисторы 32-3t с инжекторами 22 с единичными весами, вход первого Дискриминатора 1 подключен к первому входу 35 устройства, выход произведения Зб и выход переноса 37, первый транзистор 38 формирователя переноса 39 и второй транзистор 0 формирователя переноса 39 инжекторами 22 с единичным весом, два инжектора 41 и 2 с весами j равными трем, два инжектора i3 и весами, равными двум, два выходных отражателя тока и 46, второй и третий дополнительные транзисторы 47 и 48. Устройство работает следующим образом. , В исходном состоянии на входы 35 и 31 не поступают входные сигналы Х и Х2. В этом случае входные отра хатели тока 5 и 27 закрыты в обоих искриминаторах, все пороговые транзисторы 6-8 28-30 открыты вследствие инжектирования тока в их базы инжекторами 2-4, 24-26. Через эмиттер-коллекторные переходы пороговых транзисторов первого репродукционного контроллера протекают токи инжекторов 12-19, а также 22, поэтому все транзисторы выходных сумматоров тока 9-11 и дополнительные транзисторы 20, 21, 32-34, 47 и 48 закрыты. 59286 Закрыты также транзисторы 38 и 0 формирователя переноса. В результате на выходах 36 и 37 устройства токовый сигнал равен нулю. Входные величины представляют собой -значение четверичные числа, представленные четверичным кодом с помоцью логических уровней тока. Работа полного умножителя четве-ричных чисел описывается таблицами истинности, соответственно для результата умножения по Ц для двух одноразрядных чисел - табл.1 и для (результата переноса - табл.2. Т а б л и ц а 1 Таблица2

Если на входы 31 и 35 поступают ходые токи в)1, соответствующие 5 20 25 30 35 40 4S 0

Рассмотрим пример умножения двух четверичных чисел с помощью предлагаемого устройства. Пусть , . В тиком случае на вход 35 поступает еч,2, а на вход 31 Техх 3. В первом дискриминаторе входной 1 одному из 1; кодовых значений ( 0,1,2,3)), в зависимости от их величины срабатывают те из транзисторов 6-8, 28-30 (закрываются), для которых выполняется условие где 3g,(- входной ток, - ток i-ro инжектора 2-, , задающего порог срабатывания пороговых транзисторов 6-8, 28-30 в первом и втором дискриминаторах 1 и 23 (,5,1,5, 2,.Q базы i-ro группы транзисторов сумматоров тока втекают токи соответствующих инжекторов. Одновременно открываются все предыдущее первые, вторые, третьи и четвертые дополнительные транзисторы 20, 21, 47, 48, так как в их базы втекают токи инжекторов 22 с весами, равными единице, отключая тем самым от баз предыдущих групп транзисторов выходных сумматоров тока инжекторы. Транзисторы, входящие в состав i-ой ГРУППЫ, открываются и на пятые, шестые и седьмые дополнительные транзисторы 32-34 поступает соответствующие сигналы от данной i-ой группы транзисторов. К выходу устройства подключен тот сигнал, для прохождения которого открыт один из дополнительных транзисторов 32-34. От инжектора тока 41 вычитается ток коллектора, который ограничен величиной тока, задаваемой с группы выходных сумматоров тока. Остаток инвертируется выходным зеркальным отражателем тока 4ij и от тока инжектора вычитается данное значение тока, а на выход умножителя поступает сигнал с сумматоров , равный результату умножения по модулю 4. Результат переноса (оункция тaбл.2)fJ, , формируется только в случае следующих сочетаний четверичных чисел: (22 (32),С23) , (33. ГГоэтому, если на входах 31 и 35 репродукционных контроллеров 1 и 23 появляются данные сочетания, происходит отбирание тока от инк{екторрв тока 22, включенных в базы транзисторов 38 и 40 формирователя переноса и возникновение результата переноса на выходе 37 устройства. отрамптель тока 5 инвертирует значение и закрывает пороговые транзисторы 6 и 7. Транзистор 8 остается открытым, так как для 2,5. В результате открывается транзистор. 20, так как в его базу втекает ток инжектора 22, Токи инжекторов 12-1 теперь отбираются эмиттерколлекторными переходами транзистора 20. Так как первый коллектор тран зистора 20 соединен с базой порогового транзистора 6, происходит релак сационное закрывание транзистора 7. Это объясняется следующим процессом. Когда транзистор 7 начинает закрываться в момент превышения3 р над значениемЗт1 5 транзистор 20 наминает открываться за счет втекания тока инжектора 22 в базу. Но при этом начинает отбирать ток его первый коллектор и чем больше закрывается транзисто13 7, тем больше ток отбирает от инжектора 3 транзистор 2 Процесс нарастает лавинообразно, приводя к релаксационному переключению данной пары транзисторов j 20. При этом в двухвходовом сумматоре 10 открыты оба выходных отражателя тока и на выходы I и 11 сумматора пос тупают инвертированные сигналы инжекторов токов 15 и 16 с весами, . равными 2. В то же время во втфром дискриминаторе закрыты все пороговые транзисторы 28-30, так и входной отражатель тока отбирает своими коллекторами токи инжекторов . При этом открываются транзисторы Л8 7, приводя дополнительные транзисторы 33 и 3, в закрытое состояние. Открыт только транзистор 32, через котор ый отбирается ток, задаваемый двухвходовым сумматором тока, величина которого равна уровню логическо двойки. Так как инх ектор И имеет вес, равный 3, то из тока инжектора вычитается ток, равный 2 а ток, втeкaюu йй в базу выходного отражателя тока 5, равен 1. Прч этом от инжектора А2 (вес его 3) вычитается ток, равный 1, и на выход поступает значение 2. Таким образом, из , видно, что в результате срабатывания устройства получено значение f , которое совпадает со значрнием таблицы истинности для функции умножения по модулю четыре. Если аналогичным образом изменитьзначения Х и Хд на входах устройства, пробегал все множество значений возможных совокупностей, получим на выходе Зб устройства все множество значений таблицы истинности (табл.) функции умножения по mod , что доказывает, что данное устройство является четверичным умножителем. Процесс формирования переноса (табл.2) с|)ункция f , для сигналов , заключается в следующем В момент прихода сигнала на вход 35 устройства открывается входной отрах атель тока 5 и значение двойки инвертируется так, что транзистор 5 своими коллекторами отбирает полностью токи инм екторов 2 и 3. Транзисторы 6 и 7 при этом закрываются. В результате закрывания транзистора 7 от инжектора тока 22 включенного в базу транзистора jO, не отбирается ток. В то же время, в результате поступления сигнала на вход 31 устройства транзистор 27 открыт, а транзистор 29 закрыт и ток инжектора 22, включенного в базу транзистора АО инвертируется последним, вычитая из тока инжектора (вес его равен 2) ток, равный 1. В результате на выходе 37 получим значение 1, что соответствует таблице истинности для функции переноса fj (табл.2) для совокупности входных значений , Z . В результате полного перебора всех возможных сочетаний значений Х,, и X,j /f можно показать, что устройство реализует всю таблицу истинности для функции переноса f (табл.2). Таким образом, предлагаемое устройство является полным, четверичным умножителем одноразрядных чисел. Кроме того, введение связей первого, второго, третьего и четвертого дополнительных транзисторов с пороговыми транзисторами входного дискриминатора позволяет выровнять задержки цепочек включения и выключения и устранить возможность гонок в вычислительных многозначных структуipax, что важно в случае конвейерного режима (синхронного конвейера) работы последней. Формула изобретения Умножитель четверичный инжекционного типа, содерх а111ий два дискриминатора, состоящие из трехколлекторных отражателей тока, базы которых подключены к входам устройства, а коллекторы - к базам пороговых транзисторов, в первом канале первого дискриминатора коллекторы порогового транзистора соединены с входами первого трехвходового сумматора тока во втором канале первого дискриминатора два коллектора порогового транзистрра соединены с входами двухвходового сумматора тока, а третий коллектор соединен с базой первого дополнительного транзистора, три коллектора которого подключены к входам первого трехвходового сумматора тока, в третьем канале первого дискриминатора три коллектора порогового транзистора соединены с входами второ о трехвходового сумматора тока, а четвертый коллектор соединен с базой второго дополнительного транзистора, два коллектора которого соединены с входами двухвходового сумматора тока первые коллекторы пороговых транзисторов второго и третьего каналов второго дискриминатора подключены соот.ветственно к базам третьего и четвертого дополнительных транзисторов, первые коллекторы которых подключены

соответственно к второму и первому коллекторам пороговых транзисторов первого и третьего каналов второго дискриминатора, я ервый и вторые коллекторы пороговых транзисторов первого, второго и третьего каналов второго дискриминатора подключены к базам пятого, шестого, и седьмого дополнительных транзисторов, эмиттеры которых подключены соответственно к первым, вторым и третьим выхоключены соответственно к базам пороговых транзисторов второго и третьего каналов первого дискриминатора, дополнительные коллекторы третьего и четвертого дополнительных транзисторов подключены к базам пороговых транзисторов третьего и второго каналов второго дискриминатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке N 2681131/18-21,

кл. Н 03 К 19/08, 1978.

2.Авторское свидетельство СССР по заявке № 2915237/18-21,

кл. Н 03 К 19/091, 1980. дам каналов трехвходовых и двухвходового сумматора тока, а коллекторы через выходной отражатель тока подключены к выходу произведения устройства, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в него введены два транзистора формирователя переноса, база первого транзистора формирователя переноса подключена соответственно к пятому и третьему коллекторам пороговых транзисторов третьих каналов первого и второго дискриминаторов, база второго транзистора формирователя переноса подключена соответственно к четвертому и третьему коллекторан пороговых транзисторов вторых каналов первого и второго дискриминаторов, коллекторы транзисторов формирователя переноса через дополнительный отражатель тока подключены к выходу переноса устройства, дополнительные коллекторы первсьго и второго дополнительных транзисторов подга

J5 ex.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Универсальный многозначный логический элемент инжекционного типа /его варианты/ | 1980 |

|

SU890558A1 |

| Умножитель двухразрядных двоичных чисел инжекционного типа | 1980 |

|

SU894704A1 |

| Полный одноразрядный сумматор инжекционного типа | 1980 |

|

SU892730A1 |

| Четырехуровневый однозарядный сумматор | 1984 |

|

SU1236463A1 |

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Рентгеновский генератор | 1983 |

|

SU1163491A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ УПРАВЛЕНИЯ ДЛЯ ТИРИСТОРА | 1991 |

|

RU2009601C1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Одноразрядный К- значный сумматор | 1987 |

|

SU1499336A1 |

j/

oJ7 o

Авторы

Даты

1982-05-15—Публикация

1980-06-18—Подача