разряда третьего регистра, информационный вход которого объединен со вторым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ и подключен к выходу четвертого одноразрядного сумматора первый и второй входы которого объединены соответственно с первым и вторым входами блока сравнения, информационный выход третьего регистра подключен к установочному входу третьего триггера и информационному ,входу третьего сдвигового регистра, выходы (h -3)-го ИИ -го разрядов которого подключены соответственно ко входу четвертого мультиплексора

третьему входу третьего одноразрядного сумматора, выход которого подключен ко входу последовательной записи информации третьего сдвигового регистра, выход ц -го разряда которого является информационным выходом устройства, тактовые входы первого, второго и третьего регистров объединены и являются тактовым входом устройства, а входы управления сдвигом первого, второго и третьего сдвиговых регистров объединены и являются входом задания количества сдвигов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Устройство для определения фазы спектральных составляющих | 1985 |

|

SU1247890A2 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для взаимной нормализации двоичных чисел | 1980 |

|

SU896616A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

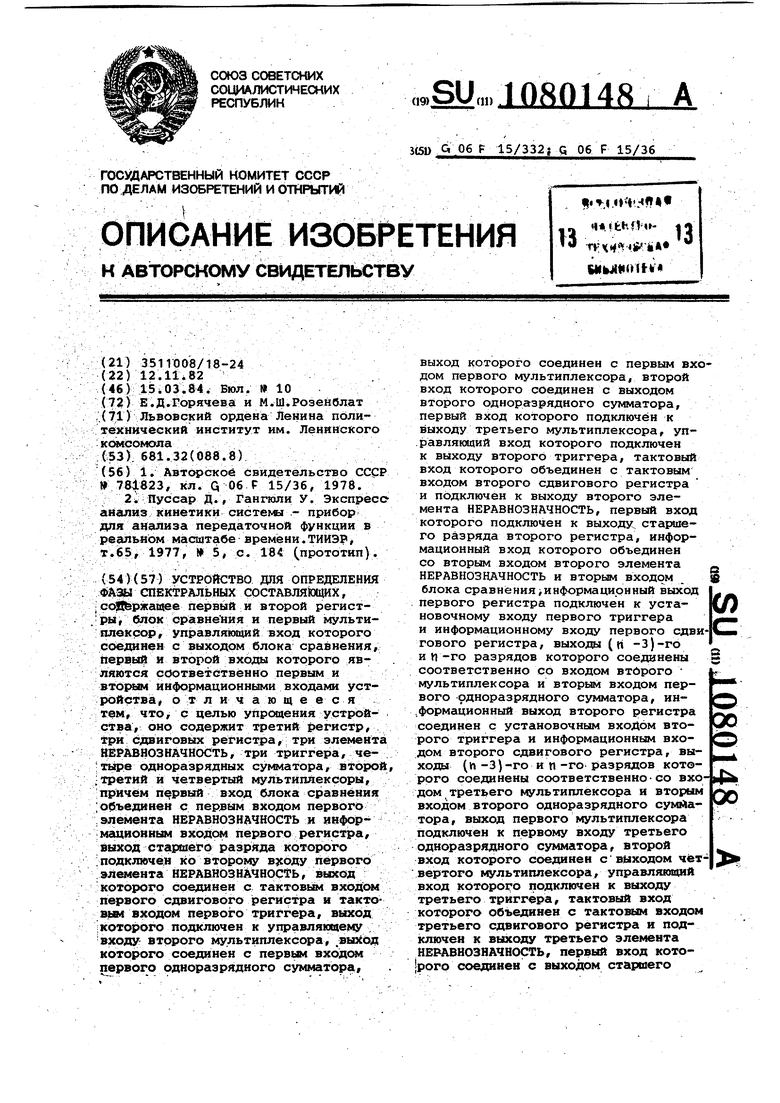

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗЫ СПЕКТРАЛЬНЫХ СОСТАВЛЯЮЩИХ, ;со {ёржа11)ее пе(вый И второй регистры, сравнения и первый мультиплексор г управляющий вход которого соедянен с выходом блока сравнения, первый и второй входы которого являются соответственно первым и вторым информационными входами устройства о т лишающееся тему что, с целью упрсяцения устройства, оно содержит третий |)егистр, tpH сдвиговых регистра,:три элемента ЙЁРАВНОЗНАЧНОСТЬ, три триггера, че;тыре одноразрядных сумматора, второй, :третий и четвертый мультиплексоры, причём первый вход блока сравнения объединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ и инфор мадионным входом первого регист|ра, выход ста1ииего разряда которого подключен ко второму В}с6ду первого элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с тактовьш входом первого сдвигового регистра и тактовьм входом первого триггера, выход КОТОРОГО подключен к управляющее ; ВХОДУ: второго мультиплексора, ,вьо

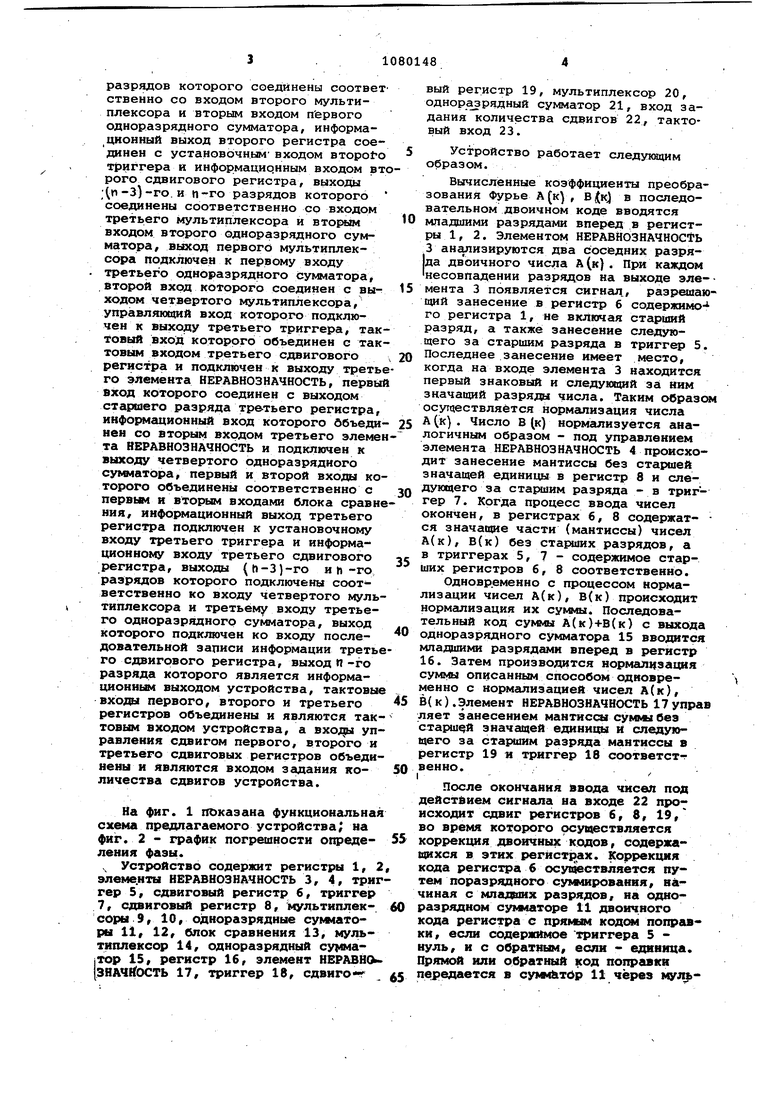

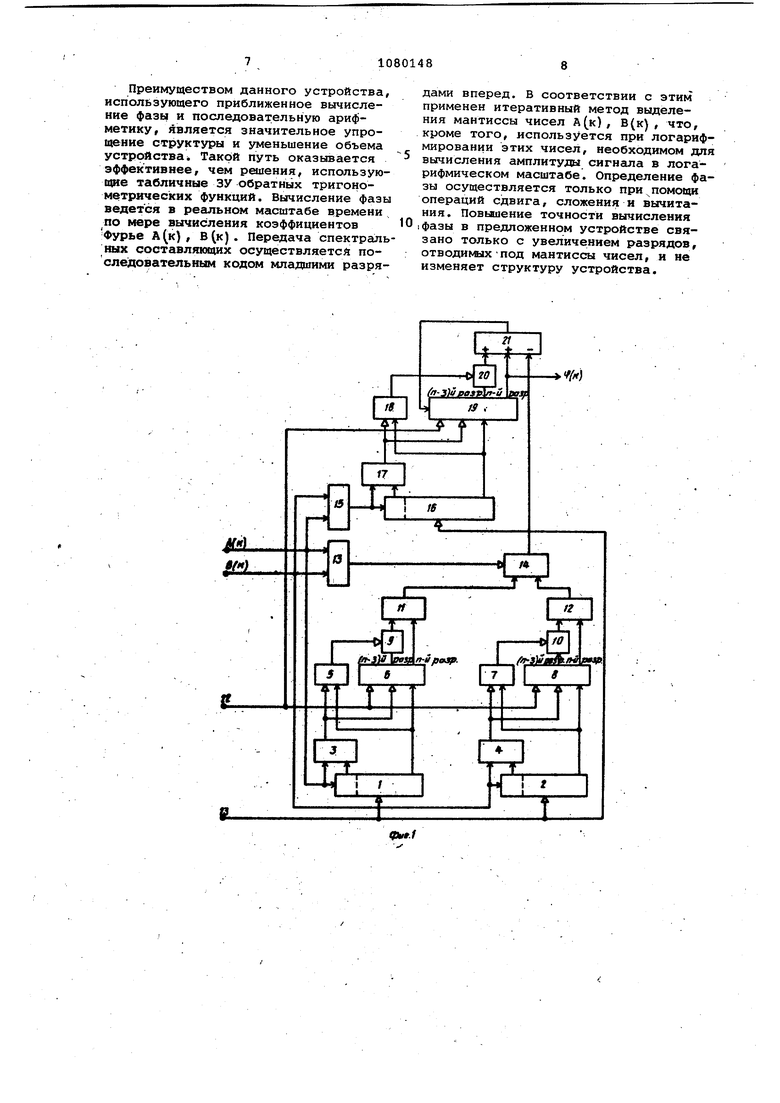

Изобретение относится к вычислительной технике, в частности к специализированным вычислительньш устройствам, и (реднаэначен6 для вычисления фазы спектральных состав ляющих в спектроанапизаторах в реальном масштабе времени. Известно устройство для определе ния фазы спектральных составлякяцих исследуемого сигнала, содержащее операционные регистры, сумматор, бл сравнения, мультиплексор, двухканал ный блок логарифмирования, блок вычитания ij . Однако такое устройство характеризуется сложностью cxei«i, наличием дорогостоящих узлов, таких как логарифматор, предполагакмций наличие ПЗУ. Нёшболее близким по технической сущности к изобретению является уст .ройство,содержащее операционные регистры, мультиплексор, блок сравнения; кроме того, в него входят дели . тель, ПЗУ, ряд ключей. При этом управлякяций вход мультиплексора соеди нен с выходом блока сравнения, перв и второй входы которого являются со ответственно первым и вторым информационными входами устройства 2 . Недостатком этой схек« является нгшичие сложных и дорогостоящих узлов, таких как делитель и 9-разрядное ПЗУ. Целью изобретения является упро1цемие устройства для определения фазы one if тральных составляющих. Указанная цель достигается тем, что устройство для определения фазы спектральных составляющих, содержащее первый и второй регистры, блок сравнения и первый мультиплексор, управляющий вход которого соединен с выхЪдом блока сравнения, пер вый и второй входы которого являются соответственно первым и вторым информационными входами устройства, содержит третий регистр, три сдвиговых регистра, три элемента НЕРАВНОЗНАЧНОСТЬ, три триггера, четыре одноразрядных сумматора, второй, третий и четвертый мультиплексоры, приче ; первый вход блока сравнения объединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ И информационным входом первого регистра, выход старшего разряда которого подключен ко второму входу первого элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с тактовым входом первого сдви гового регистра и тактовым входом первого триггера, выход которого подключен к управляющему входу второго мультиплексора, выход которого соединен с первым входом первого одноразрядного сумматора, выход которого соединен с первым входом первого мультиплексора, второй вход которого соединен с выходом второго одноразрядного сумматора, первый вход которого подключен .к выходу третьего мультиплексора, управляющий вход которого подключен к выходу второго триггера, тактовый вход которого объединен с тактовым входом второго сдвигового регистра и подключен к выходу второго элемента НЕРАВНОЗНАЧНОСТЬ, первый ВХОД которого подключен к выходу старшего разряда второго регистра, информационный вход которого объединен со вторым входом второго элемента НОЗНАЧНОСТЬ и вторым входом блока сравнения, информационный выход первого регистра подключен к установочному входу первого триггера и информационному входу первого сдвигового регистра, выходы (п-З)-го и h-ro j разрядов которого соединены соответ ственно со входом второго мультиплексора и вторым входом первого одноразрядного сумматора, информационный выход второго регистра соединен с установочным входом второго триггера и информацирнным входом вт рого сдвигового регистра, выходы )-го.и п-го разрядов которого соединены соответственно со входом третьего мультиплексора и вторым входом второго одноразрядного сумматора, выход первого мультиплексора подключен к первому входу третьего одноразрядного сумматора, Второй вход которого соединен с выходом четвертого мультиплексора, управлякжаий вход которого подключен к выходу третьего триггера, так товый вход которого объединен с так товым входом третьего сдвигового регистра и подключен к выходу треть го элемента НЕРАВНОЗНАЧНОСТЬ, первы вход которого соединен с выходом старшего разряда третьего регистра, информационный вход которого дбъеди иен со вторым входом третьего элеме та НЕРАВНОЗНАЧНОСТЬ и подключен к выходу четвертого одноразрядного сум4ат6ра, первый и второй входы ко торого объединены соответственно с первым и вторым входами блока сравн ния, инфО1 ационный выход третьего регистра подключен к установочному входу третьего триггера и информа- ционному входу третьего сдвигового регистра, выходы (й-З)-го иh -го разрядов которого подключены соответственно ко входу четвертого муль типлексора и третьему входу третьего одноразрядного сумматора, выход которого подключен ко входу последовательной записи информации треть го сдвигового регистра, выход «-го разряда которого является информационньвх выходом устройства, тактовы входа первого, второго и третьего регистров объединены и являются так товым входом устройства, а уп равления сдвигом первого, второго и третьего сдвиговых регистров объеди нены и являются входом задания количества сдвигов устройства. На фиг. 1 показана функциональна схема предлагаемого устройства; на фиг. 2 - график погрешности определения фазы. . Устройство содержит регистры 1, элеме.нты НЕРАВНОЗНАЧНОСТЬ 3, 4, три гер 5, сдвиговый регистр 6, триггер 7, сдвиговый регистр 8, мультиплексоры 9, 10, одноразрядные су «аторы 11, 12, блок сравнения 13, мультиплексор 14, одноразрядный сумма|тор 15, регистр 16, элемент НЕРАВНО 3HA4ffOCTb 17, триггер 18, сдвиге-f вый регистр 19, мультиплексор 20, одноразрядный сумматор 21, вход задания количества сдвигов 22, тактовый вход 23. Устройство работает следукнцим образом. Вычисленные коэффициенты преобразования Фурье А (к), BJ(KJ в последовательном двоичном коде вводятся младшими разрядами вперед в регистры 1, 2. Элементом НЕРАВНОЗНАЧНОСТЬ 3 анализируются два соседних разря|да двоичного числа А (к) . При каждом несовпадении разрядов на выходе эле- мента 3 появляется сигнал., раэр&ааю щий занесение в регистр б содержимого регистра 1, не включая старишй разряд, а также занесение следующего за старшим разряда в триггер 5. Последнее занесение имеет место, когда на входе элемента 3 находится первый знаковый и следуюпщй за ним значащий разряды числа. Таким образом осуществляется нормгшизация числа А (к) . Число В (к) нормализуется аналогичным образом - под управлением элемента НЕРАВНОЗНАЧНОСТЬ 4 происходит занесение мантиссы без старшей значащей единицы в регистр 8 и следующего за старшим разряда - в триггер 7. Когда процесс ввода чисел окончен, в регистрах 6,8 содержат- ся значащие части (мантиссы) чисел А(к), В(к) без старших разрядов, а в триггерах 5, 7 - содержимое старших регистров б, 8 соответственно. Одновременно с процессом нормализации чисел А(к), В(к) происходит нормализация их . Последовательный код суммы А(к)+В(к) с выхода одноразрядного сумматора 15 вводится младшими разрядами вперед в регистр 16. Затем производится иормглчзацня суммы описанным способом одновременно с нормализацией чисел А(к}, В(к).Элемент НЕРАВНОЗНАЧНОСТЬ 17управ ляет занесением мантиссы суммы без старшей значащей единищл и следующего за старшим разряда мантиссы в регистр 19 я триггер 18 соответстт венно., После окончания ввода чисел под действием сигнеша на входе 22 происходит сдвиг регистров б, 8, 19, во время которого осу|цествляется коррекция двоичных кодов, содержа111ихся в этих регйст1)ах. Коррекция кода регистра б осугцествляется путем поразрядного суммирования, начиная с младфоих разрядов, на одноразрядном су маторе 11 двоичного кода регистра с прямым кодом поправки, если содержмкое триггера 5 нуль, и с обратным, если - единица. Прямой или обратный код поправки передается в су|«(&тдр 11 через нуль.тйплексор 9, которым управляет триг гер 5. Поправка равна двоичному коду регистра б, сдвинутому на 3 разряда в сторону млгщших разрядов.Одновременно аналогичным образом осуществляется коррекция двоичного кода регистра 8 на сумматоре 12, мультиплексоре 10, триггере 7 и коррекция двоичного кода регистра 19 на сумматоре 21, мультиплексоре 20 и триггере 1.8. Блок сравнения 13 сравнивает по абсолютной величине числа А{к) и В{к), определяет большее и управляет мультиплексором 14 на его выходе появляется откорректированный двоичный код мантиссы

(w,+M,VH(M,4M,(M,,,eM«UM,4.5

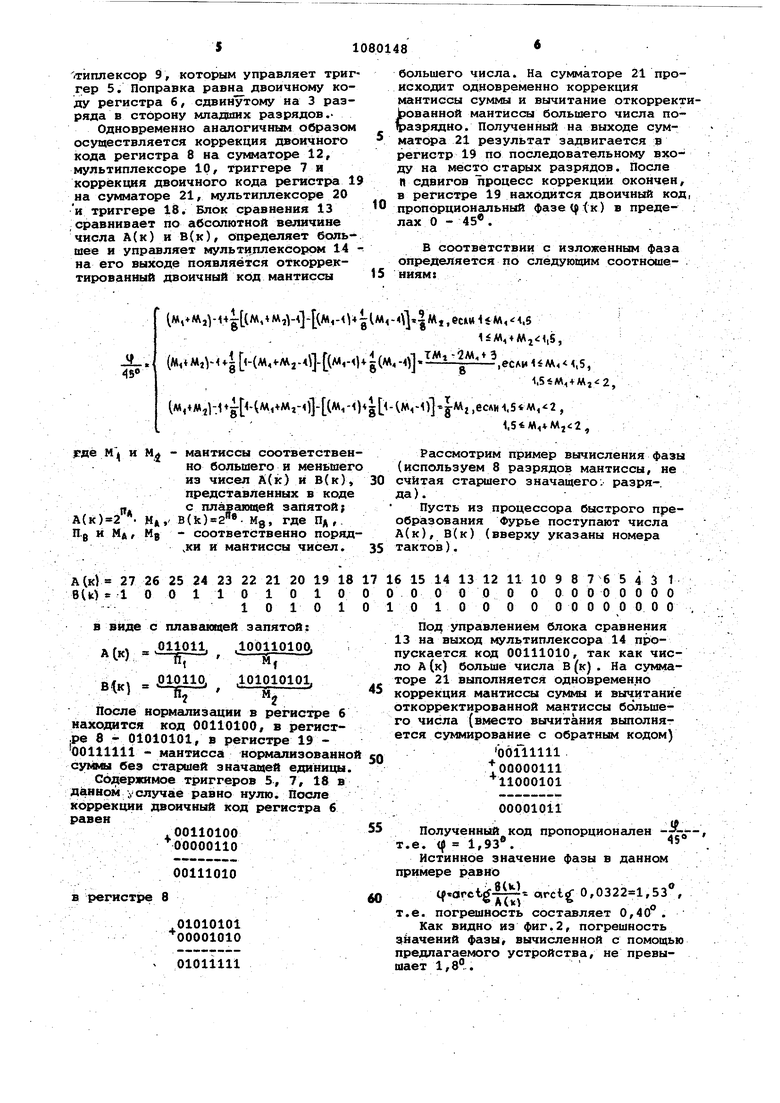

(, уде M,j и И А(к:)2 n.g и Мд, A(K) 27 26 25 24 23 22 21 20 19 18 17 16 8U) 1 О О 1 1010 1 000 1 О 10 1 01 в виде с плавеиощей запятой: .100110100. .011011. V .101010101. 510110, После нормализации в регистр находится код 00110100, в реги ре 8 - 01010101, в регистре 19 00111111 - мантисса нормализов суммы без старшей значащей един содержимое триггеров 5, 7, 1 данном Vслучае равно нулю. Посл коррекции двоичный код регистра равен .00110100 00000110 00111010 в регистре 8 .01010101 ooooioio oioiiiii

большего числа. На сумматоре 21 происходит одновременно коррекция мантиссы суммы и вычитание откорректрованной мантиссы большего числа поразрядно. Полученный на выходе сумматсфа 21 результат задвигается в регистр 19 по последовательному входу на место старых разрядов. После ц сдвигов Ъроцесс коррекции окончен, в регистре 19 находится двоичный код пропорциональный фазе(1к) в пределах О - 45®.

В соответствии с изложенным фаза определяется по следующим соотношениям:

ИАЛ, + ,5,

TMt-2M,t3

,,5, в

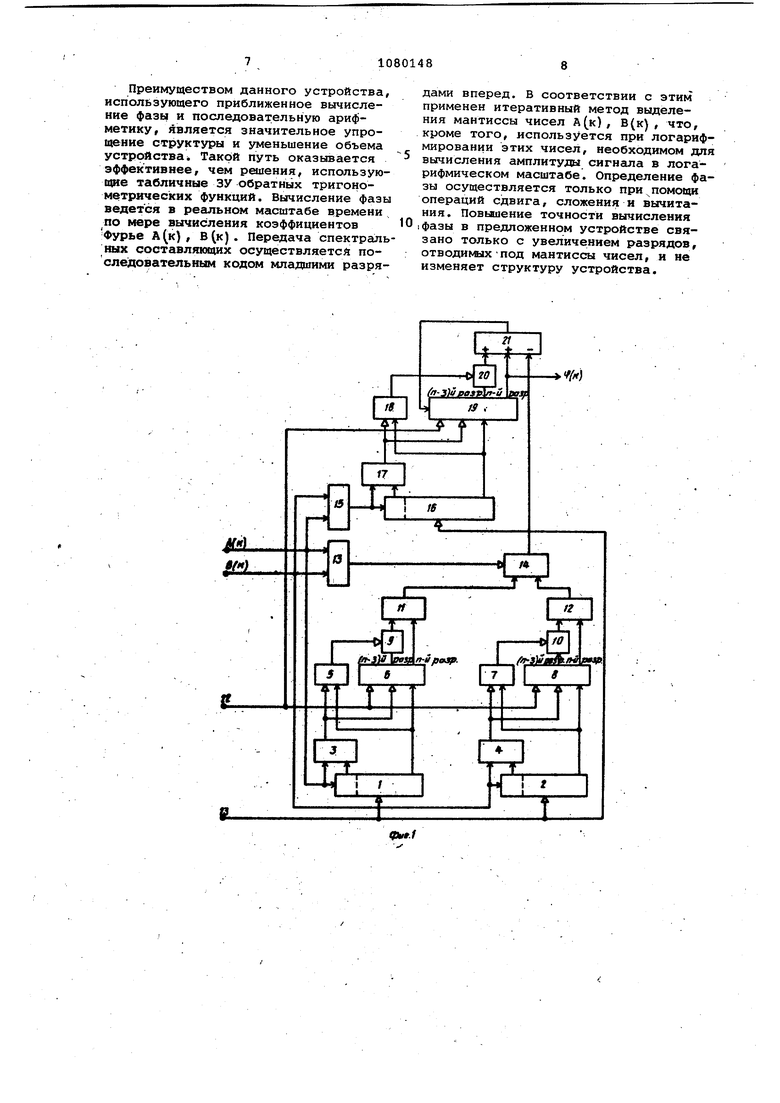

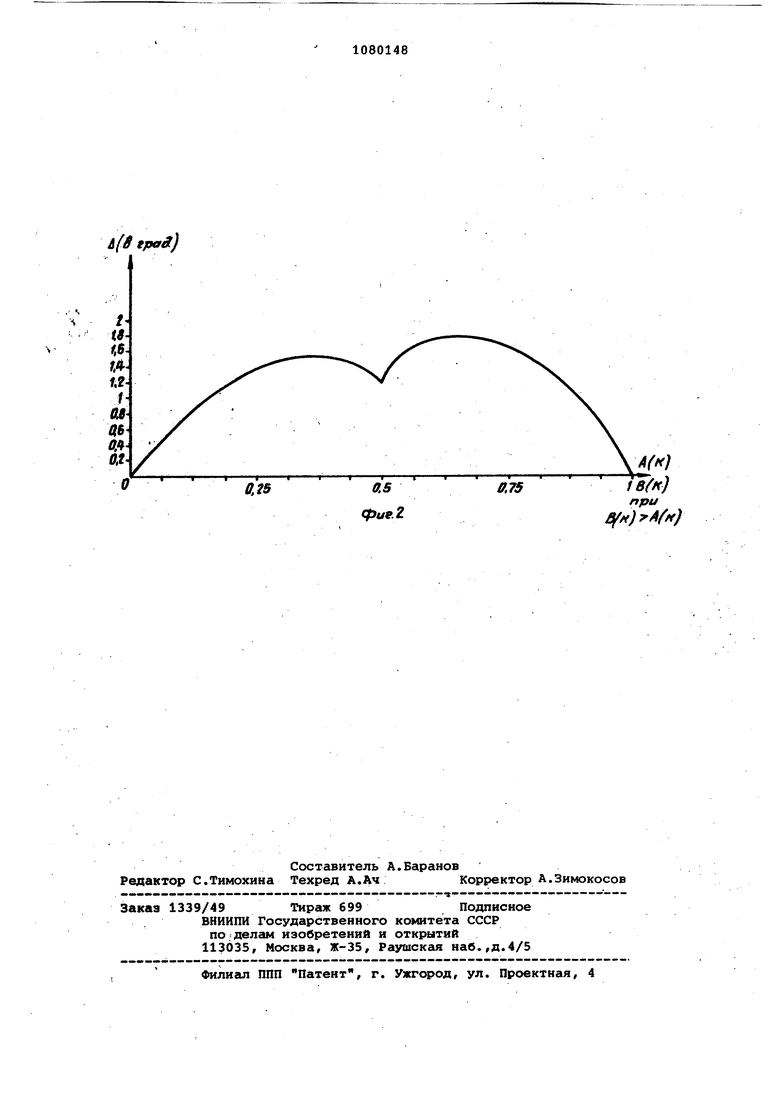

1,56M, + , (M,tM,)-.(M,-i))g-Wz,ecA),i.5«M,-:2, Mj - мантиссы соответствен- Рассмотрим пример вычисления фазы но большего и меньшего(используем 8 разрядов мантиссы, не из чисел А(к) и В(к), 30считая старшего значащего, разря-. представленных в кодеда). с плавающей запятой; Пусть из процессора быстрого преМц, B(k) Mg, где Пд ,.образования Фурье поступают числа MB - соответственно поряд-А(к),В(к) (вверху указаны номера ,ки и мантиссы чисел. 35тактов). ., 15 14 13 12 11 10 9 8 765 4 3 1 0000 О О 00000000 0 100 О О 00000000 Под управлением блока сравнения 13 на выход мультиплексора 14 пропускается код 00111010, так как число А(к) больше числа В (к). На сумматоре 21 выполняется одновременно коррекция мантиссы суммы и вычитание откорректированной мантиссы большего числа (вместо вычитания выполняется суммирование с обратным кодом) bofiiiii /toooooiii IIOOOIOI 00001011 L. Полученный код пропорционален 45 т.е. (f 1,93 Истинное значение фазы в данном примере равнй .- 0(0,,53, т.е. погрешность составляет 0,40. Как видно из фиг.2, погрешность Значений фазы, вычисленной с помощью предлагаемого устройства, не превышает 1,8°.

Преимуществом данного устройства, использующего приближенное вычисление фазы и последовательную арифметику, является значительное упрощение структуры и уменьшение объема устройстваi Такой путь оказывается эффективнее, чем решения, использующие табличные ЗУ обратных тригонометрических функций. Вычисление фазы ведется в регшьном масштабе времени по мере вычисления коэффициентов Фурье А(К) , В (к). Передача спектральных составляющих осуществляется последовательным кодом младшими разрядами вперед. В соответствии с этим применен итеративный метод выделения мантиссы чисел А(К), В(к) , что, кроме того, используется при логарифмировании этих чисел, необходимом для вычисления амплитуды сигнгша в логарифмическом масштабе. Определение фазы осуществляется только при помощи операций сдвига, сложения и вычитания. Повышение точности вычисления 1фазы в предложенном устройстве связано только с увеличением разрядов, отводиьфахПОД мантиссы чисел, и не изменяет структуру устройства.

/

(6 tpaff)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Высевающий диск точного высева семян | 1976 |

|

SU784823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь-плита | 1920 |

|

SU184A1 |

Авторы

Даты

1984-03-15—Публикация

1982-11-12—Подача