(54) ГРУППОВОЙ СТАНДАРТ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство определения азимута | 1984 |

|

SU1190747A2 |

| Демодулятор фазоманипулированных сигналов с компенсацией помех | 1987 |

|

SU1545332A1 |

| Устройство определения азимута | 1984 |

|

SU1190746A2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Устройство для формирования частотно-манипулированных сигналов | 1985 |

|

SU1297247A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛА МНОГОПОЗИЦИОННОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИИ С ЭКВИДИСТАНТНЫМ РАЗНЕСЕНИЕМ ПО ЧАСТОТЕ, ДЕМОДУЛЯТОР ТАКОГО СИГНАЛА И МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ | 2005 |

|

RU2290749C1 |

| Устройство для формирования частотно-манипулированных сигналов | 1986 |

|

SU1319303A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Резервированный генератор | 1978 |

|

SU746975A1 |

| Устройство для воспроизведения с носителя магнитной записи | 1988 |

|

SU1624517A1 |

1

Изобретение относится к радиотехнике и может использоваться в уст- . ройствах, фор1«мрую1цих выходной сигнал высокостабильной частоты.

Известен групповой стандарт частоты,содержгидий три канала,каждый из которых состоит из пос.педовательно соединенных стандарта частоты, фозовращателя и фазового детектора, причем второй вход фазового детектор -первого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго .канала соединен с выходоь фазовращателя третьего канала, а второй вход.фазового детектора третьего канала соединен с выходом фазовращателя первого канала l ..

Однако известный стандарт частоты имеет плохую долговременную стабильность выходного сигнала.

Цель изобретения - улучшение долговременной стабильности выходного сигнала.

Поставленная цель достигается тем чт.о в групповой стандарт частоты, содержащий три канала,.каждый из которых состоит из последовательно соединенных стандарта частоты, фазовраща-. теля и фазового .детектора, причем

второй вход фазового детектора первого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго канала соединен с. выходом фазовращателя третьего канала, а второй вход фазового детектора третьего канала соединен с выходом фазовращателя первого канала, введены последовательно соеди0ненные вычислитель среднего значения частоты, блок формирования сигналов управления и решающий блок, а также блок анализа фазовых сяиибок, при этом сигнальные выходы стандарта частоты

5 ка)кдого из каналов соединены с соответствующими входами вычислителя среднего значения частоты и блока формирования сигналов управления, выходы которого подключены к управляющему

0 входу стандарта частоты соответствующего канала, информационные выходы которых соединены со вторыми входами решающего блока, третьи входы которого подключены к соответствующим вы5ходам блока анализа фазовых сшибок, входы которого соединены с выходами фазовых детекторов каждого из каналов, при этом в каждом из каналов введены ключ и последовательно соединенные

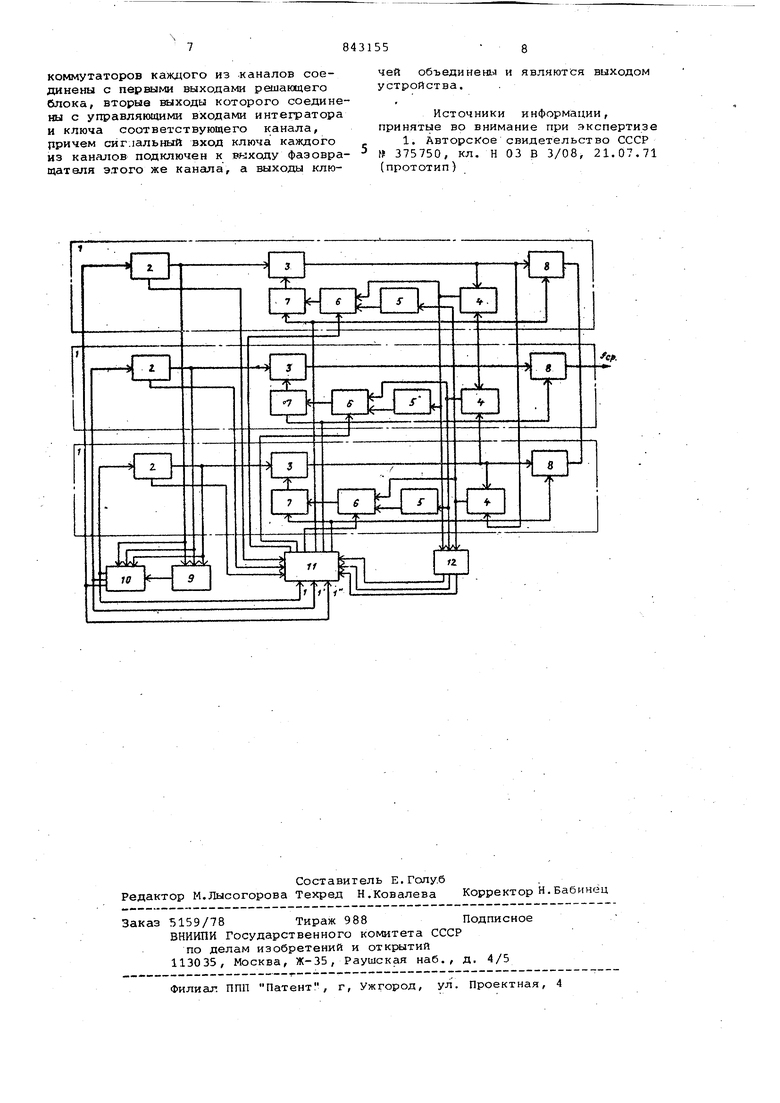

0 инвертор, коммутатор и интегратор. выход которого соединен с управляющи входом фазовращателя этого же канала другой вход коммутатора подключен к выходу фазового детектора этого же к нала, вход инвертора второго канала соединен с выходом фазового детекто-. ра первого канала,.вход инвертора третьего канала соединен с выходом фазового детектора второго канала, а вход инвертора первого канала -соединен с выходом фазо- вого детектора третьего канала, управляющие входы коммутаторов каждого из каналов соединены с первыми выходами решагацего блока, вторые выходы которого соединены с управляющими входами интегратора н.клю ча соответствующего канала, причем сигнальный вход ключа каждого из каналов подключен к выходу фазовращате ля этого же канала, а выхо.цы ключей объединены и являются выходом устрой ства. На чертеже представлена структурная электрическая схема предлагаемого стандарта частоты. Групповой стандарт частоты содержит три канала 1, каждый из которых состоит, из стандарта 2 частоты, фазовращателя 3, фазового .детектора 4, инвертора 5, коммутатора б, инт егратора 7 и электронного ключа 8, вычис литель 9 среднего значения частоты, блок 10 формирования сигналов управления, решающий блок 11, блок 12 . анализа фазовых ошибок,. . Устройство работает следующим- образом. Выходные сигналы стандартов 2 час тоты каждого канала 1 с частотами f, , f и f,, через фазовращатели 3 поступак)т на входи электронных ключе 8. Одновременно они поступают на вход вычислителя 9, который производит периодическое измерение разностей частот стандартов 2 частоты, Причем измерения производятся по кол цу, например л . f - f-g.; A-f2-3.. 2. Лf.j f fvj И вычисляе среднее значение частоты, исчисление отклонения частоты каждого стандарта 2f. от среднего значения f(.p и вырабо ка управляющего воздействия, пропорционального ( fср - fi ), производится блоком 10 формирования сигналов управления. В результате воздействия сигналов управления на выходах станЬартов 2 частоты и, соответственно, на входах электронных ключей 8 будут действовать сигналы стандартов 2 час тоты, подстроенные к . Время обработки сигнала вычислителем 9 и период между подстройками выбирается исходя из качества стандартов частоты, определяемого паспортными значениями- их погрешности и вариаций действительного занчения ча тоты (ДЗЧ), Точное фазирование выходных сигналов с ошибкой менее осуществляется с помощью фа;зовращателей 3, охваченных системой фазовоп| автоподстройки .В состав цепи автоподстройки входит фазовый детектор 4, коммутатор б, интегратор , Как видно из чертежа -коммутируя входные сигналы коммутатора б, схема позволяет либо разомкнуть цепь автоподстройки, либо осуществить подстройку фазовращателя 3 сигналаг-ш управления с выхода фазового детектора 4 данного или предыдущего канала. Включение инвертора 5 в цепь автоподстройки позволяет исключить перестройку фазы выходного сигнала фазовращателя при переключении выхода фазового детектора 4 данного канала ДЛ.Я управления фазовращателем соседнего канала. Каждый из каналов может работать в режиме автоподстройки или режиме храненИя (.памяти) фазы. Канал, находящийся в режиме памяти, является ведущим. Обеспечение режима памяти осуществляется по команде, поступающей с решающего блока 11 на коммутатор б данного канала. При этом в ведущем канал-е коммутатор, разрывает цепь автоподстройки фазовращателя 3 и замыкает их в других каналах. Причем замкнуты цепи автоподстроек по тем входам коммутаторов 6, при замыкании которых обеспечивается последовательная подстройка сигналов по фазе выходного сигнала фазовращателя ведущего канала. Одновременно с подачей сигнала управления на коммутатор 6-с решающего блока 11 выдается команда управления на интегратор 7 и электронный ключ 8 каждого канала. По этой команде интегратор 7 ведущего канала хранит напряжение, имевшее место на момент перехода канала в режим , а интеграторы 7 других каналов работают в режиме синхронизации сигйалов по фазе ведущего канала. По этой же команде замыкается электронный ключ В ведущего канала и размыкаются цепи электронных ключей 8 других каналов, в результате чеГо на выход устройства транслируется сиг-т нал с выхода стандарта частоты ведущего канала.. Нормальная работа цепей автоподстроек; фазовращателей в каналах контролируется при помощи блока 1.2 анализа.фазовых ошибок. При исправной работе цепей автоподстроек фазовращателей 3 с выходов фазовых детекторов . 4 на вход блока 12 анализа фазовйх сшибок подаются напряжения ифд О, соответствуюгдие нулевой ошибке. В слу-. чае неисправности цепи автоподстройки одного из каналов на выходе фазовых детекторов соответствующих каналов появится напряжение, отличающее-, ся от нулевого на величину, большую ±Unop. Блок 12 анализа фазовых оиибок формирует команду о неисправности це-. пи АПФ аварийного канала и транслирует ее на соответствующий вход реша щего блока 11. На другие входы решающего блока с информационных выходов стандарто 2 частоты поступают сигналы, сфор мир ванные на основе внутреннего ангшиза и соответствующие их исправной или н исправной работе. На следующие входы решающего блока 11 поступает информация о величин отклонения i-ro значения частоты стандарта 2 от средней величины, а также исправности вычислителя 9 и блока 10 формирования сигналов упра ления. На основании поступающей информа ции решающий блок формирует команды управления, по которым осуществляется один из вариантов схем соединения .каналов. В качестве примера рассмотрим случай, когда в исходном состоянии сигналы всех трех каналов исправны и ведущим выбран первый канал. Струк тура решающего блока 11 позволяет оператору любой из исправных каналов выбрать в качестве ведущего. В этом случае с выходов решающего блока 11 на управляющие входы коммутатора 6, интеграторов 7 и электронных ключей 8 поступают команды, в резуль тате воздействия которых осуществляется соответствующее соединение канадов. В ведущем (первом) канале замыкается электронный ключ 8, размыкается цепь автоподстройки фазовраща теля 3, а интегратор 7 переходит в режим памяти напряжения. В случае аварии сигнала по третьему каналу смены ведущего канала и перекоммута ции каналов не произойдет, так как по фазе сигнала с третьего канала ни один из сигналов не подстраивается. В случае аварии сигнала по второму к налу произойдет перекоммутация кана,лов. Смены ведущего канала не произойдет, а аварийный канал, становится в конце последовательной цепи автоподстройки фазы. В случае аварии сигналов по второ му -и третьему каналам производится соответствующее соединение каналов Такая логика, заключающаяся в том, что аварийный канал всегда включается в конце последовательной цепи автоподстройки фазы, позволяет произво дить ремонт канала, не ухудшая параметров выходного сигнала. В случае аварии сигнала по ведутце му каналу произойдет смена ведушего канала, а аварийный (в данном случае первый канал) подключается в конце последбвательной цепи автоподстройки Ведущим становится второй канал, интегратор данного канала переходи в режим памяти напряжения, т.е. фиксируется фаза сигнала на момент прихода команды на переключение. Учитывая, то, что фазы сигналов сведены, то при смене Бедуи;,его канала скачка фазы выходного сигнала не произойдет. Аналогично работает логика решающего блока 11 при различных ситуациях с новым ведуц им каналом. Таким образом, при достаточно прос той схеме группового стандарта частоты достигается возможность улучшения долговременной стабильности, сохранения спектральных характеристик стандартов частоты на выходе -устройства и отсутствие скачков фазы сигнала при переключении ведущего канала.. Формула изобретения Групповой стандарт частоты, содержащий три канала, кахсдый из которых состоит из последовательно соеди- ненных стандарта .частоты, фазовращателя и фазового детектора, причем второй вход фазового детектора первого канала соединен с выходом фазовращателя второго канала, второй вход фазового детектора второго канала соединен с выходом фазовращателя третего канала,, а второй вход фазового детектора третьего канала соединен с выходом фазовращателя первого канала, отличающийся тем, что, с целью улучшения долговременной стабильности выходного сигнала, в него введены последовательно соединенные вычислит.ель среднего значения частоты, блок формирования сигналов управления и решающий блок, а также блок анализа фазовых ошибок, при этом сигнальные выходы стандарта частоты каждого из каналов соединены с соответствующими входами вычислителя среднего значения частоты и блока формирования, сигналов управления, выходы которого подключены к управляющему входу стандарта частоты соот-ветст вующего канала, информационные выходы которых соединены со вторыми входами решающего блока, третьи входы которого подключены к соответствующим .выходам блока анализа фазовых сшибок, входы которого соединены с выходами фазовых детекторов каждого из каналов, при этом в каждом из каналов вве/1ены ключ и последовательно соединенные инвертор, коммутатор и интегратор, выход которого соединен с управляющим входом фазовращателя этого же канала, другой вход коммутатора подключен к выходу фазового детектора этого же канала, вход инвертора второго канала соединен с выходом фазового детектора первого кангша, вход инвертора третьего канала соединен с выходом фазового детектора.второго канала, а вход инвертора первого канала соединен с выходом фазового детектора третьего канала,управляющие входы

коммутаторов каждого из .каналов соединены с первыми выходами решающего блока, вторые выходы которого соединены с управляющими входами интегратора и ключа соответствующего канала, причем сиглальный вход ключа каждого из каналов подключен к внходу фаэовращатапя этого же канала, а выходы ключей объединены и являются выходом устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-06-30—Публикация

1979-08-27—Подача