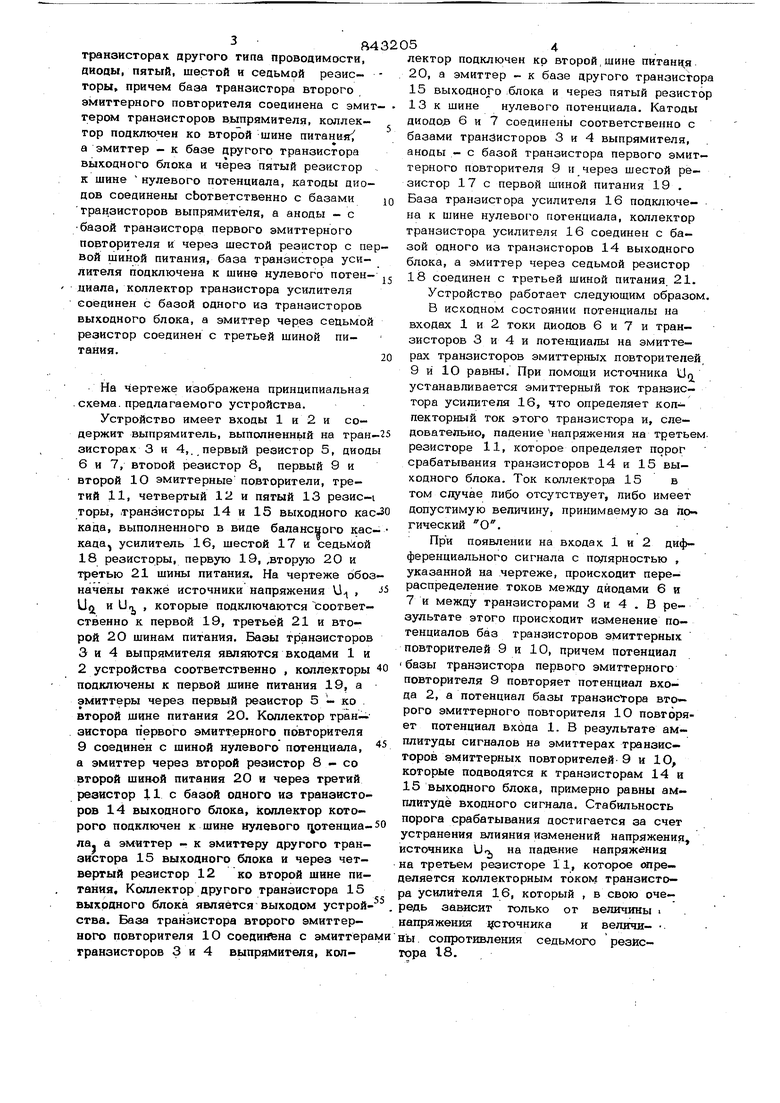

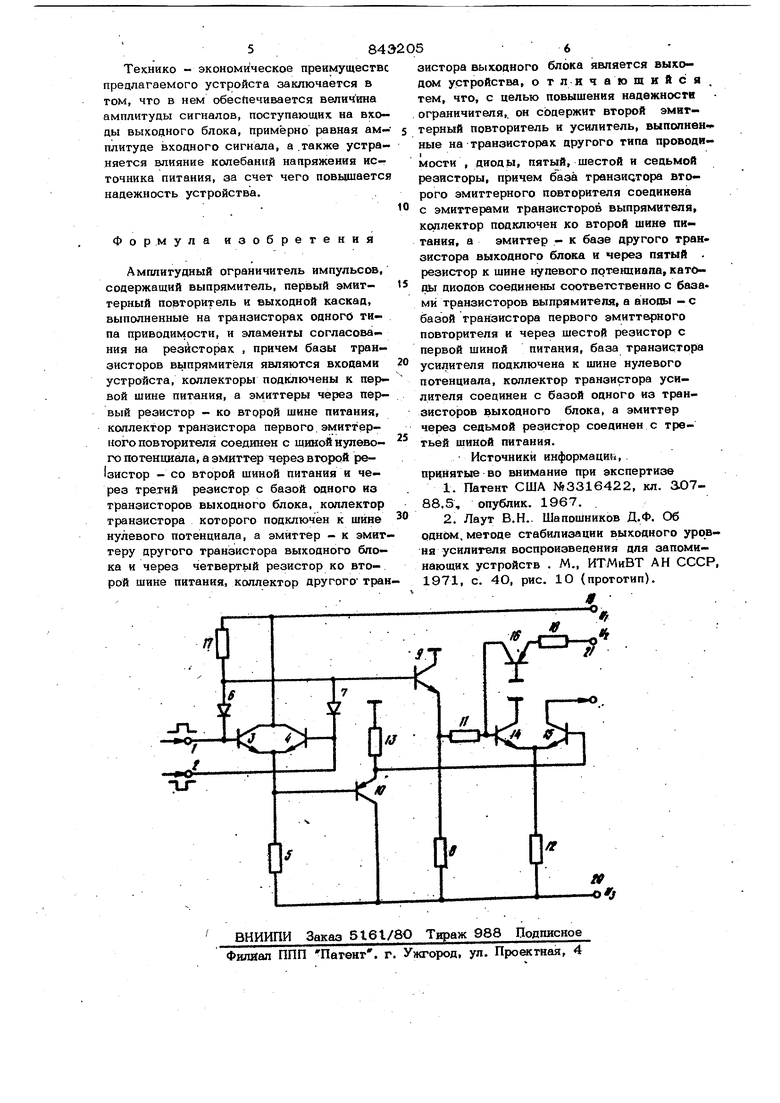

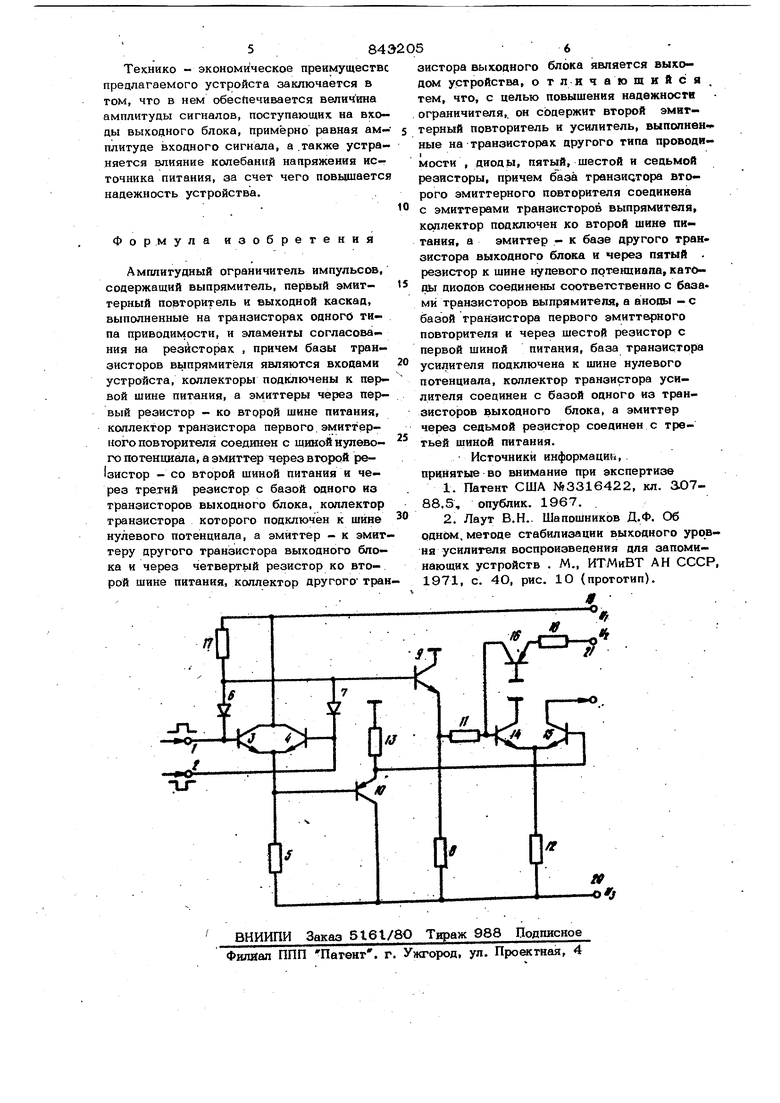

Изобретение относится к импульсной технике и может быть использовано в уси лителях воспроизведения запоминающих , устройств, измерительных усилиях и т.п. Известен амплитудный ограничитель им пульсов, который содержит выпрямитель , балансный каскад и источники напряжения Недостаток . этого устройства - низка надежность. Наиболее близкое к предлагаемому уст ройство, содержащее балансный каскад, соединенный соответствующим образом с выходом выпрямителя, и имеющее регулир мый порог- срабатывания, устанавливаемый внешним источником напряжения С2Х Недостаток известного устройства - низкая надёжность вследствие зависимости порога срабатывания от источника- питания и малая амплитуда сигнала на выходе выгГрямителя. Цель изобретения - повышение надежности устройства.. Поставленная цель достигается тем , что в амплитудный ограничитель импуль-, сов, содержащий выпрямитель, первый эмиттерный повторитель и выходной каскад, выполненные на транзисторах одного типа проводимости, и элементы согласобанн} на резисторах , причем базы транзисторов выпрямителя являются входами устройства, коллекторы подключены к первой шине питания, а эмиттеры через первый резистор - ко второй шине питания, коллектор транзистора первого эмиттерного повторителя соединен с шиной потенциала, а эмиттер через второй резистор - со второй шиной питания и через третий резистор - с базой одного из транзисторов выходного блока, коллектор которого подключен к шине нулевого потенциала, а эмиттер - к эмиттеру другого транзистора выходного блока и через четвертый резистор ко ЕГО- . рой шине питания, коллектор другого транзистора выходного блока является выходом устройства, ввёаены второй эмиттерный повторитель и усилитель, выполненные на транзисторах другого типа проводимости, аиоаы, пятый, шестой и седьмой реаисторы, причем база транзистора второго эмиттерного повторителя соединена с эмит тером транзисторов выпрямителя, коллектор подключен ко второй шине питания а эмиттер - к базе другого транзистора выходного блока и через пятый резистор к шине нулевого потенциала, катоды диодов соединены сЬответственно с базами транзисторов выпрямителя, а аноды - с базой транзистора первого эмиттерного повторителя и через шестой резистор с пе вой шиной питания, база транзистора усилителя подключена к шине нулевого потен- диала, коллектор транзистора усилителя соединен с базой одного из транзисторов выходного блока, а эмиттер через седьмой резистор соединен с третьей шиной питания. На чертеже изображена принципиальная .схема, предлагаемого устройства. Устройство имеет входы 1 и 2 и содержит выпрямитель, выполненный на тран зисторах 3 и 4,. первый резистор 5, диод 6 и 7, ВТОРОЙ резистор 8, первый 9 и второй Ю эмиттерные повторители, третий 11, четвертый 12 и пятый 13 резисторы, транзисторы 14 и 15 выкодного кас када, выполненного в виде балансного кас када, усилитель 16, шестой 17 и седыСюй 18 резисторы, первую 19, ,вторую 20 и третью 21 шины питания. На чертеже обо начены также источники Напряжения U , Uo и Un , которые подключаются Таоответственно к первой 19, третьей 21 и второй 2О шинам питания. Базы транзисторов 3 и 4 выпрямителя являются входами 1 и 2 устройства соответственно , коллекторы подключены к первой шине питания 19, а эмиттеры через первый резистор 5 - ко второй шине питания 20. Коллектор транзистора первого эмиттерного повторителя 9 соединен с шиной нулевого потенциала, а эмиттер через второй резистор 8 - со второй шиной питания 20 и через третий резистор 11с базой одного из транзисторов 14 выходного блока, коллектор которого подключен к шине нулевого цотенциала. а эмиттер - к эмиттеру другого транзистора 15 выходного блока и через четвертый резистор 12 ко второй шине питания. Коллектор другого транзистора 15 выходного блока является выходом устрой ства. База транзистора второго эмиттерного повторителя 1О соединена с эмиттер транзисторов 3 и 4 выпрямителя, коллектор подключен ко второй, шине питани.я 20, а эмиттер - к базе другого транзистора 15 выходноро блока и через пятый резистор 13 к шине нулевого потенциала. Катоды диодов 6 и 7 соединены соответственно с базами транзисторов 3 и 4 выпрямителя, аноды - с базой гранзистора первого эмит- терного повгорителя 9 и через шестой резистор 17 с первой шиной питания 19 . База транзистора усилителя 16 подключена к шине нулевого потенциала, коллектор транзистора усилителя 16 соединен с базой одного из транзисторов 14 выкодного блока, а эмиттер через седьмой резистор 18 соединен с третьей шиной питания. 21. Устройство работает следующим образом. В исходном состоянии потенциалы на входах 1 и 2 токи диодов 6 и 7 и транзистсров 3 и 4 и потенциалы на эмиттерах транзисторов эмиттерных повторителей 9 и 10 равны. При помощи источника UQ устанавливается эмиттерный ток транзистора усилителя 16, что определяет коп- пекторный ток этого транзистора и, следовательно, падение напряжения на третьем, резисторе 11, которое определяет порог срабатывания транзисторов 14 и 15 выходного блока. Ток коллектора 15 в том случае пибо отсутствует, либо имеет допустимую величину, принимаемую за логический О. При появлении на входах 1 и 2 дифференциального сигнала с полярностью , указанной на чертеже, происходит перераспределение токов между диодами 6 и 7 и между транзисторами 3 и 4 . В результате этого происходит изменение потенциалов баз транзисторов эмиттерных повторителей 9 и 10, причем потенциал базы транзистора первого эмиттерного повторителя 9 повторяет потенциал входа 2, а потенциал базы транзистора второго эмиттерного повторителя 10 повторяет потенциал входа 1. В результате амплитуды сигналов на эмиттерах транзисторов эмиттерных повторителей 9 и 1О, которые подводятся к транзисторам 14 и 15 выходного блока, примерно равны амплитуде входного сигнала. Стабильность порога срабатывания достигается за счет устранения влияния изменений напряжения, источника Uoj на паде:ние напряжения на третьем резисторе 11, которое «отре- еляется коллекторным током транзистора усилителя 16, который , в свою очередь зависит только от величины i напряжения д сточника и величи- ньг сопротивления седьмого резИстора 18.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1975 |

|

SU832721A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Устройство коммутации уровней диф-фЕРЕНциАльНОгО СигНАлА | 1979 |

|

SU822364A1 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| ПАРАЛЛЕЛЬНЫЕ АПЕРИОДИЧЕСКИЕ УПЧ | 1993 |

|

RU2118063C1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

Авторы

Даты

1981-06-30—Публикация

1979-10-01—Подача