2, Преобразователь по пЛ о т личающийся тем, что, с целью повьшения быстродействия преобразователя ;, к базе первого ключевого транзистора подключена база четвертого ключевого транзистора,, эмиттер которого соединен с шиной

нулевого потенциала, а коллектор соединен с вторым выходом и через пятый резистор - с эмиттером пятого ключевого транзистора, коллектор которого соединен с шиной питания,

,а база является вторым входом преобразователя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Усилитель считывания | 1986 |

|

SU1368918A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1492381A1 |

| Преобразователь сигналов для усилителя считывания | 1984 |

|

SU1244716A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1508280A1 |

| Усилитель считывания | 1989 |

|

SU1658209A1 |

| Эмиттерно-связанный элемент | 1988 |

|

SU1629985A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Интегральный преобразователь импульсов | 1987 |

|

SU1499449A1 |

1. ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ СИГНАЛА ДЛЯ УСИЛИТЕЛЯ СЧИТЫВАНИЯ, содержащий входной транзистор, включенный JIO схеме эмиттерного повторителя, база которого является входом преобразователя, коллектор соединен с шиной питания, а эмиттер подключен к одному выводу первого резистора, отличающийся тем, что, с целью повьппения надежности и точности преобразования логических уровней в диапазоне рабочих температур и напряжений он содержит ключевые транзисторы и усилительный транзистор, коллектор которого соединен с вторым выводом первого резистора и выходом преобразователя, эмиттер - с шиной нулевого потенциала, а база - с базой первого ключевого транзистора, эмиттером второго ключевого транзистора и через рторой резисторс шиной нулевого потенциала и эмиттером первого ключевого транзистора, коллектор второго ключевого транзистора подключен к шине питания, база - к коллектору первого ключевого транзистора и через третий резистор - к эмиттеру третьего (Л ключевого транзистора, база третьего ключевого транзистора через чет вертьй резистор и коллектор третьего ключевого транзистора подключена к шине питания. О 4i О) О) о J.

Изобретение относргтся к вычислительной технике и может бьпь использовано при создании полупровод никовых интегральньЕС схем иамятн

Известен преобразователь Зфовня сигнала для усилителя считывания, в котором пpи feкeны два эмиттерных повторителя с нагрЗзкой в виде резистивных делителей, ни7кний конец которых через общий диод подключен к шине Земля, резисторы делителей подключенные к эмиттерам транзисторов, защп-ттированные диодами, включенными в обратном направлении 11 ,

Однако известный преобразователь характеризуется высокиг потреблением МОПЩОСТИ5 низкой точностью преобразования логических уровней и низким быстродействием.

Наиболее блр$зким к предлагаемому является преобразователь уровня Сигнала для усиления считывания, содеряшщий два эмиттерных повторителя с нагрузками Б виде резистивных делителей, нюкний конец которык через общий диод подключен к шине Земля zj .

Данное устройство также характеризуется низкой точностью преобразов ния логических уровней j, низким быстродействием и высокой потребляемой мощностью из-за того, что коэффициент передачи резистивных делителей, с помощью которых происходит преобразование уровней, значн™ тельно меньше единицы и сильно зависит от рабочей температуры и напряжения пита;-; ;я..

Цель и:Joбpcтeния - повышение надежности, быстрот,ействия и точности преобразования логических уровней в диапазоне рабочих температур и напряжений.

Указанная цель достигается тем, что преобразователь уровня сигнала для усилителя считывания, содержащий входной транзистор, включенный по схеме эмиттерного повторителя, база которого является входом преобразователя, коллектор соединен с шиной питания, а эмиттер подключен к одному выводу первого резистора, содержит ключевые транзисторы и усилительньй транзистор, коллектор которого соединен с вторым выводом первого резистора и выходом преобразователя, эмиттер - с шиной нулевого потенциала, а база - с базой первого ключевого транзистора, эмиттером второго ключевого транзистора и через второй резистор - с шиной нулевого потенциала и эмиттером первого ключевого транзистора, коллектор второго ключевого транзистора подключен к шине питания, база к коллектору первого ключевого тран зистора и через третий резистор к эмиттеру третьего ключевого транзистора, база третьего ключевого транзистора через четвертый резисто и коллектор третьего ключевого транзистора подключена к шинепитания.

К базе первого ключевого транзистора подключена база четвертого ключевого транзистора, эмиттер которог соединен с шиной нулевого потенциала, а коллектор соединен с вторым выходом и через пятый резистор - с эмиттером пятого ключевого транзистора, коллектор которого соединен с шиной питания, база является вторым входом преобразователя.

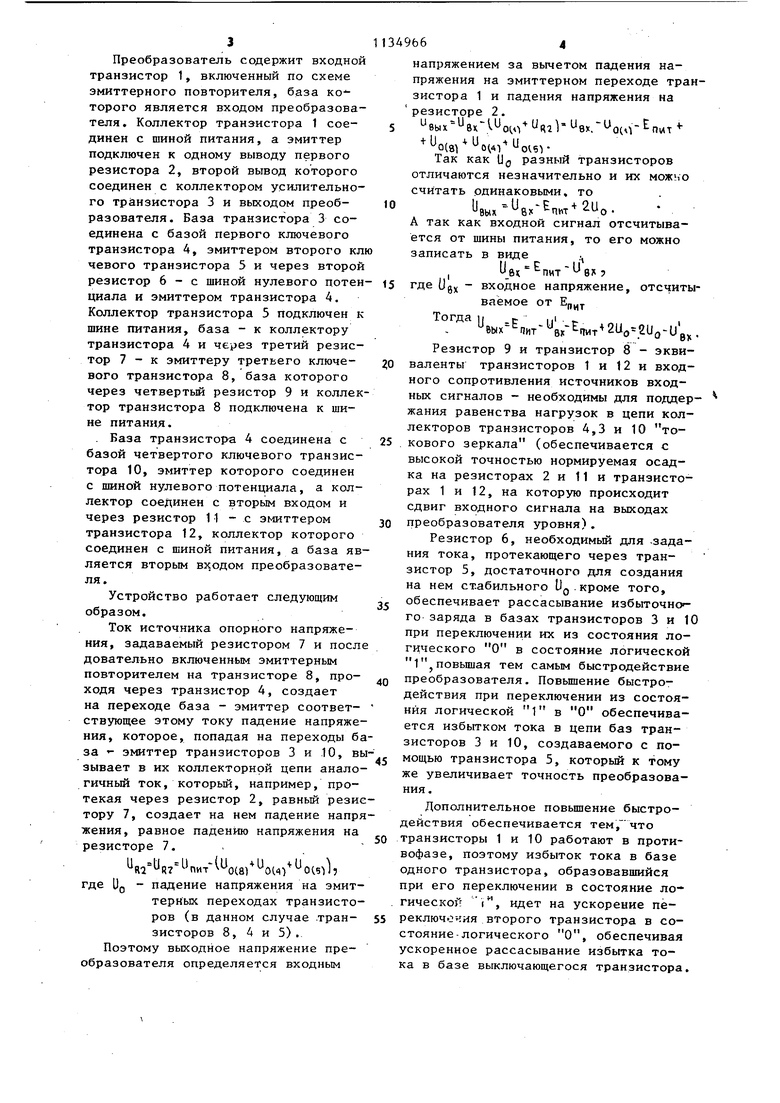

На чертеже приведена принципиальная электрическая схема преобразователя. 3 Преобразователь содержит входной транзистор 1, включенный по схеме эмиттерного повторителя, база которого является входом преобразователя. Коллектор транзистора 1 соединен с шиной питания, а эмиттер подключен к одному выводу первого резистора 2, второй вывод которого соединен с коллектором усилительного транзистора 3 и выходом преобразователя. База транзистора 3 соединена с базой первого ключевого транзистора 4, эмиттером второго кл чевого транзистора 5 и через второй резистор 6 - с шиной нулевого потен циала и эмиттером транзистора 4. Коллектор транзистора 5 подключен к шине питания, база - к коллектору транзистора 4 и через третий резистор 7 - к эмиттеру третьего ключевого транзистора 8, база которого через четвертьш резистор 9 и коллек тор транзистора 8 подключена к шине питания. . База транзистора 4 соединена с базой четвертого ключевого транзистора 10, эмиттер которого соединен с шиной нулевого потенциала, а коллектор соединен с вторьм входом и через резистор 11 - с эмиттером транзистора 12, коллектор которого соединен с шиной питания, а база яв ляется вторым входом преобразователя. Устройство работает следующим образом. Ток источника опорного напряжения, задаваемый резистором 7 и посл довательно включенным эмиттерным повторителем на транзисторе 8, проходя через транзистор 4, создает на переходе база - эмиттер соответствующее этому току падение напряже ния, которое, попадая на переходы б за - эмиттер транзисторов 3 и 10, в зывает в их коллекторной цепи анало гичный ток, который, например, протекая через резистор 2, равный рези тору 7, создает на нем падение напр жения, равное падению напряжения на резисторе 7. . (в))(5-)l5 где DO - падение напряжения на эмит терных переходах транзисто ров (в данном случае транзисторов 8, 4 и 5). Поэтому выходное напряжение преобразователя определяется входным 664 напряжением за вычетом падения напряжения на эмиттерном переходе транзистора 1 и падения напряжения на резисторе 2. ebix Ue -Wow U il-Ug, (,,,.U,,. Так как UQ разный транзисторов отличаются незначительно и их можно считать одинаковыми, то ивы.- вГЕпит 2ио. А так как входной сигнал отсчитывается от шины питания, то его можно записать в виде .., ЕПИТ в 7 где (Jgj( входное напряжение, отсчитываемое от Ер Тогда II t 1| . Bb.гEпит-V тит 2U 2Uo-u;,. Резистор 9 и транзистор 8 - эквиваленты транзисторов 1 и 12 и входного сопротивления источников входных сигналов - необходимы для подцержания равенства нагрузок в цепи коллекторов транзисторов 4,3 и 10 токового зеркала (обеспечивается с высокой точностью нормируемая осадка на резисторах 2 и 11 и транзисторах 1 и 12, на которую происходит сдвиг входного сигнала на выходах преобразователя уровня). Резистор 6, необходимый для -задания тока, протекающего через транзистор 5, достаточного для создания на нем стабильного Ug.кроме того, обеспечивает рассасывание избыточно го заряда в базах транзисторов 3 и 10 при переключении их из состояния логического О в состояние логической 1,повьш1ая тем самым быстродействие преобразователя. Повьш1ение быстродействия при переключении из состояния логической 1 в О обеспечивается избытком тока в цепи баз транзисторов 3 и 10, создаваемого с помощью транзистора 5, который к тому же увеличивает точность преобразования. Дополнительное повьш1ение быстроействия обеспечивается тем,что ранзисторы 1 и 10 работают в противофазе, поэтому избыток тока в базе дного транзистора, образовавшийся ри его переключении в состояние логической ( , идет на ускорение пееключочия второго транзистора в сотояние-логического О, обеспечивая скоренное рассасывание избытка тоа в базе выключающегося транзистора.

Логические уровни выходного напряжения преобразователя уровня не зависят от температуры и напряжения источника питания и однозначно, без ослабления повторяют входные логические уровни на фоне добавки 2 UQ, которая необходима для создания оптимальных режимов работы следующих каскадов ИС, обеспечивая тем самым высокую точность преобразования.

Высокая точность преобразования позволяет значительно снизить уровни логического перепада на входе и выходе преобразователя, тем самым значительно снижая время перезаряда паразитных емкостей на входе и выходе, что значительно повышает его быстродействие. Кроме того, высокие точность преобразования и быстродействие позволяют в ряде случаев снизить токи, протекающие в плечах

преобразователя, а иногда и совсем исключить второе плечо вместе с вторым входом и выходом, что снижает потребляемую преобразователем мощность.

Использование источника опорного напряжения с токозадающим элементом, эквивалентньм нагрузке в цепи

источников тока, включенных как токовое зеркало, выгодно отличает предлагаемый преобразователь уровня, так как повышена точность преобразования, устранена зависимость преобразованных уровней от изменения напряжения источника питания и рабочей температуры, повышено быстродействие и снижена потребляемая мощность, что существенно упрощает построение на

его основе высоконадежных, помехоустойчивых и быстродействующих ИС с малой потребляемой мощнос| сью

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

Авторы

Даты

1985-01-15—Публикация

1983-04-11—Подача