(54) УСТРОЙСТВО СРАВНЕНИЯ ФАЗ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик импульсов | 1982 |

|

SU1042185A1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693321C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| D-ТРИГГЕР С САМОСИНХРОННОЙ ПРЕДУСТАНОВКОЙ | 2006 |

|

RU2319297C1 |

| Аналого-цифровой преобразователь последовательного приближения | 1987 |

|

SU1499496A1 |

| Устройство для измерения отношения двух напряжений | 1984 |

|

SU1226323A1 |

| Устройство для определения экстремума | 1988 |

|

SU1603341A1 |

| Устройство выделения сейсмических сигналов | 1982 |

|

SU1049781A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

Изобретение относится к автоматике и может быть использовано для авт матического определения направления вращения или движения объекта, например, в устройстве измерения длины движущейся заготовки сравниванием фаз импульсных сигналов, поступающих на его вход. Известно устройство сравнения последов тельности поступления импульс ных сигналов, используемое для определения направления движения, содержащее четыре триггера, тактовые входы попарно соединены с тактовьми вхо дами устройства, входы которого через RC-цепочки соединены с D-входами триггеров . Известно также устройство сравнения фаз сигналов, содержащее первый, второй, третий и четвертый триггеры и инвертор, вход которого соединен с первым входом устройства 2 . Недостаток этих устройств - относительно низкая достоверность функционирования. Цель изобретения- повышение досто- верности функционирования. Поставленная цель достигается тем что устройство сравнения фаз сигналов содержащее первый, второй, третий и четвертый триггеры и инвертор, вход которого соединен с первым входом устройства, введены первый ,. второй, третий и четвертый дополнительные инверторы, первый, второй, третий, четвертый и пятый элементы И-НЕ, пятый триггер, элемент И-ИЛИ НЕ, выход которого соединен с входами первого и второго элементов И-НЕ и входом первого дополнительного инвертора, выход которого соединен с первыми входами третьего и четвертого элементов И-НЕ, вторые входы которых соединены с выходами пятого триггера, входы которого соединены с выходами первого и второго элементов И-НЕ, вы38

ход инвертора соединен с тактовым входом третьего и D-входом четвертого триггеров и второго дополнительного инвертора, выход которого соединен с тактовым входом первого и D-BXOдом второго триггеров, второй вход устройства соединен с входом третьего дополнительного инвертора, вьпсод которого соединен с D-входом первого и тактовым входом четвертого триггеров и входом четвертого дополнительного инвертора, выход которого соединен с тактовым входом второго и D-входом третьего триггера, прямой выход первого триггера соединен с входом первого элемента И-НЕ и первым входом первой группы входов по И элемента И-ИЛИ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным выходом четвертого триггера, прямой выход которого соединен с входом первого элемента И-НЕ и первым входом второй группы входов по И элемента И-ИЛИ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным выходом третьего триггера, прямой выход которого со единен с входом первого элемента И-НЕ и первым входом третьей группы входов по И элемента И-ИЛИ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным выходом второго триггера, прямой выход которого соединен с входом первого элемента И-НЕ и первым входом четвертой группы входов И элемента И-ИЛИ-НЕ, второй вход которой соединен с инверсным выходом первого три1- гера и входом второго элемента И-НЕ, инверсные входы сброса первого, второго, третьего и четвертого триггеров соединены с выходом третьего элемента И-НЕ и первым входом пятого элемента И-НЕ, второй вход которого соединен с выходом четвертого элемента И-НЕ и инверсными входами установки первого, второго, третьего и четвертого триггеров.

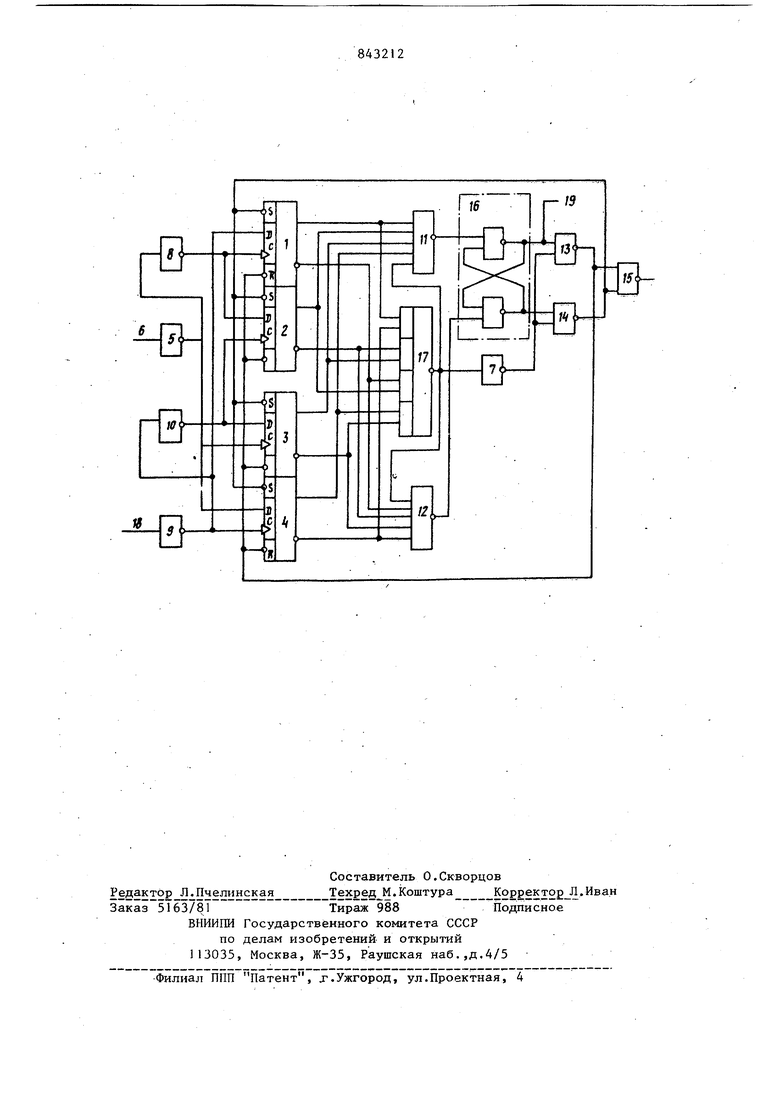

На чертеже показана структурная схема устройства сравнения фаз сигНалов.

. Устройство сравнения фаз сигналов содержит первый 1, второй 2, третий3 и четвертый 4 триггеры и инвертор 5, выход которого соединен с первым входом 6 устройства, а также первый 7, второй 8, третий 9 и четвертый 10 дополнительные инверторы, первый 11,

24

второй 12, третий 13, четвертый 14, пятый 15 элементы И-НЕ, пятый тригг&р 1 6, элементы И-И.ПИ-НЕ 1 7, выход которого соединен с входами первого 11 и второго 12 элементов И-НЕ и входом первого дополнительного инвертора 7, выход которого соединен с первыми входами третьего 13 и четвертого 14 элементов И-НЕ, вторые входы которых соединены с выходами пятого триггера 16, входы которого соединены с выходами первого 11 и второго 12 элементов И-НЕ, выход инвертора 5 соединен с тактовым входом третьего. 3 и входом четвертого 4 триггеров и второго дополнительного инвертора 8, выход которого соединен с тактовым входом первого 1 и D-входом второго 2 триггеров, второй вход 18 устройства соединен с входом третьего дополнительного инвертора 9, вы-, ход которого соединен с D-входом перйЪго 1 и тактовым входом четвертого 4 триггеров и входом четвертого дополнительного инвертора 10, выход которого соединен с тактовым входом второго 2 и D-входом третьего 3 триггера, прямой выход nepBoio триггера 2 соединен с входом первого элемента И-НЕ 11 и первым входом первой группы входов по И элемента И-ИЛИ-НЕ 17, второй вход которой соединен с входом второго элемента И-НЕ 12 и инверсным выходом четвертого триггера 4, прямой выход которого соединен с входом первого элемента И-НЕ 1 и первым входом второй группы входов по И элемента И-ИЛИ-НЕ 17, второй, вход которой соединен с входом втрого элемента И-НЕ и инверсным выходом третьего триггера 3, прямой выход которого соединен с входом первого элемента И-НЕ 11 и первым входом третьей группы входов по И элемента И-ИЛИ-НЕ I7, второй вход которой соединен с входом второго элемента И-НЕ 12 и инверсным выходом второго триггера 2, прямой выход которого соединен.с входом первого элемента И-НЕ 11 и первым входом четвертой группы входов по И элемента И-ИЛИ-НЕ 17, второй вход которой соединен с инверсным выходом первого триггера 1 и входом второго элемента И-НЕ 12, инверсные входы сброса первого 1, второго 2, третьего 3 и четвертого 4 триггеров соединены с выходом третьего элемента И-НЕ 13 и первым входом пятого элемента И-НЕ 15, второй вход которого соединен с выходом четверто го элемента И-НЕ 14 и инверсными вхо дами установки первого 1, второго 2, третьего 3 и четвертого 4 триггеров. Устройство работает следующим образом. С подачей напряжения устройство з нимает только одно состояние из двух устойчивых: либо все триггеры 1 - 4 и триггер 16 взведены, что соответст вует индикации движения вперед, при этом на выходе 19 устройства имеется сигнал логической единицы; либо все они сброшены, и индицируется движение назад, а на выходе 19 устройства присутствует логический ноль. Пример 1. Триггеры 1 - 4 взведены, а триггер 16 сброшен. На выходе элемента И-НЕ появляется логический нуль, а на выходе элемента И-НЕ 12 сохраняется логическая едини ца, которые поступая на входы триггера 16 возводят его, т.е. устройство перейдет в устойчивое состояние П р и м е р 2. Все триггеры 1-4 сброшены, а триггер 16 взведен. На выходе элемента И-НЕ 1 Т сохраняется логическая единица, а на выходе элемента И-НЕ 12 появляется логический нуль, который поступая на входы триггера 16 с раздельными входами сбрасывают его, т.е. устройство также переходит в устойчивое состояние. Если состояние хотя бы одного из триггеров 1 - 4 отличается от состояния других триггеров, на выходе элемента И-ИЛИ-НЕ 17 появляется логический нуль. В зависимости от состояния тригг ера 16 возможны два варианта перехода в устойчивое состояниеП р и м .е р 3. Триггер 16 взведен На выходе элемента И-НЕ присутствует логический нуль, который, поступая на входы установки в единицу всех триггеров 1 - 4, взводит их. После взведения всех триггеров 1 - 4 на выходе элемента Й-ИЛИ-НЕ 17 и на вы. ходе элемента И-НЕ 13 появляется еди,ница, т.е. устройство переходит в устойчивое состояние. П р и м е р 4. Триггер 16 сброшен На выходе элемента И-НЕ 14 присутствует логический нуль, который, поступая на входы установки в ноль всех триггеров 1-4, сбрасывает их, на выходе элемента И-ИЛИ-НЕ 17 и на выходе Элемента И-НЕ. 14 появляется ло826 . гическая единица, т.е. устройство переходит в устойчивое состояние. Если устройство находится в состоянии индикации движения вперед, и сигнал на выходах 6 и 18 начинает изменяться соответственно движению вперед, устройство сохраняет свое состоят ние. При смене направления движения по приходу превого же фронта выходного сигнала на выходы 6 и 18 сбрасывается один из триггеров 1-4, что -приводит к появлению сигнала Логический нуль на выходе элемента И-ИЛИНЕ 17 и на выходе элемента И-НЕ 13, который поступая на входы установки в ноль всех триггеров 1 - 4 сбрасывает их.. Сброс в ноль всех триггеров 1- 4 приводит к пропаданию логического нуля на выходе элемента .И-ИЛИ-НЕ 17, смене логического нуля на выходе элемента И-НЕ 13 на логическую единицу и к сбросу триггера 16. В результате устройство переходит в устойчивое состояние индикации движения назад, которое сохраняется при сохранении направления движения и остановке. Если устройство находится в состоянии индикации движения назад, и направление движения изменяется, то по приходу первого же фронта входного сигнала, соответствующего движению вперед, на входы 6 и 18 сбрасывается один из триггеров 1-4, что приводит к появлению логического нуля на выходе элемента И-ИЛИ-НЕ 17 и на выходе элемента И-НЕ 14, который поступая на входы установки в единицу всех триггеров J - 4, возводит их. Логический нуль на выходе элемента И-ИЛИ-НЕ 17 сменяется на логическую единицу, на выходе элемента 11 появляется логический нуль при сохранении логической единицы на выходе элемента И-НЕ 12, что приводит к взведению триггера 16. Устройство переходит в устойчивое состояние индикации движения вперед, которое сохраняется при сохранении направления движения и остановке. В предлагаемом устройстве для определения направления движения осуществляют индикацию потери его работоспособности при отказе хотя бы одного из триггеров 1-4, подключая входы элемента И-НЕ I5 к выходам элементов И-НЕ 13 и 14. При выходе из строя хотя бы одного из триггеров 1 - 4 устройство переходит в новое 78 возникающее в случае изменения направ ления движения устойчивое состояние когда при любом изменении сигнала на выходах 6 и 18, на выходах одного из элементов И-НЕ 13 и 14 сохраняется логический нуль, поступающий либо на входы установки в ноль, либо на входы установки в единицу триггеров 1 - 4 и не позволяющий триггерам 1 - 4 изменить свое состояние. Сохранение этого сигнала во времени приводит к появлению логической единицы на выход элемента И-НЕ 14 и к срабатыванию индикатора неработоспособности устройства для опред,еления направления движения. Формула изобретения Устройство сравнения фаз сигналов содержащее первый, второй, третий и четвертьй триггеры и инвертор, вход которого соединен с первым входом устройства, о т л и ч ающееся тем, что, с целью повышения достоверности функционирования, в него введены первый, второй, третий и четвертый дополнительные инверторы, первый, вто рой, третий, четвертый и пятый элементы И-НЕ, пятый триггер, элемент И-ИЛИ-НЕ, выход которого соединен с входами первого и второго элементов И-НЕ и входом первого дополнительного инвертора, выход которого соедийен с первыми входами третьего и четвертого элементов И-НЕ, вторые входы которых соединены с выходами, пятого триггера, входы которого соединены с выходами первого и второго элементов И-НЕ, выход инвертора соединен с тактовымвходом третьего и D-входом четвертого триггеров и второго дополнительного инвертора, выход которого соединен с тактовым входом первого и D-входом второго триггеров, второй вход устройства соединен с входом третьего дополнительного инвертора. 8 выход которого соединен с О-входом первого и тактовым входом четвертого триггеров и входом четвертого дополнительного инвертора, выход которого соединен с тактовым входом второго и D-входом третьего триппера, прямой выход первого триггер.а соединен с входом первого элемента И-НЕ и первым входом первой группы входов по И элемента И-ИЛИ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным вьЬсодом четвертого триггера, прямой выхЬд которого соединен с входом первого элемента И-НЕ и первым входом второй группы входов по И элемента И-ИЛИ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным выходом третьего триггера, прямой выход которого соединен с входом перво-. го элемента И-НЕ и первым входом третьей группы входов по И элемента И-ШШ-НЕ, второй вход которой соединен с входом второго элемента И-НЕ и инверсным выходом второго триггера, прямой выход которого соединен с входом первого элемента И-НЕ и первым . ; входом четвертой .группы входов .по И элемента И-ИЛИ-НЕ, второй вход которой соединен с инверсным выходом первого триггера и входом второго элемента И-НЕ., инверсные входы сброса первого, второго, третьего и четвертого триггеров соединены с выходом третьего элемента И-НЕ и первым входом пятого элемента И-НЕ, второй вход которого соединен с выходом четвертого элемента И-НЕ и инверсными входами установки первого, второго, третьего и четвертого триггеров. Источники информации, принятые во внимание, при экспертизе 1.Патент ФРГ № 2007072, кло Н 03 К 21/00, 1970. 2.Авторское свидетельсвто СССР № 406312, кл. Н 03 К 5/18, 1971 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-08-17—Подача