(54) ЯЧЕЙКА КОРРЕЛЯТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый фильтр-коррелятор | 1979 |

|

SU824409A1 |

| Интегральный программируемый фильтр | 1980 |

|

SU1005273A1 |

| Активный фильтр на коммутируемых конденсаторах | 1986 |

|

SU1381690A1 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| Емкостное накопительное устройство | 1975 |

|

SU555540A1 |

| Устройство выборки и хранения информации | 1976 |

|

SU746729A1 |

| Усилитель считывания | 1978 |

|

SU834764A1 |

| Емкостное накопительное устройство | 1973 |

|

SU500580A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Фазовый детектор | 1980 |

|

SU949772A1 |

1

Изобретение относится к электронной технике, в частности к устройствам обработки сигналов и может использоваться в каналах связи, в радио- и гидролокационной аппаратуре и т.п..

Известна ячейка прибора с зарядовой связью для обработки сигнала 1.

Однако эта ячейка не обладает дифференциальным выходом.

Известна ячейка коррелятора, содержащая первую шину смещения, первую и вторую выходные шины суммирования, первый и второй управляющие транзисторы, входы управления, нагрузочный и измерительные транзисторы 2.

Недостатком этой ячейки является большой уровень нелинейных искажений.

Цель изобретения - уменьшение нелинейных искажений устройства.

Поставленная цель достигается тем, что в ячейку коррелятора, содержащую первую шину смешения, первую и вторую выходные шины суммирования, первый и второй управляющие транзисторы, затворы которых подключены к противофазным входам управления, последовательно включенные нагрузочный и измерительный транзисторы, затвор измерительного транзистора подключен к выходной шине, дополнительно введены запо минающий конденсатор, вторая шина смешения, коммутирующий и стробирующий транзисторы, при этом стоки измерительного и нагрузочного транзисторов подключены соответственно к первой и второй шине смещения, истоки измерительного и нагрузочного транзисторов соединены со стоком коммутирующего транзистора, исток которого подключен к первой обкладке запоминающего конденсатора и стоку стробирующего транзистора, сток которого подсоединен к стокам первого и второго управляющих транзисторов, истоки которых соответственно соединены с первой и второй выходными шинами суммирования с щиной смещения.

Кроме того, в устройство вторая обкладка конденсатора может быть подключена к первой шине смешения.

Вторая обкладка конденсатора может JJ быть подключена ко второй шине смещения.

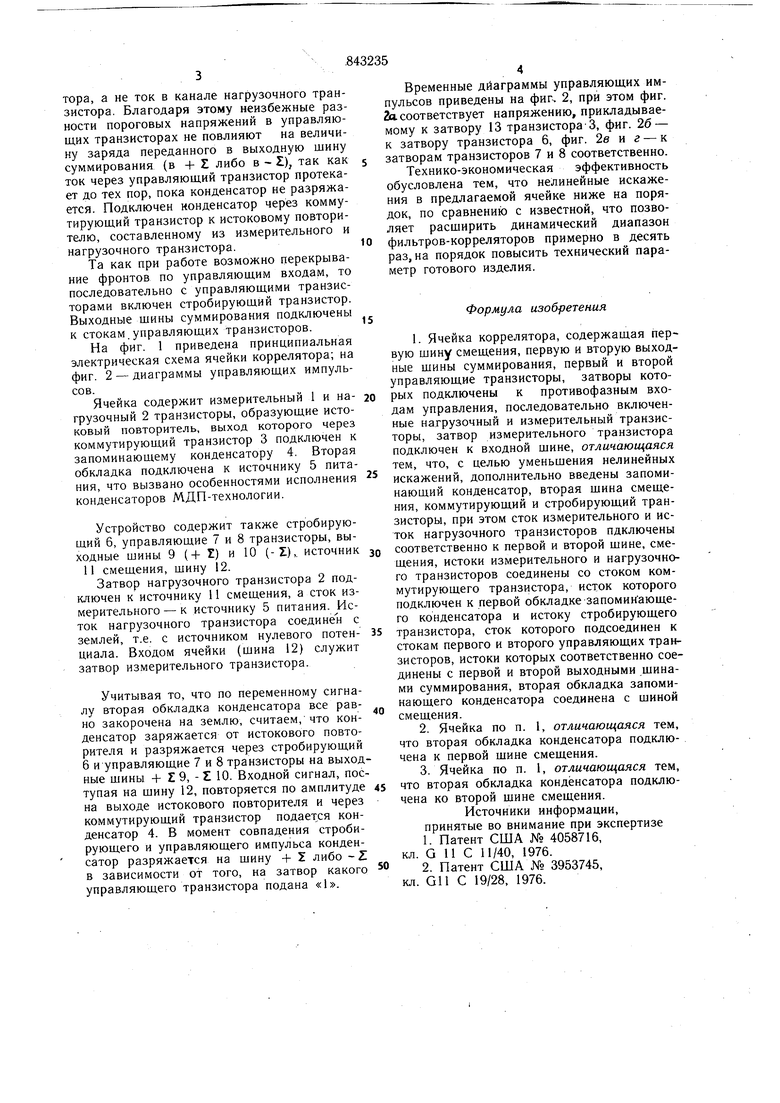

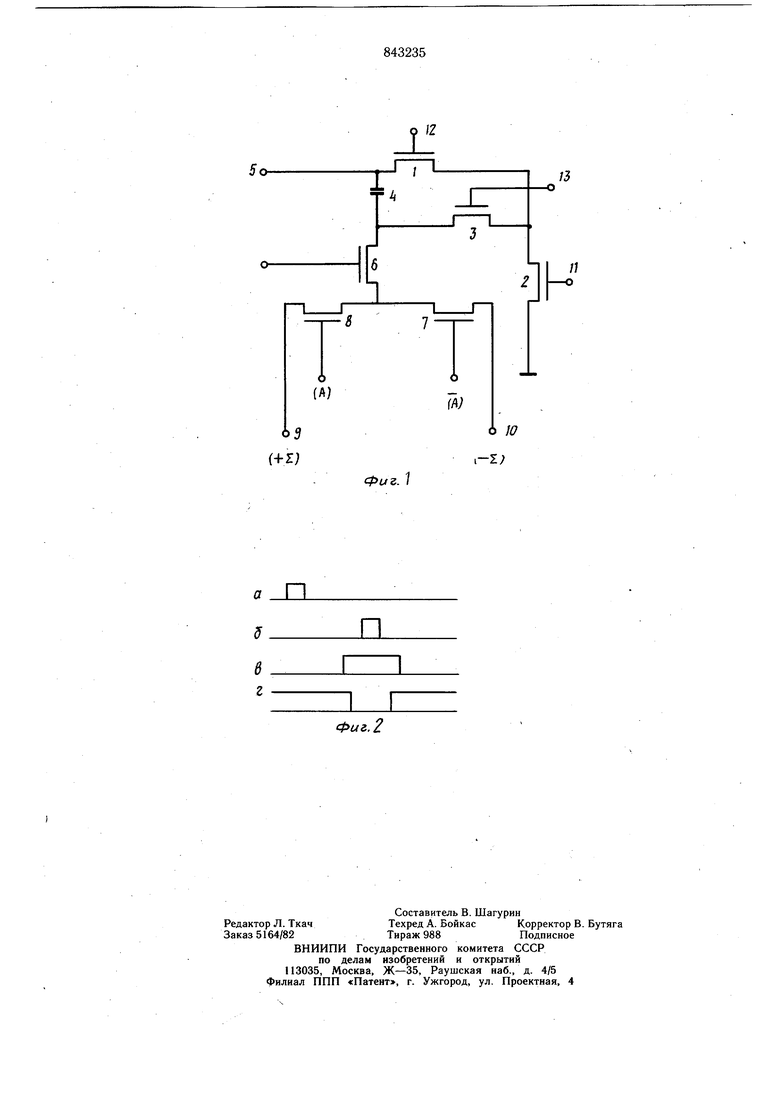

Введение запоминающего конденсатора приводит к тому, что информационным параметром ячейки ставится заряд конденсатора, а не ток в канале нагрузочного транзистора. Благодаря этому неизбежные разности пороговых напряжений в управляющих транзисторах не повлияют на величину заряда переданного в выходную шину суммирования (в + Z либо в - Z), так как ток через управляющий транзистор протекает до тех пор, пока конденсатор не разряжается. Подключен конденсатор через коммутирующий транзистор к истоковому повторителю, составленному из измерительного и нагрузочного транзистора. Та как при работе возможно перекрывание фронтов по управляющим входам, то последовательно с управляющими транзисторами включен стробирующий транзистор. Выходные щины суммирования подключены к стокам.управляющих транзисторов. На фиг. 1 приведена принципиальная электрическая схема ячейки коррелятора; на фиг. 2 - диаграммы управляющих импульсов. Ячейка содержит измерительный 1 и нагрузочный 2 транзисторы, образующие истоковый повторитель, выход которого через коммутирующий транзистор 3 подключен к запоминающему конденсатору 4. Вторая обкладка подключена к источнику 5 питания, что вызвано особенностями исполнения конденсаторов МДП-технологии. Устройство содержит также стробирующий 6, управляющие 7 и 8 транзисторы, выходные шины 9 (-Ь I) и 10 (-Z),. источник 11 смещения, шину 12. Затвор нагрузочного транзистора 2 подключен к источнику 11 смещения, а сток измерительного - к источнику 5 питания. Исток нагрузочного транзистора соединен с землей, т.е. с источником нулевого потенциала. Входом ячейки (шина 12) служит затвор измерительного транзистора. Учитывая то, что по переменному сигналу вторая обкладка конденсатора все равно закорочена на землю, считаем, что конденсатор заряжается от истокового повторителя и разряжается через стробирующий 6 исправляющие 7 и 8 транзисторы на выход ные щины 4- 19, -Z 10. Входной сигнал, поступая на щину 12, повторяется по амплитуде на выходе истокового повторителя и через коммутирующий транзистор подаехся конденсатор 4. В момент совпадения стробирующего и управляющего импульса конденсатор разряжается на шину -f 2 либо - Z. в зависимости от того, на затвор какого управляющего транзистора подана «1. Временные диаграммы управляющих импульсов приведены на фиг, 2, при этом фиг. 2а. соответствует напряжению, прикладываемому к затвору 13 транзистора-3, фиг. 26- к затвору транзистора 6, фиг. 2в и г - к затворам транзисторов 7 и 8 соответственно. Технико-экономическая эффективность обусловлена тем, что нелинейные искажения в предлагаемой ячейке ниже на порядок, по сравнению с известной, что позволяет расщирить динамический диапазон фильтров-корреляторов примерно в десять раз, на порядок повысить технический параметр готового изделия. Формула изобретения 1.Ячейка коррелятора, содержащая первую шину смещения, первую и вторую выходные шины суммирования, первый и второй управляющие транзисторы, затворы которых подключены к противофазным входам управления, последовательно включенные нагрузочный и измерительный транзисторы, затвор измерительного транзистора подключен к входной шине, отличающаяся тем, что, с целью уменьшения нелинейных искажений, дополнительно введены запоминающий конденсатор, вторая щина смещения, коммутирующий и стробирующий транзисторы, при этом сток измерительного и исток нагрузочного транзисторов пдключены соответственно к первой и второй щине, смещения, истоки измерительного и нагрузочного транзисторов соединены со стоком коммутирующего транзистора, исток которого подключен к первой обкладке запоминающего конденсатора и истоку стробирующего транзистора, сток которого подсоединен к стокам первого и второго управляющих транзисторов, истоки которых соответственно соединены с первой и второй выходными щинами суммирования, вторая обкладка запоминающего конденсатора соединена с шиной смещения. 2.Ячейка по п. 1, отличающаяся тем, что вторая обкладка конденсатора подключена к первой щине смещения. 3.Ячейка по п. 1, отличающаяся тем, что вторая обкладка конденсатора подключена ко второй щине смещения. Источники информации, принятые во внимание при экспертизе 1.Патент США № 4058716, кл. G 11 С 11/40, 1976. 2.Патент США № 3953745, кл. G11 С 19/28, 1976.

5о73

о

(А)

65

(+i;

а

5

фиг. 2

6 Ю

1-1;

фиг. 1

Авторы

Даты

1981-06-30—Публикация

1979-05-07—Подача