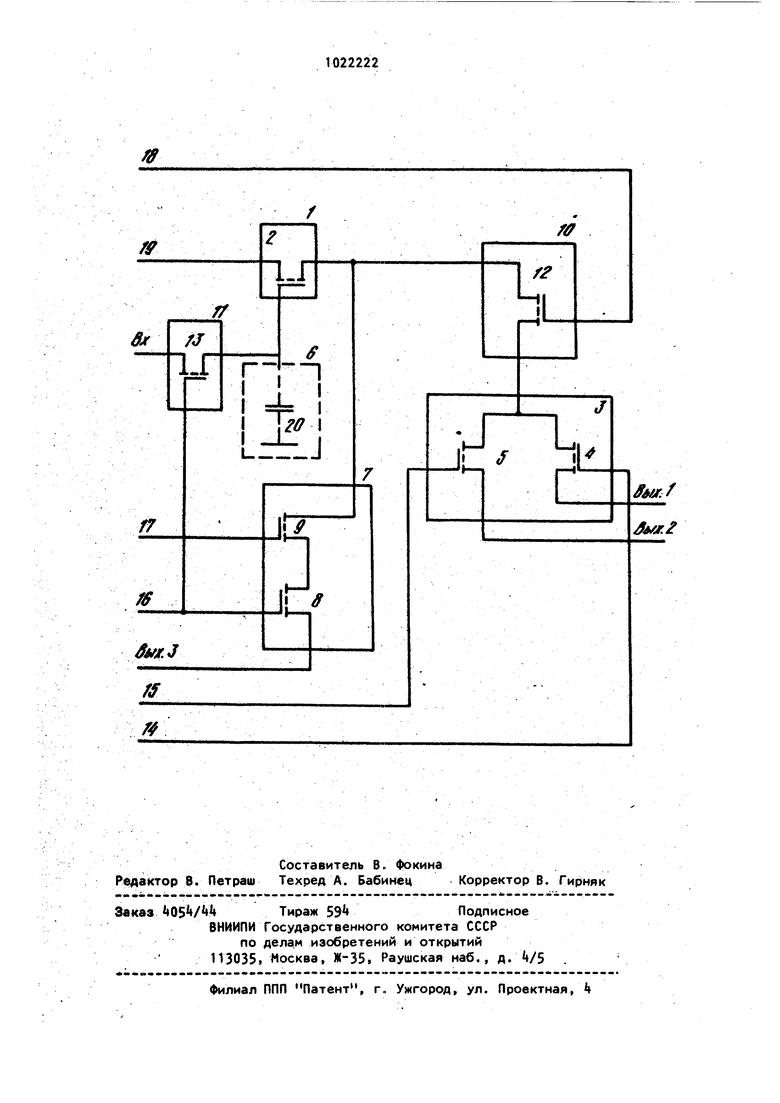

Изобретение относится к вычисли тельной технике, в частности к устройствам обработки сигналов, и может быть использовано в интегральных, программируемых фильтрах сигналов. Известна ячейка памяти сигналов, содержащая операционный усилитель, запоминающие и компенсирующие конденсаторы и выходной истоковый повт ритель 3 . Недостатком ячейки является боль шая потребляемая мощность и разброс уровня постоянной составляющей выход ного сигнала в зависимости от велич ны порогового напряжения выходного транзистора в истоковом повторителе что исключает возможность ее исполь зования в программируемых фильтрах. Известна ячейка памяти для трансверсального фильтра, которая содержит электрод ввода зарядов, области для хранения зарядов, а также электроды для разделения зарядового пакета на две части 2 . К недостаткам ячейки относится низкая точность, вызванная нелинейным вводом зарядового пакета, неэффективностью переноса и нелинейным характером считывания сигнала, а так же то, что коэффициент передачи зафиксирован и не может быть nepenpo граммирован. Поэтому ячейка может быть использована только в трансверсальных фильтрах с жесткой программой. Наиболее близкой по технической сущности к предлагаемой является ячейка памяти для программируемого фильтра сигналов, содержащая преобразователь напряжение - ток, выпол ненный на первом МДП-транзисторе, сток которого соединен с шиной питания. Кроме того, устройство содержит переключатель тока, выполненный на втором и третьем МДП-транзисторах затворы которых соединены соответственно с первой и второй шинами управ ления , .причем стоки второго и третьего МДП-транзисторов являются первым и вторым выходами ячейки памяти. Устройство содержит также накопитель ный элемент, например конденсатор, образованный затвором первого МДПтранзистора, и шины стробирования зЗ . Недостатком известной ячейки памя ти является низкая точность и большая потреблаемая мощность. Низкая точность ячейки обусловлена тем, что нагрузкой первого МДП-транзистора является нелинейный резистор, выполненный на нагрузочном МДП-транзисто-, ре с высоким внутренним сопротивлением. В результате этого в выходном токе ячейки содержится большой уровень ( до 8) второй гармоники, что снижает точность ячейки. Большой уровень потребляемой мощности вызван тем, чуо цепь считывания информации содержит три МДП-транзистора: с большим Z, средним Z и малым Т. , где 1 отношение ширины к длине МДП-транзистора. Поэтому, если ток покоя ячейки составляет 100 мкА, то для обеспе ения динамического диапазона дБ напряжение питания должно составлять не менее 12 В, откуда следует, что потребляемая мощность составляет 1,2 мВт, т.е. недопустимо много. Цель изобретения - повышение точности ячейки памяти и уменьшение потребляемой мощности. Поставленная цель достигается тем, что в ячейку памяти, содержащую преобразователь напряжение - ток, выполненный на первом МДП-транзисторе, сток которого соединен с шиной питания , переключатель тока, выполненный на втором и третьем МДП-транзисторах, затворы которых соединены соответственно с первой и второй шинами управления, стоки второго и третьего МДП-транзисторов являются первым и вторым выходами ячейки па мяти, накопительный элемент, выполненный на конденсаторе, образованном затвбром первого МДП-транзистора и шиной нулевого потенциала, и шины напряжения стробирования, введены коммутатор, выполненный на четвертом и пятом МДП-транзисторах, первый и второй ключи, выполненные на шестом и седьмом МДП-транзисторах, причем затворы четвертого и пятого МДП-транэисторов соединены соответственно с первой и второй шинами напряжения стробирования, исток четвертого МДПтранэистора соединен с истоком пятого МДП-транзистора, сток которого соединен с истоком первого и со стоком шестого МДП-транзисторов, сток ,четверт9го МДП-транзистора является третьим выходом ячейки памяти, исток шестого МДП-транзистора соединен с истоками второго и третьего МДП-транзисторов, затвор шестого МДП-транзистора соединен с третьей шиной напряжения стробирования, исток седьмого МДП-транзистора является входом ячей ки памяти, затвор седьмого НДП-транзистора соединен с первой шиной напряжения стробирования, сток седьмого МДП-транзистора соединен с затвором первого МДП-транзистора. На чертеже изображена электрическая схема предлагаемой ячейки памяти Ячейка содержит преобразователь 1 напряжение - ток, выполненный на МДП-транзисторе 2, переключатель 3 тока, выполненный на НДП-транзистора и 5, накопительный элемент, выполненный на конденсаторе .6, коммута тор 7, выполненный на МДП-транзисто pax 8 и 9 ключи 10 и 11, выполненны на МДП-транзисторах 12 и 13, шины I и 15 управления, шины 16 - 18 напряжения стробирования, шину 19 питания шину 20 нулевого потенциала. Ячейка памяти функционирует следующим образом. Работа ячейки памяти состоит из трех этапов. На первом этапе осуществляется запись аналогового сигнала в ячейку памяти, на втором-хранение на третьем - считывание. Запись сигнала осуществляется подачей строба записи на шины 16 и 17. В этом случае с входа ячейки памяти через второй ключ 11 на затвор транзистбра 2 будет поступать сигнал . с выхода внешнего регулирующего элемента. В результате этого ток, протекающий по цепи: шина 19 питания, преобразователь 1 напряжение - ток, коммутатор 7, третий выход, будет установлен пропорционально уровню входного сигнала с точностью 1/К, где К - коэффициент усилен1 я внешнего регулирующего элемента (например, операционного усилителя). По окончании строба записи до подачи строба считывания на шину 1В ячейка памяти осуществляет хранение сигнала. При подаче строба считывания на шину 18 осуществляется считывание сигнала. При этом ток считывания, пропорциональный выборке входного сигнала, протекает на Вых.1, если подан разрешающий потенциал на шину k управления, либо на Вых. 2, если потенциал подан на шину 15 управления. Введение первого и второго ключей и коммутатора позволяет через третий выход установить с помощью внешнего регулирующего элемента ток первого транзистора, пропорциональный уровню входного сигнала с точностью 1/К, где К коэффициент усиления регулирующего элемента. У современных ре,гу;лирующих элементов (операционных , усилителей) К 50000, что позволяет реализовать точность установки и считывания тока ячейки не хуже 0,10,011. Выигрыш по мощности достигается за счет того, что устройство в цепи тока считывания содержит только преобразователь напряжение - ток с малым внутренним сопротивлением и низкоомный переключатель тока. Благодаря этому питание ячейки осуществляется от низковольтного ( 0,6-2 В) источника питания, за счет чего достигается экономия потребляемой мощности. Технико-экономический эффект возникает при использовании ячейки памяти в программируемых фильтрахО.гналов. Снижение на порядок уровня нелинейных искажений и уменьшение примерно в раза потребляемой мощности позволяют примерно в три раза сократить объем аппаратурных затрат при изготовлении устройств обработки игналов на основе программируемых ильтров сигналов, содержащих ячейу памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

. ЯЧЕЙКА ПАМЯТИ, содержащая преобразователь напряжение г ток, выполненный на первом МДП-транзисторе, сток которого соединен с шиной питания, переключатель тока, выполненный на втором и третьем МДП-транзисторах, затворы которых соединены соответственно с первой и второй шинами управления, стоки второго и третьего МДП-транзисторов являются первым и вто|%1М выходами ячейки па мяти, накопительный элемент, выполненный на конденсаторе, образр ванном затвором первого МДП-транзистора и шиной нулевого потенциала, и . шины напряжения стробирования, отличающаяся тем, что, с целью повь1шения точности и уменьшения потребляемой мощности ячейкой памяти, в нее введены коммутатор, выполненный на четвертом и пятом МДП-транзисторах, первый и второй ключи, выполненные .на шестом и седьмом НДП-транзисторах, причем затворы четвертого и пятого МДП-транзисторов i соединены соответственно с первой и второй шинами напряжения стробирования, исток четвертого МДП-транзистора соединен с истоком пятого МДП транзистора, сток которого соединен с истоком первого и со стоком Шестого МДГ -транзисторов, сток четi вертого МДП-транзистора является третьим выходом ячейки памяти, исток шестого МДП-транзистора соединение истоками второго и третьего МДП- транзисторов, затвор шестого МДП-транзистора соединен с третьей шиной напряжения стробирования, исток седьмого МДП-транзистора является входом ячейО ки памятиi затвор седьмого МДП-транзистора соединен с первой шиной наю пряжения стробирования, сток седьмо1C го МДП-транзистора соединен с затвою ю ю ром первого МДП-транзистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ фотографической записи звуковых колебаний | 1922 |

|

SU400A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дополнительный полюс большого магнитного сопротивления в динамо-машинах | 1924 |

|

SU1376A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-06-07—Публикация

1979-10-08—Подача