Изобретение относится к импульсной технике и может быть использовано в качестве стандартного узла цифровой СБИС. Цель изобретения - расширение функциональных возможностей устройства за счет введения режима начальной установки, режима пересчета 1:1, 2:1 и режима управления счетом.

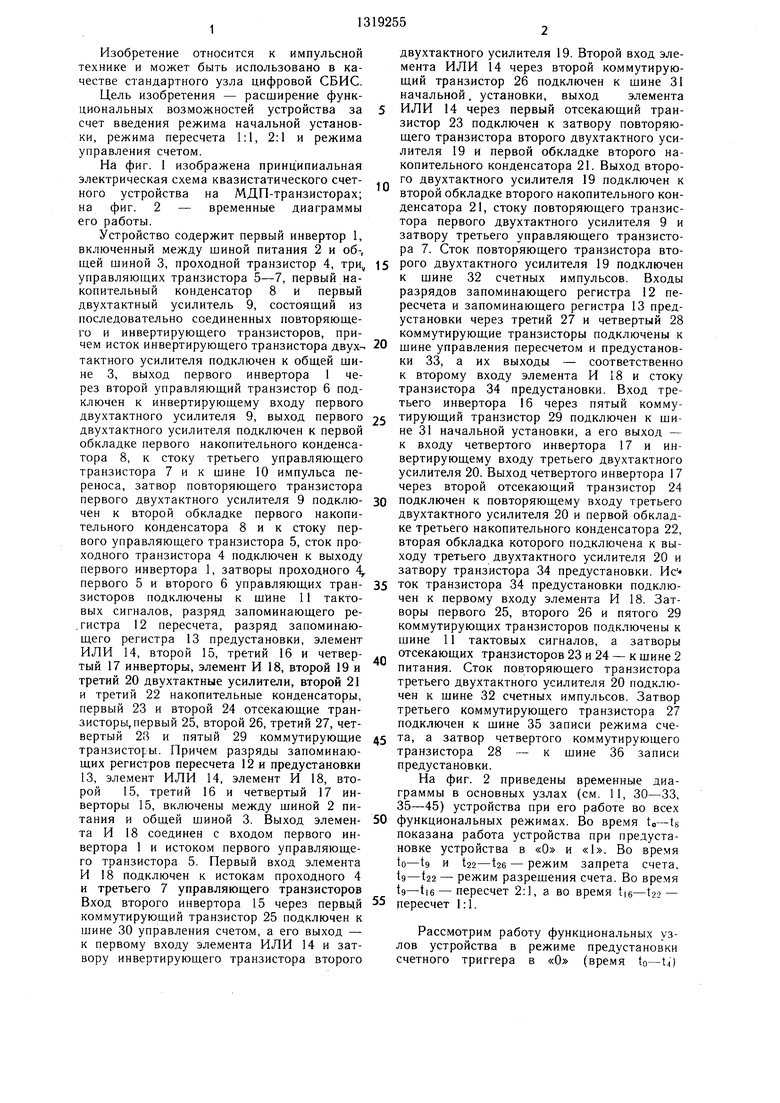

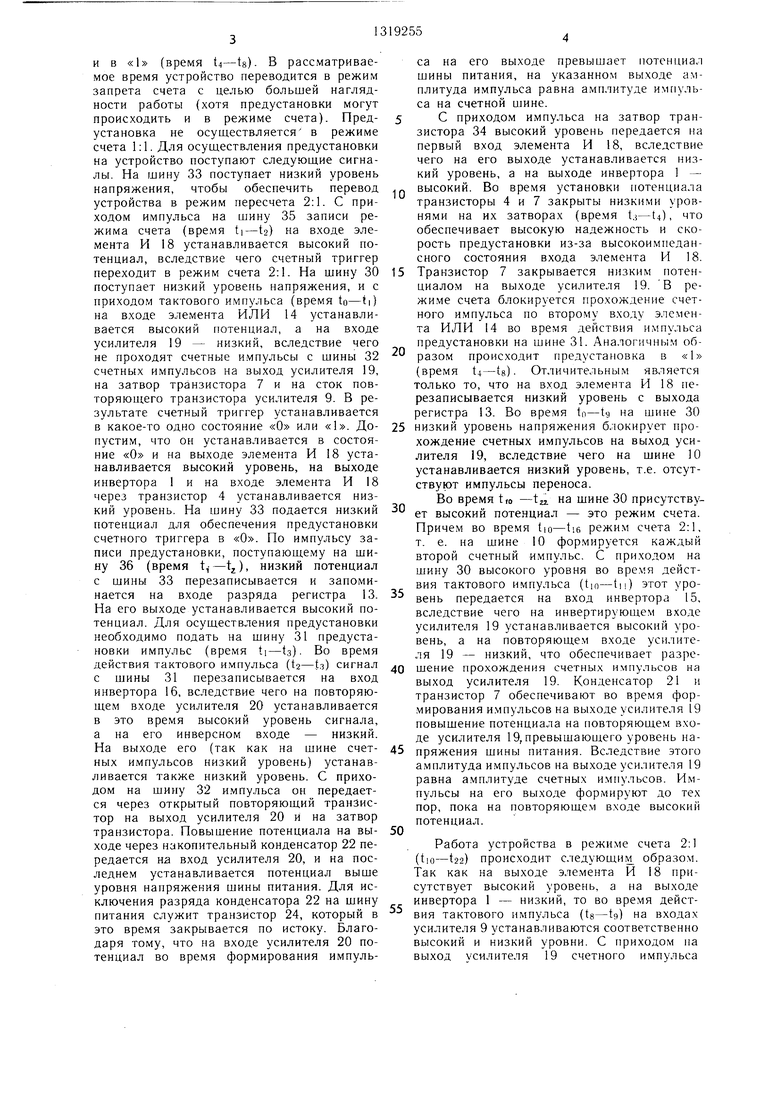

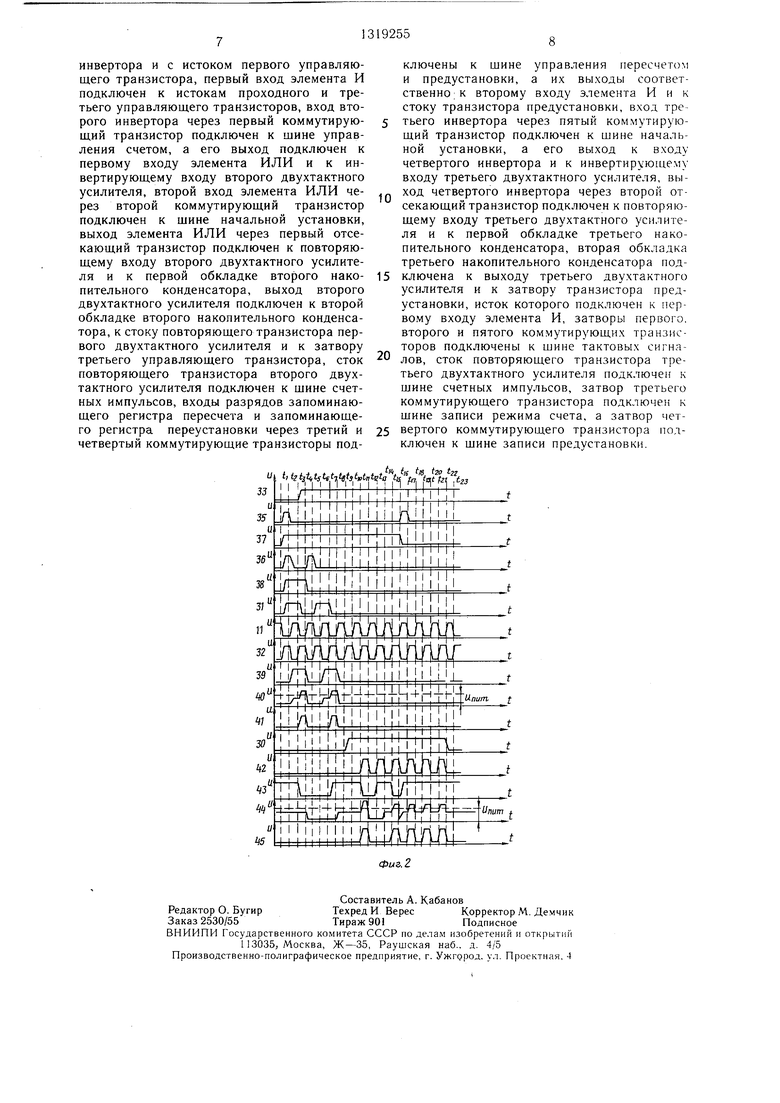

На фиг. I изображена принц ипиальная электрическая схема квазистатического счет- ного устройства на МДП-транзисторах; на фиг. 2 - временные диаграммы его работы.

Устройство содержит первый инвертор 1, включенный между шиной питания 2 и об-, щей шиной 3, проходной транзистор 4, три управляюш,их транзистора 5-7, первый накопительный конденсатор 8 и первый двухтактный усилитель 9, состоящий из последовательно соединенных повторяющего и инвертирующего транзисторов, причем исток инвертирующего транзистора двух- тактного усилителя подключен к общей шине 3, выход первого инвертора 1 через второй управляющий транзистор 6 подключен к инвертирующему входу первого двухтактного усилителя 9, выход первого двухтактного усилителя подключен к первой обкладке первого накопительного конденсатора 8, к стоку третьего управляющего транзистора 7 и к шине 10 импульса переноса, затвор повторяющего транзистора первого двухтактного усилителя 9 подклю- чен к второй обкладке первого накопительного конденсатора 8 и к стоку первого управляющего транзистора 5, сток проходного транзистора 4 подключен к выходу первого инвертора 1, затворы проходного 4 первого 5 и второго 6 управляющих тран- зисторов подключены к щИне 11 тактовых сигналов, разряд запоминающего ре- .гистра 12 пересчета, разряд запоминающего регистра 13 предустановки, элемент ИЛИ 14, второй 15, третий 16 и четвер- тый 17 инверторы, элемент И 18, второй 19 и третий 20 двухтактные усилители, второй 21 и третий 22 накопительные конденсаторы, первый 23 и второй 24 отсекающие транзисторы, первый 25, второй 26, третий 27, четвертый 28 и пятый 29 коммутирующие транзисторы. Причем разряды запоминающих регистров пересчета 12 и предустановки 13, элемент ИЛИ 14, элемент И 18, второй 15, третий 16 и четвертый 17 инверторы 15, включены между щиной 2 питания и общей щиной 3. Выход элемен- та И 18 соединен с входом первого инвертора 1 и истоком первого управляющего транзистора 5. Первый вход элемента И 18 подключен к истокам проходного 4 и третьего 7 управляющего транзисторов Вход второго инвертора 15 через первый коммутирующий транзистор 25 подключен к шине 30 управления счетом, а его выход - к первому входу элемента ИЛИ 14 и затвору инвертирующего транзистора второго

двухтактного усилителя 19. Второй вход элемента ИЛИ 14 через второй коммутирующий транзистор 26 подключен к щине 31 начальной. установки, выход элемента ИЛИ 14 через первый отсекающий транзистор 23 подключен к затвору повторяющего транзистора второго двухтактного усилителя 19 и первой обкладке второго накопительного конденсатора 21. Выход второго двухтактного усилителя 19 подключен к второй обкладке второго накопительного конденсатора 21, стоку повторяющего транзистора первого двухтактного усилителя 9 и затвору третьего управляющего транзистора 7. Сток повторяющего транзистора второго двухтактного усилителя 19 подключен к шине 32 счетных импульсов. Входы разрядов запоминающего регистра 12 пересчета и запоминающего регистра 13 предустановки через третий 27 и четвертый 28 коммутирующие транзисторы подключены к шине управления пересчетом и предустановки 33, а их выходы - соответственно к второму входу элемента И 18 и стоку транзистора 34 предустановки. Вход третьего инвертора 16 через пятый коммутирующий транзистор 29 подключен к щине 31 начальной установки, а его выход - к входу четвертого инвертора 17 и инвертирующему входу третьего двухтактного усилителя 20. Выход четвертого инвертора 17 через второй отсекающий транзистор 24 подключен к повторяющему входу третьего двухтактного усилителя 20 и первой обкладке третьего накопительного конденсатора 22, вторая обкладка которого подключена к выходу третьего двухтактного усилителя 20 и затвору транзистора 34 предустановки. Ис ток транзистора 34 предустановки подключен к первому входу элемента И 18. Затворы первого 25, второго 26 и пятого 29 коммутирующих транзисторов подключены к шине 11 тактовых сигналов, а затворы отсекающих транзисторов 23 и 24 - к щине 2 питания. Сток повторяющего транзистора третьего двухтактного усилителя 20 подключен к шине 32 счетных импульсов. Затвор третьего коммутирующего транзистора 27 подключен к щине 35 записи режима счета, а затвор четвертого коммутирующего транзистора 28 - к щине 36 записи предустановки.

На фиг. 2 приведены временные диаграммы в основных узлах (см. 11, 30-33, 35-45) устройства при его работе во всех функциональных режимах. Во время to-tg показана работа устройства при предустановке устройства в «О и «1. Во время to-tg и t22-126 - режим запрета счета, tg-122 - режим разрешения счета. Во время tg-ti6 - пересчет 2:1, а во время - пересчет 1:1.

Рассмотрим работу функциональных узлов устройства в режиме предустановки счетного триггера в «О (время to-t)

и в «1 (время t4-tg). В рассматриваемое время устройство переводится в режим запрета счета с целью большей наглядности работы (хотя предустановки могут происходить и в режиме счета). Предустановка не осуществляется в режиме счета 1:1. Для осуществления предустановки на устройство поступают следующие сигналы. На щину 33 поступает низкий уровень напряжения, чтобы обеспечить перевод устройства в режим пересчета 2:1. С приходом импульса на щину 35 записи режима счета (время ti-12) на входе элемента И 18 устанавливается высокий потенциал, вследствие чего счетный триггер переходит в режим счета 2:1. На шину 30 поступает низкий уровень напряжения, и с приходом тактового импульса (время to-1|) на входе элемента ИЛИ 14 устанавливается высокий потенциал, а на входе усилителя 19 - низкий, вследствие чего не проходят счетные импульсы с щины 32 счетных импульсов на выход усилителя 19, на затвор транзистора 7 и на сток повторяющего транзистора усилителя 9. В результате счетный триггер устанавливается в какое-то одно состояние «О или «1. Допустим, что он устанавливается в состояние «О и на выходе эле.мента И 18 устанавливается высокий уровень, на выходе инвертора 1 и на входе элемента И 18 через транзистор 4 устанавливается низкий уровень. На щину 33 подается низкий потенциал для обеспечения предустановки счетного триггера в «О. По импульсу записи предустановки, поступающему на щину 36 (время t,--t), низкий потенциал с щины 33 перезаписывается и запоминается на входе разряда регистра 13. На его выходе устанавливается высокий потенциал. Для осуществления предустановки необходимо подать на щину 31 предустановки импульс (время ti-ta). Во время действия тактового импульса (t2-|:з) сигнал с щины 31 перезаписывается на вход инвертора 16, вследствие чего на повторяющем входе усилителя 20 устанавливается в это время высокий уровень сигнала, а на его инверсном входе - низкий. На выходе его (так как на щине счетных импульсов низкий уровень) устанавливается также низкий уровень. С приходом на щину 32 и.мпульса он передается через открытый повторяющий транзистор на выход усилителя 20 и на затвор транзистора. Повыщение потенциала на выходе через накопительный конденсатор 22 передается на вход усилителя 20, и на последнем устанавливается потенциал выще уровня напряжения щины питания. Для исключения разряда конденсатора 22 на щину питания служит транзистор 24, который в это время закрывается по истоку. Благодаря тому, что на входе усилителя 20 потенциал во время формирования импуль0

5

0

5

0

5

0

5

0

5

са на его выходе превыщает потенциал щины питания, на указанном выходе амплитуда импульса равна амплитуде импульса на счетной щине.

С приходом импульса на затвор транзистора 34 высокий уровень передается на первый вход элемента И 18, вследствие чего на его выходе устанавливается низкий уровень, а на аыходе инвертора 1 - высокий. Во время установки потенциала транзисторы 4 и 7 закрыты низкими уровнями на их затворах (время t.i-(4), что обеспечивает высокую надежность и скорость предустановки из-за высокоимпедан- сного состояния входа элемента И 18. Транзистор 7 закрывается низким потенциалом на выходе усилителя 19. В режиме счета блокируется прохождение счетного импульса по второму входу элемента ИЛИ 14 во время действия импульса предустановки на щине 31. Аналогичным образом происходит предустановка в «1 (время t4-tg). Отличительным является только то, что на вход элемента И 18 перезаписывается низкий уровень с выхода регистра 13. Во время tn-tg на щине 30 низкий уровень напряжения блокирует прохождение счетных импульсов на выход усилителя 19, вследствие чего на щине 10 устанавливается низкий уровень, т.е. отсутствуют импульсы переноса.

Во время t(o -tji на щине 30 присутствует высокий потенциал - это режим счета. Причем во время tio-tie режим счета 2:1, т. е. на щине 10 формируется каждый второй счетный импульс. С приходом на щину 30 высокого уровня во время действия тактового импульса (tio-tii) этот уровень передается на вход инвертора 15, вследствие чего па инвертирующем входе усилителя 19 устанавливается высокий уровень, а на повторяющем входе усилителя 19 - низкий, что обеспечивает разрешение прохождения счетных импульсов на выход усилителя 19. Конденсатор 21 и транзистор 7 обеспечивают во время формирования и.мпульсов на выходе усилителя 19 повыщение потенциала на повторяющем входе усилителя 19, превыщаюп его уровень напряжения щины питания. Вследствие этого а.мплитуда импульсов на выходе усилителя 19 равна амплитуде счетных импульсов. И.м- пульсы на его выходе формируют до тех пор, пока на повторяюще.м входе высокий потенциал.

Работа устройства в режиме счета 2:1 (tio-122) происходит следующим образом. Так как на выходе эле.мента И 18 присутствует высокий уровень, а па выходе инвертора 1 - низкий, то во время действия тактового импульса (ts-tg) на входах усилителя 9 устанавливаются соответственно высокий и низкий уровни. С приходом па выход усилителя 19 счетного импульса

(tg-t

МО ОН передается через открытый

повторяющий транзистор усилителя 9 на шину 10 и через транзистор 7 на вход элемента И 18. Высоким потенциалом на его входе устанавливается на выходе элемента 18 низкий уровень, а на выходе инвертора 1 - высокий. На шине 10 формируется амплитуда импульса, равная амплитуде счетных импульсов на шине 32 благодаря конденсатору 8. По окончании счетного импульса на выходе усилителя 19 транзистор 7 закрывается, но высокий уровень запоминается на входной емкости входа элемента И 18. С приходом тактового импульса высокий уровень на этом входе поддерживается транзистором 4, который на время действия тактовых импульсов осу- ществляют подключение выхода инвертора 1 ia первый вход элемента И 18. Во время действия тактового импульса (ti2-iis) на входах усилителя 9 устанавливаются через транзисторы 5 и 6 соответственно низкий и высокий уровни. С приходом следующего счетного импульса {li.j-tu) на выход усилителя 19 он не проходит через закры- Tbn i повторяющий транзистор усилителя 9 на тину 10, и на последнем остается низкий уровень. Через транзистор 7 на первом входе элемента И 18 устанавливается низкий потенциал, следовательно, на выходах элемента И 18 и инвертора 1 устанавливаются соответственно высокий и низкий уровни. По тактовому импульсу (i 4-tis) через транзисторы 5 и 6 на входах усилителя 9 устанавливаются соответственно высокий и низкий уровни. С приходом очередного счетного импульса (ti5-ti(i) на шине 10 формируется импульс, а на первом входе элемента И 18 устанавливается высокий уровепь, т. е. повторяется состояние (ti 1-ti2). Таким образом, в данном режиме на шину И) проходит каждь й второй счетный импульс, т. е. происходит пересчет 2:1.

Во время ti6-i 7 импульсом записи режима счета на шине 35, на выходе разряда запоминающего регистра 12 устанавливается низкий потенциал в соответствии с . ютенциалом на шине 33. Вследствие этого на выходах элемента И 18 и инвертора 1 устанавливаются и поддерживаются соответственно высокий и низкий уровни (время t,b-tis). По тактовому импульсу {время t|fe -t ,г ) высокий уровень с выхода элемента И 18 через транзистор 5 передается на повторяющий вход усилителя 9, а низкий уровень с выхода инвертора 1 через транзистор 6 передается на инвертирующий вход усилителя 9. С приходом на выход усилителя 19 следующего счетного импульса (время ti7-tis) на щине 10 формируется импульс. Так как во время действия последующих тактовых импульсов уровни на входах усилителя 9 остаются

соответственно высоким и низким, то на шине 10 формируются импульсы с приходом на выход усилителя 19 каждого счетного импульса, т. е. происходит пересчет 1:1. С приходом на шину 30 низкого уровня (tai-126) по тактовому импульсу (t22-12.3)

на входе элемента ИЛИ 14 устанавливается высокий уровень и блокирует прохождение счетных импульсов на выход усилителя 19, т. е. переводит устройство в ре- жим запрета счета. Таким образом, квазистатическое счетное устройство на МДП- транзисторах обеспечивает управление счетом (запрет счета и разрешение счета), два режима счета (пересчет 2:1 и пересчет 1:1), начальную установку счетно1-о

триггера в «О и в «1.

5

Формула изобретения

Квазистатическое счетное устройство на

0 МДП-транзнсторах, содержащее первый инвертор, включенный между шиной питания и общей шиной, проходной транзистор, три управляющих транзистора, первый накопительный конденсатор и первый двухтактный усилитель, состоящий из последовательно соедипенных повторяющего и инвертирующего транзисторов, причем исток инвертирующего транзистора двухтактного усилителя подключен к общей шине, выход первого инвертора через второй управQ ляющий транзистор подключен к инверти- рующе.му входу первого двухтактного усилителя, выход первого двухтактного усилителя подключен к первой обкладке первого накопительного конденсатора, к стоку I peTbei о управляющего транзистора и к шине

5 импульса переноса, затвор повторяющего транзистора первого двухтактного усилителя подключен к второй обкладке первого накопительного конденсатора и к стоку первого управляющего транзистора, сток проходного транзистора иол.ключен к выходу первого ин0 вертора, затворы проходного первого и второго управляющих транзисторов подключены к щкне тактовых скгнало.з. отличаю- щееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены разряд заЕЮминаю- nicro регистра пересчета, разряд запоминающего регистра предустановки, элемент ИЛИ, второй, третий и четвертый инверторы, эле.мент И, второй и третий накопительные конденсаторы, второй и третий двух0 тактные усилители, первый и второй отсекающие транзисторы, транзистор предустановки, первый, второй, третий, четвертый и пятый коммутирующие транзисторы, разряд запо.минающего регистра предустановки, разряд запоминающего регистра пересчета,

5 элемент ИЛИ, элемент И, второй, третий и четвертый инверторы включены между шиной питания и обш.ей шиной, выход элемента И соединен с входом первого

инвертора и с истоком первого управляющего транзистора, первый вход элемента И подключен к истокам проходного и третьего управляющего транзисторов, вход второго инвертора через первый коммутирующий транзистор подключен к шине управления счетом, а его выход подключен к первому входу элемента ИЛИ и к инвертирующему входу второго двухтактного усилителя, второй вход элемента ИЛИ через второй коммутирующий транзистор подключен к шине начальной установки, выход элемента ИЛИ через первый отсекающий транзистор подключен к повторяющему входу второго двухтактного усилителя и к первой обкладке второго накопительного конденсатора, выход второго двухтактного усилителя подключен к второй обкладке второго накопительного конденсатора, к стоку повторяющего транзистора первого двухтактного усилителя и к затвору третьего управляющего транзистора, сток повторяющего транзистора второго двухтактного усилителя подключен к щине счетных импульсов, входы разрядов запоминающего регистра пересчета и запоминающего регистра переустановки через третий и четвертый коммутирующие транзисторы подключены к щине управления пересчетом и предустановки, а их выходы соответственно; к второму входу элемента Инк стоку транзистора предустановки, вход тре- 5 тьего инвертора через пятый коммутирующий транзистор подключен к шине начальной установки, а его выход к входу четвертого инвертора и к инвертирующему входу третьего двухтактного усилителя, выQ ход четвертого инвертора через второй отсекающий транзистор подключен к повторяющему входу третьего двухтактного усилителя и к первой обкладке третьего накопительного конденсатора, вторая обкладка третьего накопительного конденсатора под5 ключена к выходу третьего двухтактного усилителя и к затвору транзистора предустановки, исток которого подключен к первому входу элемента И, затворы первого. второго и пятого коммутирующих транзисторов подключены к шине тактовых сигналов, сток повторяющего транзистора третьего двухтактного усилителя подключен к щине счетных импульсов, затвор третьего коммутирующего транзистора подключен к щине записи режима счета, а затвор чет5 вертого коммутирующего транзистора подключен к щине записи предустановки.

0

35

-t..Y Yi i Vf Y M : l

1 .Г. I i г I I i 1 il I I

35

37

36

3)

32

зэ

..(1

ш/шшшгад

5«fc7H33±eih±HEl«I

41

зо (

ад

« «

, liliiMn

n ITTT I I I I I I ч I M

-УС

dftm

5

-УС

ПЛИМУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Квазистатический счетный триггер на мдп-транзисторах | 1975 |

|

SU632060A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Усилитель-формирователь импульсов на мдп транзисторах | 1974 |

|

SU525247A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Усилитель-формирователь на металло= диэлектрических полупроводниковых транзисторах | 1974 |

|

SU531284A2 |

| Устройство формирования импульсов на МДП-транзисторах | 1985 |

|

SU1277380A1 |

| Ячейка коррелятора | 1979 |

|

SU843235A1 |

Изобретение относится к импульсной технике. Может быть использовано в ка- честве стандартного узла цифровой СБИС, Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит транзисторы 4-7, инвертор 1, накопительный конденсатор 8, двухтактный усилитель 9. Для достижения поставленной цели в устройство введены запоминающие регистры -12, 13, элемент ИЛИ 14, инверторы 15-17, элемент И 18, двухтактные усилители 19, 20, накопительные конденсаторы 21, 22, транзисторы 23-29. 2 ил. S (Л со со to ел ел

Составитель A. Кабанов

Редактор О. БугирТехред И ВересКорректор М. Демчик

Заказ 2530/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.. д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Триггер на мдп транзисторах | 1978 |

|

SU790127A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Квазистатический счетный триггер на мдп-транзисторах | 1975 |

|

SU632060A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-03—Подача