(54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Формирователь адресных сигналов для блоков памяти | 1983 |

|

SU1163354A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

1

Изобретение относится к автоматике и вычислительной технике и преназначено для использования, в частности, в интегральных полупостоянных ЗУ.

Известен усилитель считывания, содержащий первый разрядный транзистор, затвор которого подключен к входу усилителя, и инвертор, состящий из зарядного и второго разрядного транзисторов, сток зарядного транзистора подключен к шине питания, затвор и исток соединен со стоком второго разрядного транзистора, исток которого соединен с шиной смещения. Кроме того, усилите.г1ь.,содержит транзистор с обеднением, образующий истоковый повторитель с первым разрядным транзистором и два выходных транзистора, соединенных в пошпульный выходной каскад 1,

Недостатком данного усилителя является пониженное быстродействие, обусловленное тем, что транзистор с обеднением, подключенный к истоку первого разрядного транзистора, образует с ним истоковый повторител и замедляет за счет отрицательной обратной связи с выходом инвертора прием считываемой информации.

Если на затво э первого разрядного транзистора поступает логическая , то проводимость транзистора с обеднением уменьшается, что приводит к увеличению потенциала на истоке первого разрядного транзистора, который замедляет прием логичес1. а если поступает логикой

ческий О, то проводимость тран0зистора с обеднением возрастает, потенциал на истоке первого разрядного транзистора уменьшается, замедляя прием логического О.

Известен также усилитель считы5вания, содержащий два инвертора, в каждом из которых зарядный транзистор стоком соединен с шиной питання, исток зарядного транзистора первого инвертора соединен со стоком перво0го разрядного транзистора, затвор которого подключен к входу усилителя считывания. Исток зарядного транзистора второго инвертора соединен со стоком второго разрядного тран5зистора, затвор которого подключен к стоку первого разрядного транзистора, а исток соединен с истоком . принимающего транзистора. Смещение на истоке первого разрядного тран-

0 зистора обеспечивается транзистором,

сток которого подключен к истоку первого разрядного транзистора/ затвор соединен с шиной питания, а исток подключен к шине смещения 2.

Недостатком указанного усилителя считывания является отсутствие управляемого смещения на истоке первого разрядного транзистора, что замедляет прием считываемой информации .

Наиболее близким к предлагаемому является усилитель считывания,содержащий три инвертора со встроенными нагрузками,причем затвор и исток зарядного транзистора первого инвертор соединен со стоком разрядного транзистора первого инвертора и с затвором разрядного транзистора второго инвертора/сток которого соединен с затвором и истоком зарядного транзистора второго инвертора,затвор и исток зарядного транзистора третьего инвертора соединен со стоком разрядного транзистора третьего инвертора. Кроме того/ усилитель содержит выходные транзисторы, затворы которых соединены с выходами инверторов 3 .

Недостаток известного усилителя в том, что положительный потенциал на истоке первого разрядного транзистора, равный напряжению смещения, замедляет прием логического О , что приводит к уменьшению быстродействия и помехоустойчивости. Кроме того, технологический разброс порогового напряжения транзистора с обеднением уменьшает надежность данного усилителя считывания.

Цель изобретения - повышение быстродействия и помехоустойчивости усилителя считывания.

Поставленная цель достигается тем, что в усилитель считывания, содержащий три инвертора/ каждый из которых состоит из зарядного транзистора со встроенным каналом и из разрядного транзистора, сток которого соединен с затвором и истоком зарядного транзистора со встроенным каналом, стоки зарядных транзисторов со встроенным каналом подключены к шине питания, истоки разрядных транзисторов объединены, затвор первого разрядного транзистора соединен с затвором третьего разрядного транзистора и подключен к входу усилителя,сток первого разрядного транзистора соединен с затвором второго разрядного транзистора,сток кот рого подключен к прямому выходу усилителя, сток третьего разрядного транзистора подключен к инверсному выходу усилителя, и коммутирующий транзистор, исток которого подключен к шине смещения, а затвор - к шине управления, введены два согласующих транзистора со встроенными каналами сток первого из которых подключен к шине питания, затвор - к стоку

первого разрядного транзистора, а исток соединен с истоком первого разрядного транзистора и со стоком второго согласующего транзистора со встроенным каналом, затвор и исток которого соединены со стоком коммутирующего транзистора.

В данном усилителе считывания дополнительно введенные транзисторы за счет управления смещением истока первого разрядного транзистора создают благоприятные условия для приема каждого из логических уроваей двоичной информации,в результате чего усилитель обладает более высокими быстродействием, помехоустойчивостью и надежностью, повышение которой обеспечивается также нейтрализацией технологических отклонений порогового напряжения транзисторов со встроенными каналами.

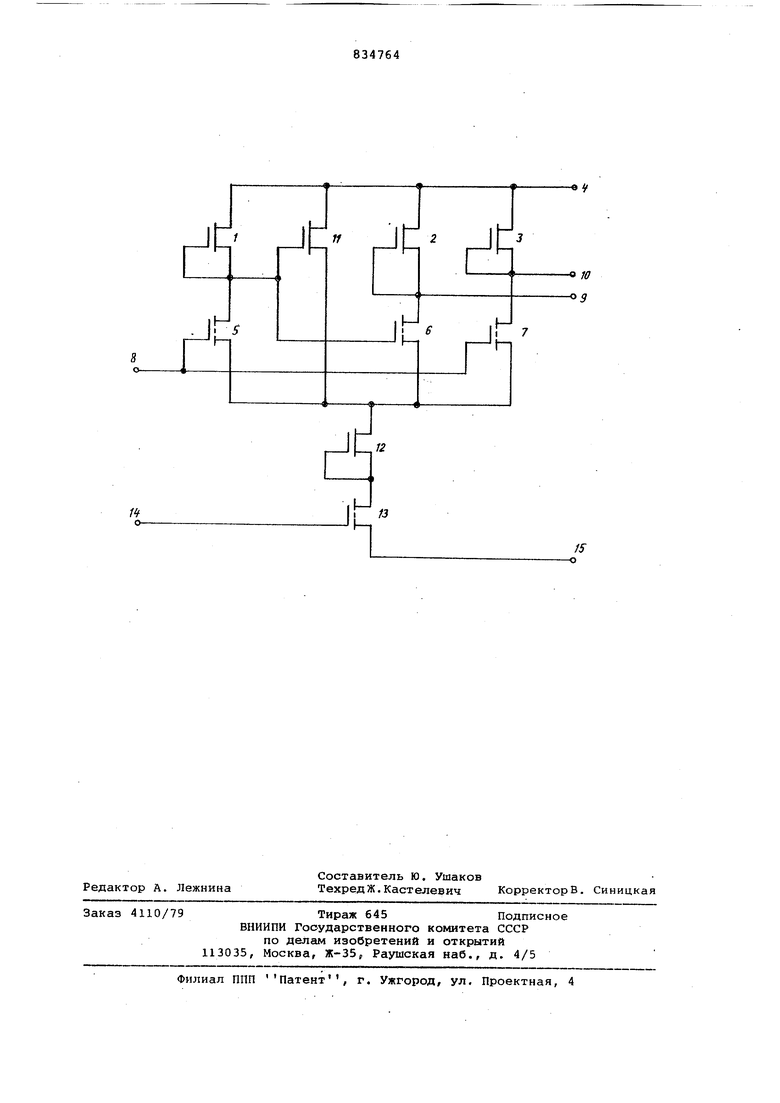

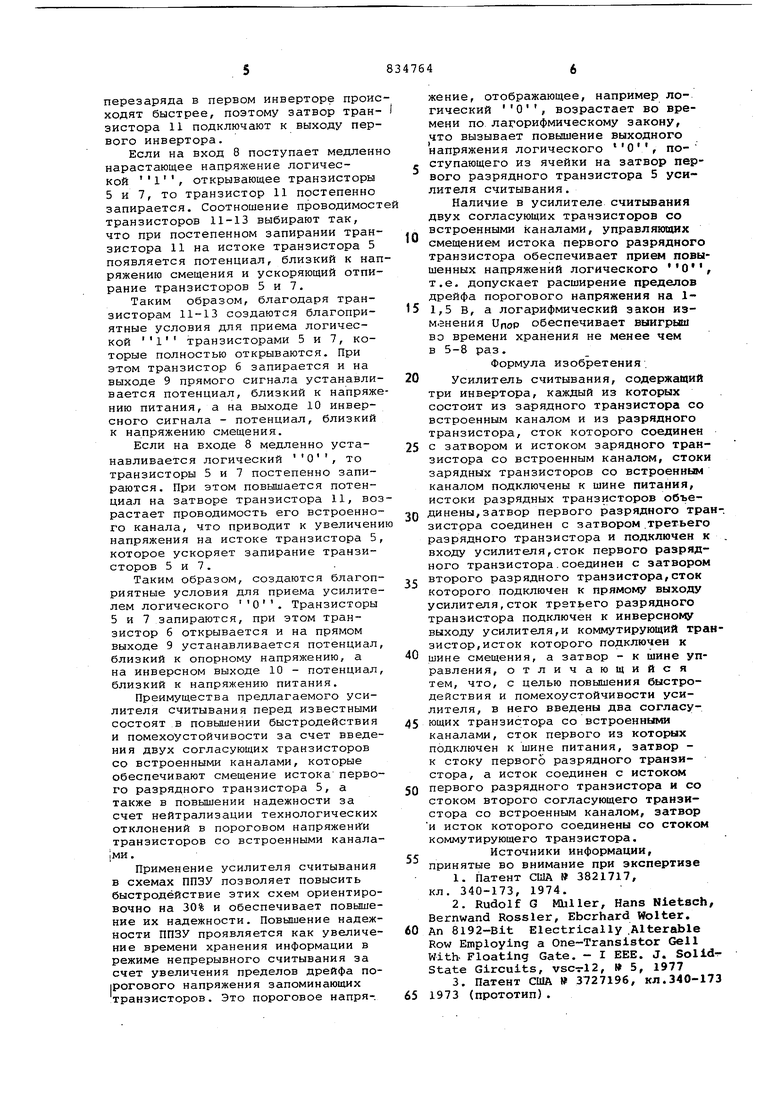

На чертеже изображена схема усилителя считывания.

Усилитель считывания содержит три инвертора, зарядными транзисторами 1-3 в которых являются МДПтранзисторы со встроенным каналом, стоки которых подключены к шине 4 . питания. Исток и затвор зарядного транзистора 1 подключены к стоку певого разрядного транзистора 5 с индцированным каналом и к затвору вторго разрядного транзистора 6 с индуцрованным каналом. Затвор транзистора 5 соединен с затвором третьего разрядного транзистора 7 с индуцированным каналом и подключен к вход 8, а исток его соединен с истоками разрядных транзисторов б и 7, стоки которых соответственно подключены к истокам и затворам зарядных транзсторов 2 и З.Сток разрядного транзистора 6 соединен с прямым выходом 9 а сток разрядного транзистора 7 - с инверсным выходом 10.

Кроме этого,устройство включает два согласующих транзистора 11 и 12 со встроенными к Налами, причем сток транзистора 11 Подключен к шине 4 питания, а затвор - к стоку транзистора 5. Исток транзистора 11 соединен с истоком транзистора 5 и стоком транзистора 12, затвор и исток которого подключены к стоку коммутирующего транзистора 13 с индукцированным каналом, затвор которого соединен с шиной 14 управления, а исток - с шиной 15 смещения.

Устройство работает следующим образом.

Для включения усилителя считывания на шину 14 управления подается

(напринапряжение логической

мер сигнал из дешифратора адреса или сигнал Выбор ИС), открывающее транзистор 13. Емкостная нагрузка . первого инвертора намного меньше емкостной нагрузки второго и третьего инверторов, вследствие чего процессы перезаряда в первом инверторе прои ходят быстрее, поэтому затвор тран зистора 11 подключают к выходу пер вого инвертора. Если на вход 8 поступает медлен нарастающее напряжение логической , открывающее транзисторы 5 и 7, то транзистор 11 постепенно запирается. Соотношение проводимос транзисторов 11-13 выбирают так, что при постепенном запирании тран зистора 11 на истоке транзистора 5 появляется потенциал, близкий к на ряжению смещения и ускоряющий отпи рание транзисторов 5 и 7. Таким образом, благодаря транзисторам 11-13 создаются благоприятные условия для приема логической транзисторами 5 и 7, которые полностью открываются. При этом транзистор 6 запирается и на выходе 9 прямого сигнала устанавли вается потенциал, близкий к напряж нию питания, а на выходе 10 инверсного сигнала - потенциал, близкий к напряжению смещения. Если на входе 8 медленно устаО , то навливается логический транзисторы 5 и 7 постепенно запираются. При этом повышается потенциал на затворе транзистора 11, во растает проводимость его встроенно го канала, что приводит к увеличен напряжения на истоке транзистора 5 которое ускоряет запирание транзисторов 5 и 7 . Таким образом, создаются благоп риятные условия для приема усилителем логического О. Транзисторы 5 и 7 запираются, при этом транзистор б открывается и на прямом выходе 9 устанавливается потенциал близкий к опорному напряжению, а на инверсном выходе 10 - потенциал близкий к напряжению питания. Преимущества предлагаемого усилителя считывания перед известными состоят в повышении быстродействия и помехоустойчивости за счет введения двух согласующих транзисторов со встроенными каналами, которые обеспечивают смещение истока первого разрядного транзистора 5, а также в повышении надежности за счет нейтрализации технологических отклонений в пороговом напряжении транзисторов со встроенными канала|ми. Применение усилителя считывания в схемах ППЗУ позволяет повысить быстродействие этих схем ориентировочно на 30% и обеспечивает повышение их надежности. Повышение надежности ППЗУ проявляется как увеличение времени хранения информации в режиме непрерывного считывания за счет увеличения пределов дрейфа поiporoBoro напряжения запоминающих транзисторов. Это пороговое напря-. жение, отображающее, например логический О, возрастает во времени по лагорифмическому закону, что вызывает повышение выходного напряжения логического OV, поступающего из ячейки на затвор первого разрядного транзистора 5 усилителя считывания. Наличие в усилителе считывания двух согласующих транзисторов со встроенными каналами, управляющих смещением истока первого разрядного транзистора обеспечивает прием повышенных напряжений логического О, т.е. допускает расширение пределов дрейфа порогового напряжения на 11,5 в, а логарифмический закон изменения ОПОР обеспечивает выигрыш во времени хранения не менее чем в 5-8 раз. Формула изобретения Усилитель считывания, содержащий три инвертора, каждый из которых состоит из зарядного транзистора со встроенным каналом и из разрядного транзистора, сток которого соединен с затвором и истоком зарядного транзистора со встроенным каналом, стоки зарядных транзисторов со встроенным каналом подключены к шине питания, истоки разрядных транзисторов объединены, затвор первого разрядного транзистрра соединен с затвором третьего разрядного транзистора и подключен к входу усилителя,сток первого разрядного транзистора.соединен с затвором второго разрядного транзистора,сток которого подключен к прямому выходу усилителя,сток третьего разрядного транзистора подключен к инверсному выходу усилителя,и коммутирующий транзистор,исток которого подключен к шине смещения, а затвор - к шине управления, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости усилителя, в него введены два согласующих транзистора со встроенными каналами, сток первого из которых подключен к шине питания, затвор к стоку первого разрядного транзистора, а исток соединен с истоком первого разрядного транзистора и со стоком второго согласующего транзистора со встроенным каналом, затвор и исток которого соединены со стоком коммутирующего транзистора. Источники информации, принятые во внимание при экспертизе 1.Патент США 3821717, кл. 340-173, 1974. 2.Rudolf G Mliller, Hans Nietsch, Bernwand Rossler, Ebcrhard Wolter. n 8192-Bit Electrically .Alterable Row Employing a One-Transistor Cell ith- Floating Gate. - I НЕЕ. J. Solid-etate Circuits, VSCT12, 5, 1977 3.Патент США 3727196, кл.340-173 1973 (прототип).

-Jk rJU

1 o-e

Jt

-e Л7 -05

u

/5

Авторы

Даты

1981-05-30—Публикация

1978-12-07—Подача