(54) ДЕКОДЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1984 |

|

SU1290532A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Селектор импульсов по длительности | 1986 |

|

SU1352629A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Устройство для синхронизации М-последовательности | 1985 |

|

SU1322429A2 |

| Многоканальный преобразователь напряжения в код | 1982 |

|

SU1109900A1 |

| Селектор пачки импульсов | 1979 |

|

SU813751A2 |

| Устройство коррекции временных искажений воспроизведенных самосинхронизирующихся сигналов | 1983 |

|

SU1123050A1 |

| Декодирующее устройство | 1986 |

|

SU1432781A1 |

1

Изобретение относится к автоматике.

Наиболее близким техническим решением к изобретению является декодер, содержащий селектор второго импульса, входы которого соединены с входными шинами, а выход подключен к одному из входов элемента ИЛИ-НЕ, выход которого соединен с выходной шиной, а другой вход - с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя 1.

Недостаток известного устройства - сложность конструкции.

Цель изобретения - упрощение декодера.

Указанная цель достигается тем, что в декодере, содержащем селектор второго импульса, входы которого соединены с входными щинами, а выход подключен к одному из входов элемента ИЛИ-НЕ, выход которого соединен с выходной щиной, а другой вход - с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя, первая и вторая входные шины соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы которого через формирователи объединены и подключены ко входу двухразрядного регистра сдвига.

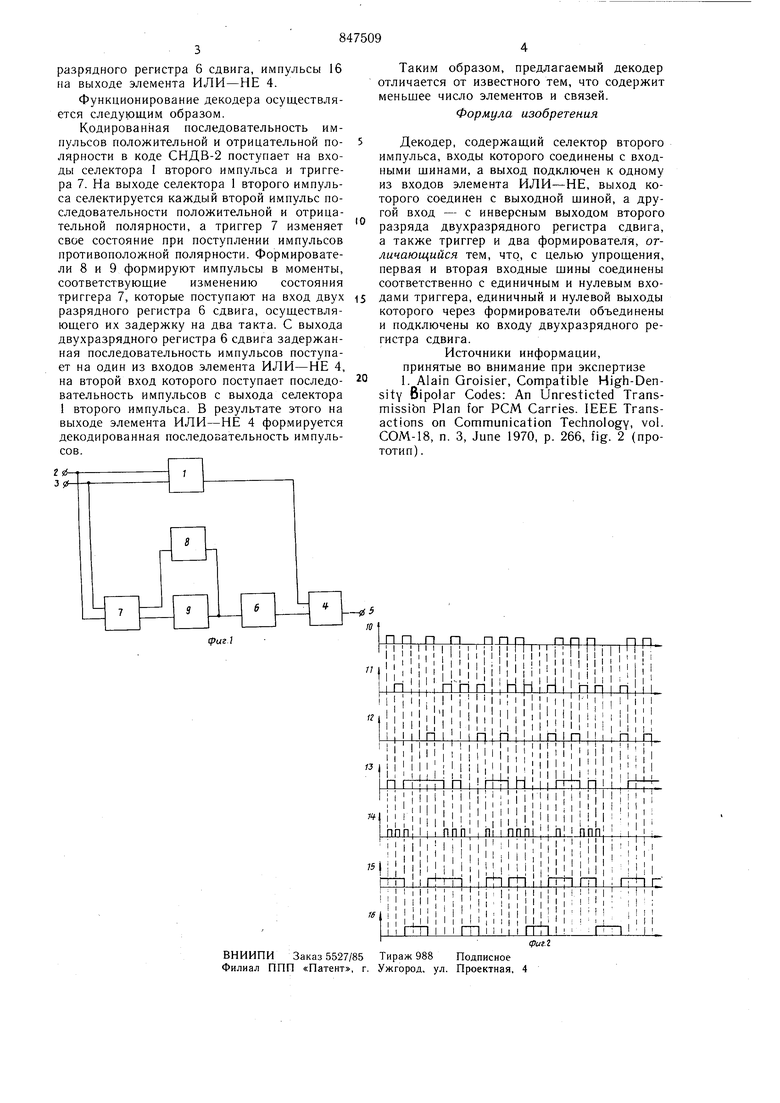

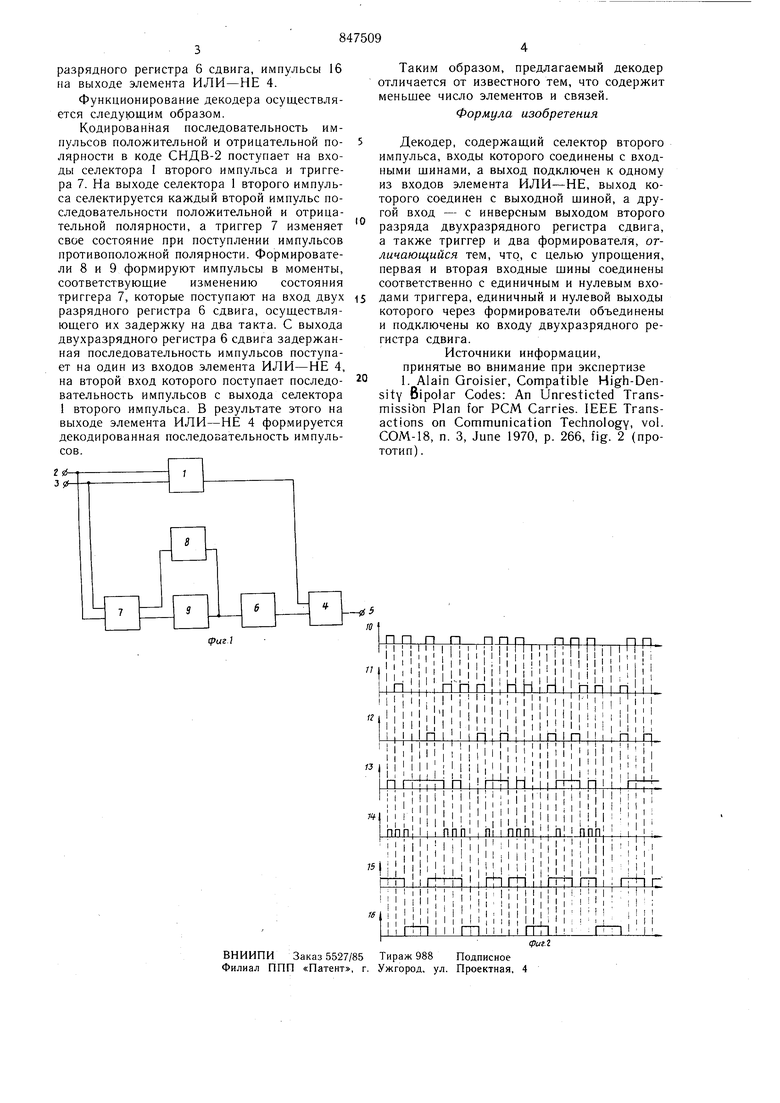

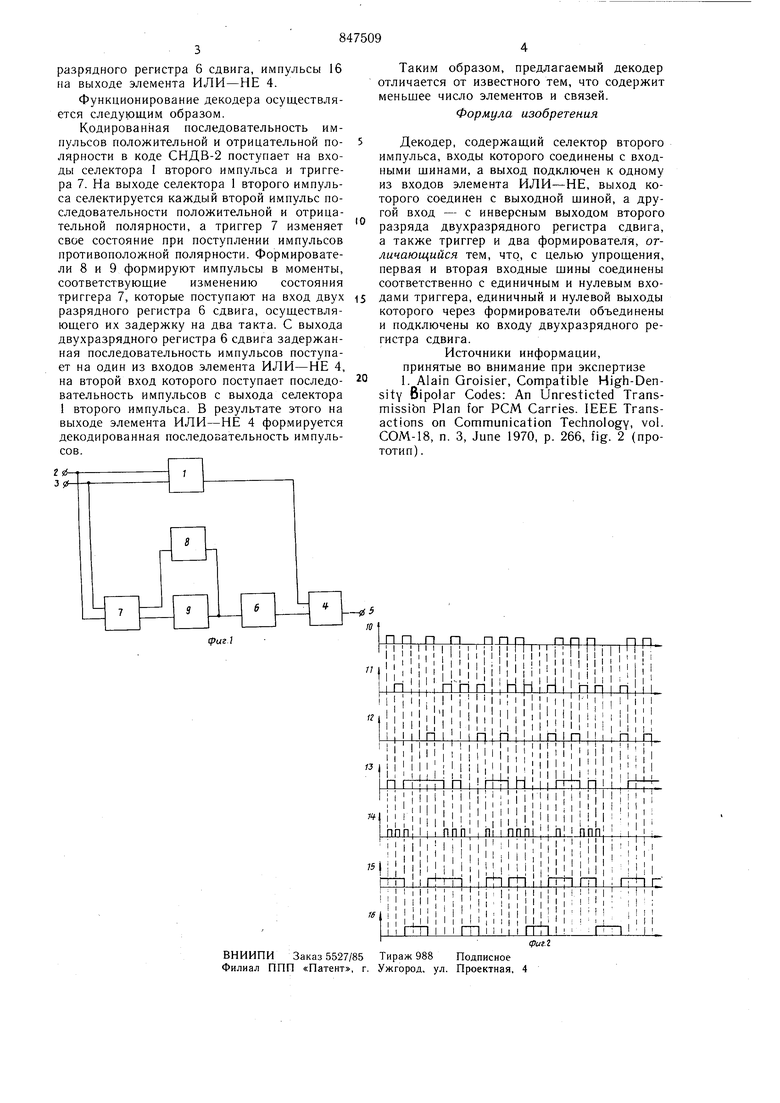

На фиг. 1 представлена функциональная схема декодера; на фиг. 2 - временная диаграмма функционирования декодера.

Схема (фиг. 1) содержит селектор 1 второго импульса, входы которого соединены с входными шинами 2 и 3, а выход подключен к одному из входов элемента ИЛИ-НЕ 4,

10 выход которого соединен с выходной шиной 5, а другой вход - с инверсным выходом второго разряда двухразрядного регистра 6 сдвига. Входные шины 2 и 3 соединены соответственно с единичным и нулевым вхоf J дами триггера 7, единичный и нулевой выходы которого через формирователи 8 и 9 обЪединены и подключены ко входу двухразрядного регистра 6 сдвига. На фиг. 2 обозначено: импульсы 10 на входной шине 2, импульсы 11 на входной шине 3, импульсы 12 на выходе селектора 1 второго импульса,

20 импульсы 13 и уровни на выходах триггера 7, импульсы 14 на входе двухразрядного регистра 6 сдвига, уровни 15 на выходе двухразрядного регистра 6 сдвига, импульсы 16 на выходе элемента ИЛИ-НЕ 4. Функционирование декодера осуществляется следующим образом. Кодированная последовательность импульсов положительной и отрицательной полярности в коде СНДВ-2 поступает на входы селектора I второго импульса и триггера 7. На выходе селектора 1 второго импульса селектируется каждый второй импульс последовательности положительной и отрицательной полярности, а триггер 7 изменяет свое состояние при поступлении импульсов противоположной полярности. Формирователи 8 и 9 формируют импульсы в моменты, соответствующие изменению состояния триггера 7, которые поступают на вход двух разрядного регистра 6 сдвига, осуществляющего их задержку на два такта. С выхода двухразрядного регистра 6 сдвига задержанная последовательность импульсов поступает на один из входов элемента ИЛИ-НЕ 4, на второй вход которого поступает последовательность импульсов с выхода селектора 1 второго импульса. В результате этого на выходе элемента ИЛИ-НЕ 4 формируется декодированная последовательность импульсов. Таким образом, предлагаемый декодер отличается от известного тем, что содержит меньшее число элементов и связей. Формула изобретения Декодер, содержащий селектор второго импульса, входы которого соединены с входными щинами, а выход подключен к одному из входов элемента ИЛИ-НЕ, выход которого соединен с выходной щиной, а другой вход - с инверсным выходом второго разряда двухразрядного регистра сдвига, а также триггер и два формирователя, отличающийся тем, что, с целью упрощения, первая и вторая входные щины соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы которого через формирователи объединены и подключены ко входу двухразрядного регистра сдвига. Источники информации, принятые во внимание при экспертизе 1. Alain Groisier, Compatible High-Density Bipolar Codes: An Unresticted Transmission Plan for PCM Carries. IEEE Transactions on Communication Technology, vol. COM-18, n. 3, June 1970, p. 266, fig. 2 (прототип).

Авторы

Даты

1981-07-15—Публикация

1979-05-30—Подача