(54) ДИСКРИМИНАТОР ЧАСТОТЫ СЛЕДОВАНИЯ

1

Изобретение относится к автоматике и вычислительной технике.

Известен селектор импульсов, содержащий одновибратор, согласующие элементы, элементы И-НЕ, диод и конденсатор, обеспечивающий регистрацию понижения частоты следования импульсов 1.

Недостатком устройства является то, что оно имеет импульсный выход, что требует дополнительных преобразований при использовании его в устройствах автоматики и не позволяет гибкое изменение значения пороговой частоты с высокой точностью.

Наиболее близким по технической сущности к предлагаемому является дискриминатор 4acTotbi следования импульсов, содержащий дещифратор, счетчик импульсов, подключенный к счетным входам к источнику импульсов эталонной частоты, а щиной обнуления - к источнику входных импульсов, два RS-триггера, элемент И и элемент задержки 2.

Недостатком известного дискриминатора является то, что точность сравнения периода импульсной последовательности с эталонным интервалом ограничена частотой задающего генератора (источника счетных ИМПУЛЬСОВ

импульсов) из-за неопределенности соотнощения фазы счетных и анализируемых импульсов. Кроме того, известный дискриминатор не позволяет осуществлять плавное изменение пороговой частоты, что снижает его функциональные возможности.

Цель изобретения - повыщение точности работь и расЩирёние функциональных возможностей устройства.

Поставленная цель достигается тем, что в известное устройство, содержащее счетf. чик импульсов, счетный вход которого подключей к выходу источника эталонной, частоты, вход сброса через элемент задержки - к S-входу первого RS-триггера, а выход через дещифратор - к R-вхрду второго RS-триггера, S-вход которого соединен с

15 выходом элемента И, первый вход которого подключен к шине входных импульсов, а второй вход - к прямому выходу первого RSтриггера, введены два ключа, элемент ИЛИ и дополнительный элемент задержки, выход которого соединен с входом сброса счетчика импульсов, а вход - i с щйной входных импульсов и первым входом элемента ИЛИ, второй вход которого подключен к выходу дешифратора, а выход - к R-входу первого RS-триггера, инверсный выход которого через первый ключ соединен с первым входом источника эталонной частоты, второй вход которого через второй ключ подключен к шине управляющих импульсов.

При этом источник импульсов эталонной частоты содержит операционный усилитель, выход которого непосредственно соединен с выходным формирователем импульсов, а через резистор - с первым входом источника эталонной частоты и первыми выводами первого и второго конденсатора, второй вывод первого из которых подключен к шине, а второго к второму входу источника эталонной частоты.

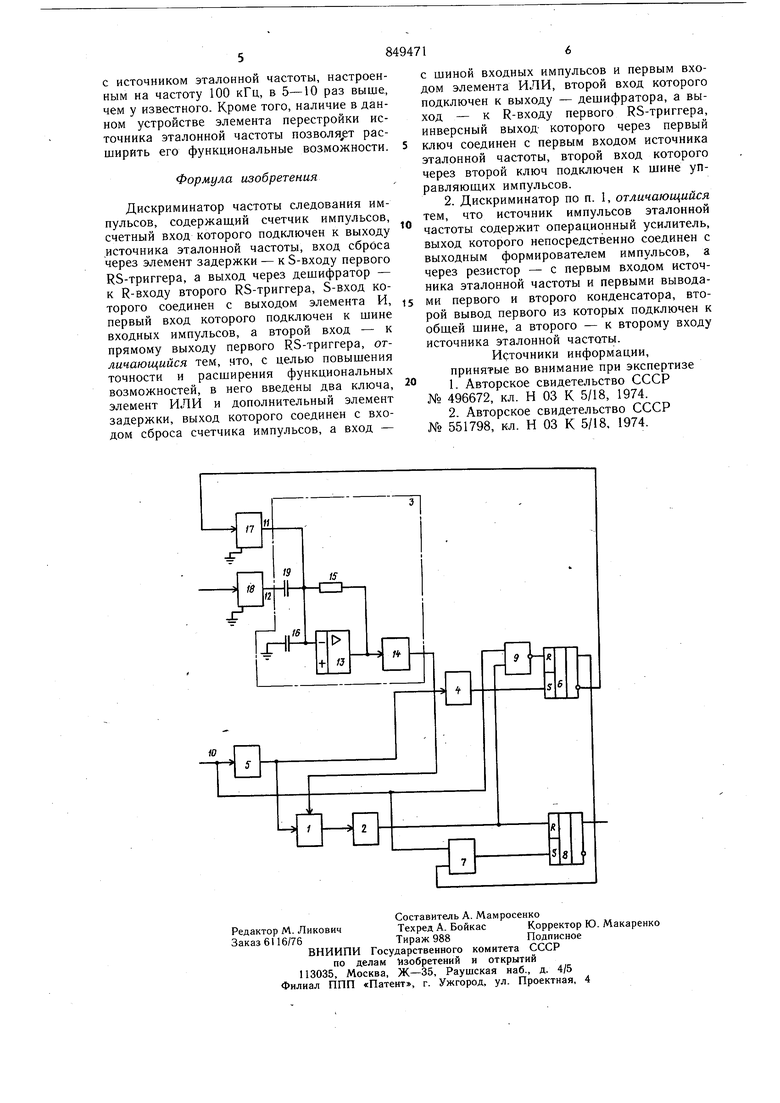

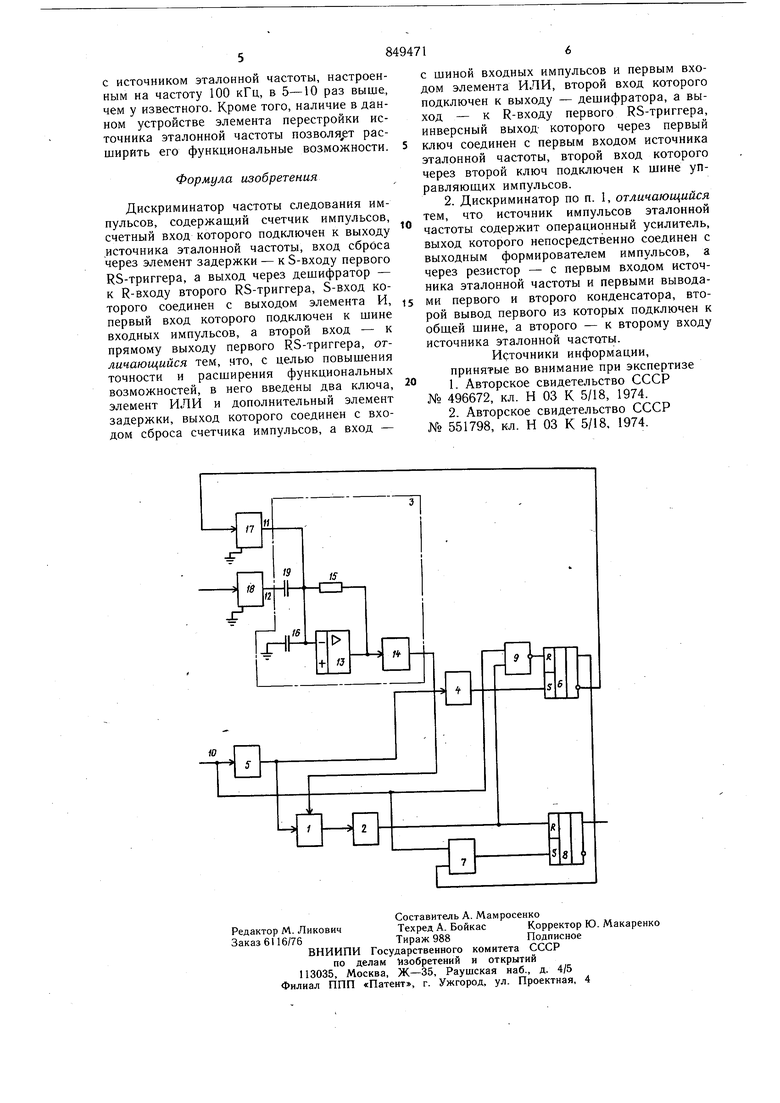

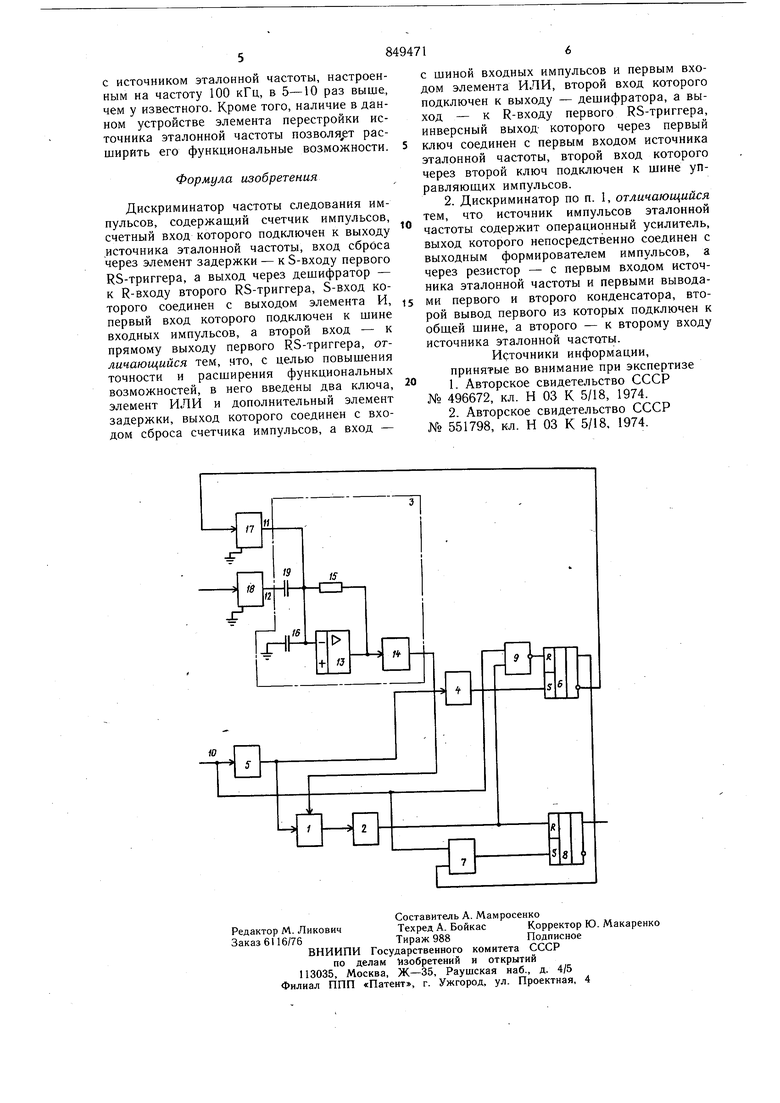

На чертеже изображена функциональная электрическая схема устройства.

Устройство содержит счетчик 1 импульса, дешифратор 2, счетный вход счетчика 1 подключен к источнику 3 импульсов эталонной частоты, а вход сброса - к входу эле.мента 4 задержки и выходу элемента 5 задержки, выход первого из которых соединен со S входом RS-триггера 6, прямой выход которого через элемент И 7 подключен к S-входу RS-триггера 8, R-вход которого соединен с выходом дешифратора 2 и элемент ИЛИ 9, второй вход которого подключен к входу элемента И 7, вход элемента 5 задержки - к шине 10 входных импульсов R-входом RS-триггера 6, инверсный выход которого подключен к входу 11, управляющему входу источника 3 импульса, содержащего усилитель 13, операционный выход которого подключен к входу формирователя 14 импульсов и через резистор 15- к его инверсному входу и первому выводу конденсатора 16, второй вывод которого соединен с общей шиной через ключ 17, а вход 12 управляющего источника 3 через ключ 18 подключен к щине управляющих импульсов, а вторые входы ключей подключены к общей шине, выход ключа 17 непосредственно, а выход ключа 18 через конденсатор 19 подключен к первому выводу конденсатора 16.

Дискриминатор частоты следования импульсов работает следующим образом.

От шины 10 входных импульсов сигнал поступает через элемент ИЛИ 9 на R вход RS-триггера 6, устанавливая его в исходное состояние. Сигнал с инверсного выхода RS-триггера 6 открывает ключ 17, при этом импульсы с источника 3 не поступают на вход счетчика 1 импульсов и он прекращает работу. Сигнал с прямого выхода RS-триггера 6 запрещает прохождение задержанного на элементе 5 задержки входного импульса на установку RS-триггера 8. Одновременно входной импульс, задержанный на элементе 5 задержки, устанавливает счетчик 1 импульса в исходное состояние, а через время, определяемое элементом 4 задержки, осуществляет переброс RS-триггера 6 в состояние, разрещающее прохождение импульСОВ через элемент И 7 и закрывающее ключ 17, при этом с источника 3 начинают поступать на счетчик 1 импульсов импульсы определенной фазы. Если интервал, формируемый на счетчике 1 импульсов, меньще периода ,следования входных импульсов, то на выходе дещифратора 2 появляется сигнал, перебрасывающий RS-триггер 6 в состояние, при котором прекращается поступление счетных импульсов и запрещается прохождение входного сигнала на З-вход RS-триггера 8, который установлен ранее по R-входу имцульсов с выхода дещифратора 2 в состояние, сигнализирующее, что входная частота ниже установленного значения. Следующий задержанный входной импульс вновь устанавливает счетчик 1 импульсов в исходное состояние, а затем перебрасывает RS-триггер 6. Процесс формирования эталонного интервала повторяется, при этом состояние RS-триггера 8 не изменяется. Если период частоты входных импульсов меньше формируемого эталонного интервала, то последующий входной импульс до окончания формирования интервала проходит на S-вход - RS-триггера 8 и R-вход RS-триггера 6, изменяя их состояние. Прекращается формирование и счет эталонных импульсов, а через время, определяемое элементами 4 и 5 задержки, последовательно осуществляется сброс счетчика 1 импульсов и. формирование нового эталонного интервала. С приходом следующего входного импульса до окончания формирования эталонного интервала процесс повторяется. Таким образом, потенциал на выходе RS-триггера 8 остается неизменным, сигнализирующим, что входная частота превысила заданное значение. При необходимости изменения эталонного интервала возможно путем подачи управляющего потенциала на ключ 18, осуществлять подключение дополнительного конденсатора 19 для изме1 ения эталонной частоты источника 3.

В устройстве точность сравнения периодов входных импульсов с эталонным интервалом определяется в основном длительностью задержки между остановом, сбросом и пуском источника 3 и счетчика 1 импульсов и при использовании элементов широкого применения не превыщает 1-2 мкс, в то время как в известных дискриминаторах точность сравнения лежит в пределах периода частоты источника 3 эталонной частоты, в связи с чем для получения точностных характеристик требуется увеличивать частоту источника 3, что не всегда возможно и приводит к увеличению разрядности счетчика 1 импульсов и усложнению дешифратора.

Предлагаемый дискриминатор частоты следования импульсов по сравнению с известными при одинаковой степени сложности обладает более высокой точностью работы, причем точность данного устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискриминатор частоты следования импульсов | 1980 |

|

SU959272A1 |

| Дискриминатор частоты следования импульсов | 1974 |

|

SU551798A1 |

| Логический накопитель импульсов | 1978 |

|

SU739746A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Преобразователь тока в частоту следования импульсов | 1985 |

|

SU1324113A1 |

| Цифровой измеритель скважностипРяМОугОльНыХ иМпульСОВ | 1979 |

|

SU808955A1 |

| Измеритель скорости звука | 1991 |

|

SU1796918A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

Авторы

Даты

1981-07-23—Публикация

1978-10-20—Подача