го

о

с

ON

Изобретение относится к импульсной технике и может быть использовано в качестве быстродействующего делителя частоты цифровых систем синтеза сеток стабильных частот и также в качестве элемента систем цифровой фазовой автоподстройкм частоты, используемых в передающих и приемных устройствах.

Цель изобретения - повышение надежности функционирования.

За счет введения устройства сброса в нуль элементов памяти, синхронного D- триггера, элемента задержки и управляемого электронного ключа, формирователя импульсов с соответствующими связями в рассматриваемом делителе с переменным коэффициентом деления после включения питающего напряжения и окончания записи исходной информации в первый и третий счетчики импульсов первый RS-триггер надежно устанавливается в правильное (нулевое) исходное состояние, за счет чего обеспечивается правильное исходное состояние первого и второго элементов совпадения, и надежное функционирование делителя в целом.

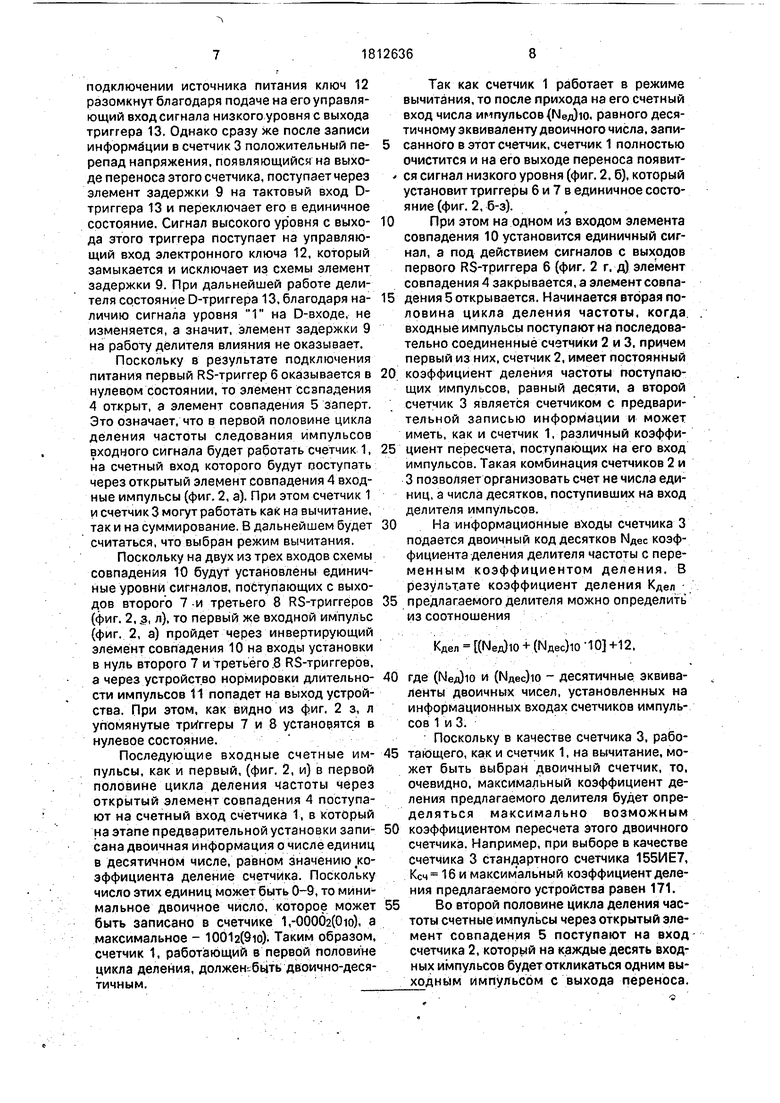

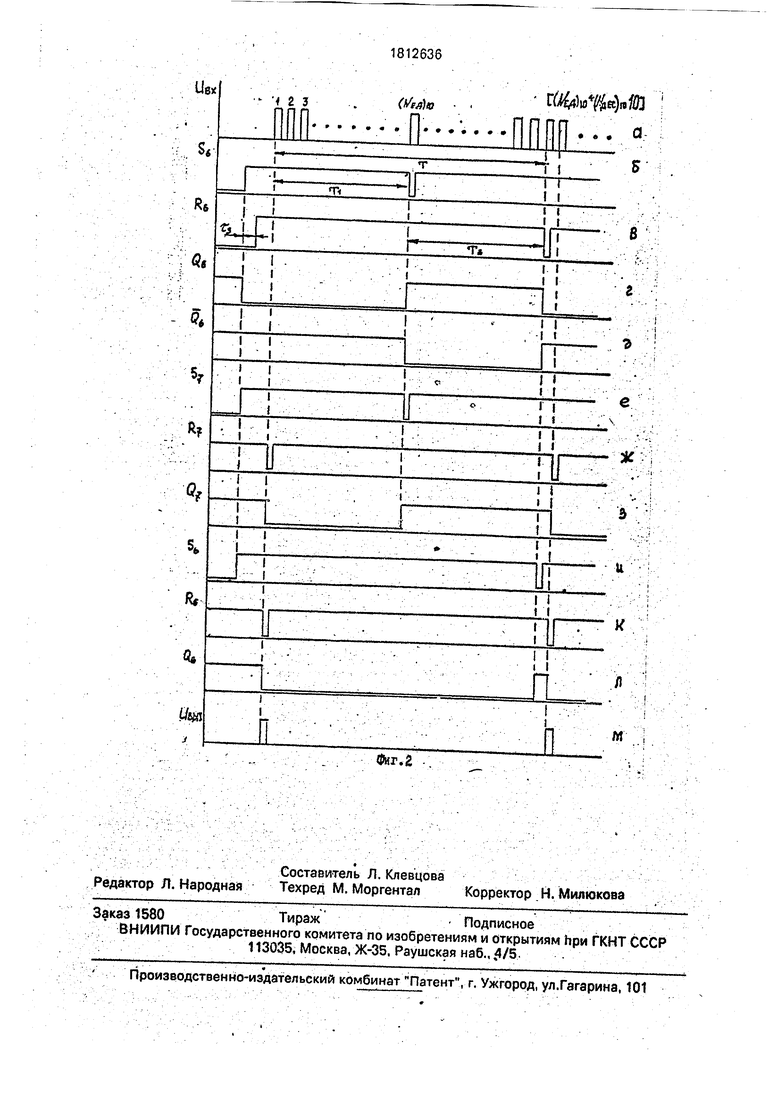

На фиг. 1 приведена электрическая функциональная схема делителя с переменным коэффициентом деления; на фиг. 2 - временные диаграммы, поясняющие принцип работы устройства.

Рассматриваемый делитель с переменным коэффициентом деления содержит первый, второй я третий счетчики 1, 2, 3 импульсов, причем выходы переноса первого и третьего счетчиков 1, 2, 3 соединены с их входами предварительной установки, а счетные входы первого и второго счетчиков 1, 2 через первый и второй элементы совпадения 4 и 5 подключены к входной шине.

Выход переноса первого счетчикз 1 нагружен на входы установки в единицу первого и второго RS-триггеров б и 7, вход установки в единицу третьего RS-триггера 8 связан с выходом переноса третьего счетчика 3 импульсов, который через элемент задержки 9 подключен ко входу установки в нуль первого RS-триггера б. Выход переноса второго счетчика 2.импульсов подсоединен к счетному входу третьего счетчика 3, прямой и инверсный выходы первого RS- триггера 6 соединены с вторыми (управляющими) входами второго и первого элементов совпадения соответственно. Прямые выходы.второго и третьего RS-триггеров 7 и 8 соединены с первым и вторым входами третьего элемента совпадения 10. Выход третьей схемы совпадения 10 связан со входами установки в нуль второгб и третьего

RS-триггеров 7 и 8 и со входом формирова- . теля 11 коротких импульсов.

Кроме того, между входом и выходом элемента задержки включен управляемый

электронный ключ 12, управляющий вход

которого подключен к выходу синхронного

D-триггера 13, причём вход сброса в нуль

этого триггера, как и входы сброса в нуль

первого, второго и третьего счетчиков 1,2,3

импульсов, подключен к выходу сброса в нуль элементов памяти 14. Тактовый вход синхронного D-триггера связан с выходом элемента задержки 9, а его информационный вход подключен к шине логической

5 единицы ;

Третий вход третьего элемента совпадения 10 подключен ко входной шине 15, а выход формирователя коротких импульсов подключен к выходной шине 16. кодовые

0 шины 17 и 18 подключены к информационным входам счетчиков 1 и 3 соответственно. Рассмотрение работы предлагаемого делителя с переменным коэффициентом деления следует начинать с момента включе5 ния питающего напряжения, так как правильная работа делителя определяется правильной исходной установкой RS-триггеров 8, 7 и 8 после включения питающего напряжения. .

0 при включении источника и отсутствия входного сигнала, который представляет собой последовательность униполярных импульсов (фиг. 2, а}, состояния упомянутых RS-триггероа будут определяться состояни5 ями выходов переноса счетчиков 1 и 3, а также уровнем сигнала на выходе элемента совпадения 10. Что касается сигнала на выходе элемента совпадения 10, то при отсутствии входного сигнала он будет иметь

0 высокий уровень, а сигналы с выходов переноса первого 1 и третьего 3 счетчиков могут быть как нулевыми, так и единичными. Для устранения этой неоднозначности в предлагаемый делитель введено устройство 14

5 сброса в нуль элементов памяти, выход которого подключен к входам установки в нуль счетчиков 1, 2 и 3, а также синхронного D- триггера 13. При включении источника пита-, ния устройство сброса 14 вырабатывает

0 короткий положительный импульс, обеспечивающий установку в нуль синхронного D-триггера 13, очистку регистров памяти счетчиков 1 и 3 и установку в нулевое состояние десятичнргЬ счетчика 2. При этом

5 управляемый электронный ключ 12 оказывается в разомкнутом состоянии, а выход переноса счетчика 3 будет подключен к входу установки в нуль RS-триггера б через элемент задержки 9. который может быть выполнен в виде асинхронного D-триггера,

Очистка регистров памяти счетчиков 1 и 3 обеспечит появление на их выходах переноса сигналов низкого уровня, которые поступят на входы RS-триггера 6 (фиг. 2 б, в). Это так называемая запрещенная комбина- 5 ция для RS-триггера с инверсным управлением, поэтому на выходах RS-триггера 6 будут высокие уровни сигналов (фиг, 2, г, д).

RS-триггеры 7 и 8 под воздействием сигналов низкого уровня с выходов переноса 10 счетчиков 1 и 3 (фиг. 2, е, и), а также сигнала высокого уровня с выхода элемента совпадения 10 (фиг. 2 ж, к) первоначально установятся в единичное состояние (фиг. 2, з, л).

Поскольку выходы переноса счетчиков 15 1 и 3 соединены с их входами предварительной установки, то благодаря воздействию на эти входы сигналов низкого уровня с выходов переноса в счетчики 1 и 3 производится запись информации с информацией- 20 ных входов каждого счетчика.

После окончания цикла записи этой информации на выходах переносов счетчиков 1 и 3 установятся высокие (единичные) уровни сигналов. При этом состояние второго и 25 третьего RS-триггеров 7 и 8 не изменяется (фиг. 2 з, л), а состояние первого RS-триггера 6 в обязательном порядке должно стать нулевым, так как только в этом случае элемент совпадения 4 будет открыт, а элемент сОв- 30 падения 5 - закрыт, что необходимо для правильной работы устройства в режиме деления, т.е. обеспечения заданного коэф- фициента деления начиная уже с первого цикла деления.35

Установка RS-триггера б в нулевое или единичное состояние определяется тем, на каком из двух входов S и R ранее появится сигнал единичного уровня, поступающий в первом случае с выхода переноса счетчика 40 1, а во втором - с выхода переноса счетчика. 3 (фиг. 2 б, в).

В устройстве - прототипе, где отсутствует элемент задержки 9, все определяется продолжительностями циклов записи ин- 45 формаций в счетчики 1 и 3. Если цикл записи информации в счетчик 1 длиннее, чем в счетчик 3, то RS-триггер б установится в единич- ное состояние и открытым окажется элемент совпадения 5, что приведет к не- 50 правильной работе делителя в режиме деления частоты следования импульсов. Однако и в противоположном случае, если длительность цикла записи информации в счетчике 3 будет больше, чем в счетчике 1, возможны 55 сбои правильной установки RS-триггера б, поскольку, во-первых, эта длительность далеко не строго фиксирована, что может ска- , заться при замене счетчиков, а во-вторых, она изменяется в зависимости от меняющихся условий окружающей среды. Кроме того, промежуток времени A t между моментом установки в исходное состояние счетчика 1 и моментом установки счетчика 3 может оказаться меньше, чем время, необходимое для переключения RS-триггера 6, а это также приведет к сбоям и неправильной работе делителя частоты следования импульсов.

Благодаря наличию в предлагаемой схеме делителя с переменным коэффициентом деления элемента задержки 9 возможна надежная установка требуемого состояния первого RS-триггера б, который, как было указано выше, после включения питающего напряжения и окончания записи информации в счетчики 1 и 3 обязательно должен установиться в нулевое состояние. Для надежного обеспечения этой цели время задержки гз элемента задержки 9 (фиг. 2 в) должно выбираться исходя из величины промежутка времени, необходимого для установки первого RS-триггера 6, а также должен обязательно учитываться возможный разброс параметров счетчиков 1, 3 и влияние воздействий окружающей среды.

Таким образомч благодаря введению устройства 14 сброса в нуль элементов памяти и элемента задержки 9 с их связями в предлагаемой схеме после окончания переходных процессов, вызванных включением источника питания, очисткой элементов па- мяТи и последующей записью информации в счетчики импульсов 1 и 3, на выходах переноса последних установятся сигналы высокого уровня, второй и третий RS-триггеры 7 и 8 окажутся в единичном состоянии, а первый RS-триггер будет в нулевом состоянии. Следует подчеркнуть, что в отличие от устройства - прототипа в данной схеме уже в первом цикле деления в счетчиках 1 и 3 будет записана правильная информация о коэффициенте деления частоты. Это обеспечивается принудительным обнулением всех элементов памяти при включении питания с помощью специального устройства 14, которое в простейшем случае представляет собой логический инвертор с времязадаю- щей RC-цепью на входе, подключенной к источнику питания. Наряду с обнулением счетчиков 1,2 и 3 происходит также сброс в нулевое состояние синхронного D-триггера 13, который предназначен для управления электронным ключом 12. В свою очередь, замыкание этого ключа выводит из работы элемент задержки 9, который в предлагаемой схеме необходим лишь на этапе перво- начального запуска делителя. После первоначального сброса D-триггера 13 при

подключении источника питания ключ 12 разомкнут благодаря подаче на его управляющий вход сигнала низкого уровня с выхода триггера 13. Однако сразу же после записи информёции в счетчик 3 положительный перепад напряжения, появляющийся на выходе переноса этого счетчика, поступает через элемент задержки 9 на тактовый вход D- триггера 13 и переключает его в единичное состояние. Сигнал высокого уровня с выхода этого триггера поступает на управляющий вход электронного ключа 12, который замыкается и исключает из схемы элемент задержки 9. При дальнейшей работе делителя состояние D-триггера 13, благодаря наличию сигнала уровня 1 на D-входе, не изменяется, а значит, элемент задержки 9 на работу делителя влияния не оказывает.

Поскольку в результате подключения питания первый RS-триггер б оказывается в нулевом состоянии, то элемент совпадения 4 открыт, а элемент совпадения 5 заперт. Это означает, что в первой половине цикла деления частоты следования импульсов входного сигнала будет работать счетчик 1, на счетный вход которого будут поступать через открытый элемент совпадения 4 входные импульсы (фиг. 2, а). При этом счетчик 1 и счетчик 3 могут работать как на вычитание, так и на суммирование. В дальнейшем будет считаться, что выбран режим вычитания.

Поскольку на двух из трех входов схемы совпадения 10 будут установлены единичные уровни сигналов, поступающих с выходов второго 7 -и третьего 8 RS-триггёров (фиг. 2, 3i л), то первый же входной импульс (фиг. 2, а) пройдет через инвертирующий элемент совпадения 10 на входы установки в нуль второго 7 и третьего .8 RS-триггеров, а через устройство нормировки длительности импульсов 11 попадет на выход устройства. Ори этом, как видно из фиг. 2 з, л упомянутые триггеры 7 и 8 установятся в нулевое состояние.

Последующие входные счетные импульсы, как и первый, (фиг. 2, и) в первой половине цикла деления частоты через открытый элемент совпадения 4 поступают на счетный вход счетчика 1, в который на этапе предварительной установки записана двоичная информация о числе единиц в десятичном числе, равном значению .коэффициента деление счетчика. Поскольку число этих единиц может быть 0-9, то минимальное двоичное число, которое может быть записано в счетчике 1,-00002(Ою), а максимальное - 1001a(9io). Таким образом, счетчик 1, работающий в первой половине цикла деления, должен быть двоично-десятичным.

Так как счетчик 1 работает в режиме вычитания, то после прихода на его счетный вход числа импульсов (Ne/0io, равного десятичному эквиваленту двоичного числа, записанного в этот счетчик, счетчик 1 полностью очистится и на его выходе переноса появит- ся сигнал низкого уровня (фиг. 2.6), который установит триггеры 6 и 7 в единичное состояние (фиг. 2, б-з).

При этом на одном из входом элемента совпадения 10 установится единичный сигнал, а под действием сигналов с выходов первого RS-триггера 6 (фиг. 2 г. д) элемент совпадения 4 закрывается, а элемент совпадения 5 открывается. Начинается вторая половина цикла деления частоты, когда, входные импульсы поступают на последовательно соединенные счетчики 2 и 3. причем первый из них, счетчик 2, имеет постоянный

коэффициент деления частоты поступающих импульсов, равный десяти, а второй счетчик 3 является счетчиком с предварительной записью информации и может иметь, как и счетчик 1, различный коэффициент пересчета, поступающих на его вход импульсов. Такая комбинация счетчиков 2 и 3 позволяет организовать счет не числа единиц, а числа десятков, поступивших на вход делителя импульсов.

На информационные входы счетчика 3 подается двоичный код десятков Мдес коэффициента деления делителя частоты с пере- менным коэффициентом деления. В результате коэффициент деления Кдел

предлагаемого делителя можно определить из соотношения

Кдел (Мея)ю + (МДес}10-Ю +12,

где (Мед)ю и (МДес)ю - десятичные эквиваленты двоичных чисел, установленных на информационных входах счетчиков импульсов 1 и 3.

Поскольку в качестве счетчика 3, работающего, как и счетчик 1, на вычитание, может быть выбран двоичный счетчик, то, очевидно, максимальный коэффициент деления предлагаемого делителя будет определяться максимально возможным

коэффициентом пересчета этого двоичного счетчика. Например, при выборе в качестве счетчика 3 стандартного счетчика 155ИЕ7, КСч 16 и максимальный коэффициент деления предлагаемого устройства равен 171.

Во второй половине цикла деления частоты счетные импульсы через открытый элемент совпадения 5 поступают на вход счетчика 2, который на каждые десять входных импульсов будет откликаться одним выходным импульсом с выхода переноса.

Импульсы с выхода счетчика 2 поступают на счетный вход.счетчика 3, в котором записан код Мдес. После очистки счетчика, т.е. после того, как во второй половине цикла деления на вход делителя поступят (Мдес)10 10 счетных импульсов, на выходе переноса счетчика 3 появится отрицательный перепад напряжения, который установит третий RS- триггер 8 в единичное состояние (фиг. 2 и к.л), а первый RS-триггер 6 в нулевое состояние (фиг. 2 в, г, д).

Важно, что на этом этапе элемент задержки 9 уже выключен из работы, так как а противном случае, при нулевом коде единиц (К|ед в 0), сигнал установки RS-триггера 6 в единицу с выхода переноса счетчика 1 мог бы опередить сигнал установки этого триггера в нуль. Это несомненно привело бы а нарушению режима работы делителя и установлению на один или несколько циклов ошибочного значения коэффициента деления.

Благодаря отключению с помощью управляемого электронного ключа 12 элемента задержки 9 RS-триггер б будет надежно установлен в нуль при любом значении ко-, зффициента Нед и обеспечит отпирание первого элемента совпадения.4 м ззпира- ние второго элемента совпадения 5. Кроме того, благодаря установке в единичное состояние третьего RS-триггера 8 уже на двух входах третьего элемента совпадения 10 будут установлены сигналы высокого уровня. Тем самым схема оказывается подготовленной к следующему циклу деления.

Окончание предыдущего цикла деления и начало следующего совпадает с приходом первого, после опрокидывания в нулевое состояние RS-триггера 6, счетного импульса- (фиг. 2 а, г, д). Поскольку в этот момент времени триггеры 7 и 8 находятся в единичном состоянии, создавая на двух входах элемента совпадения 10 сигналы высокого уровня, .то указанный счетный импульс.беспрепятственно проходит через трехвходо- вый элемент совпадения 10 и далее через устройство нормировки длительности импульсов 11 поступает на выход делителя (фиг. 2 м). Наряду с этим сигнал с выхода элемента совпадения 10 (фиг. 2 ж, к) устанавливает триггеры 7 и 8 в нулевое состояние. . :

В дальнейшем цикл работы предлагаемого делителя с переменным коэффициентом деления повторяется.

Формула, изобретения Делитель частоты с переменным коэффициентом деления, содержащий первый, второй и третий счетчики импульсов, при- 5 чем входы предварительной установки первого и третьего счетчиков импульсов соединены с их выходами переноса, а информационный входы этих счетчиков импульсов подключены к соответствующим

0 кодовым шинам, входная шина через первый и второй элементы совпадения соединена со счетными входами первого и второго счетчиков импульсов соотаетствен- . но, выход переноса второго счетчика им5 пульсов соединен со счетным входом третьего счетчика импульсов, вторые входы первого м второго элементов совпадения соединены соответственно с инверсным м прямым выходами первого RS-триггера, S0 входы первого м второго RS-трмггеров сое- дине ны с выходом переноса первого счетчика импульсов, S-вход третьего RS- триггера соединен с выходом переноса третьего счетчика импульсов, прямые выхо5 ды второго м третьего RS-триггеров соединены соответственно с первым и вторим входами третьего элемента совпадений, третий вход которого соединен с входной шиной, выход третьего элемента совпаде0 ния соединен с R-оходами второго и третьего RS-триггеров. содержащий также выходную шину, отличающийся тем, что, с целью повышения надежности функ- цмонированмя, в него введены устройство

5 сброса в 0м элементов памяти, О-триггер, элемент задержки, формирователь коротких импульсов, управляемый электронный ключ, причем устройство сбрйса в О элементов памяти подключено к входам уста0 новки в О первого, второго и третьего счетчиков импульсов, а также D-триггера, п элемент задержки включен между выходом переноса третьего счетчика импульсов и R-входом первого RS-триггера,

5 причем информационный вход управляемого электронного ключа соединен с выходом переноса третьего счетчика импульсов, выход - с выходом элемента задержки, а . управляющий вход - с выходом D-триггера,

0 тактовый вход D-триггера соединен с выхо дом элемента задержки, а его информаци.. онный вход подключен к шине логической

единицы, между выходом третьего элемента

совпадения и.выходной шиной - включен

5 формирователь коротких импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор частоты электроагрегата | 1985 |

|

SU1288891A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Устройство регулирования угла опережения зажигания | 1985 |

|

SU1694971A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Часовое устройство с полуавтоматической коррекцией | 1988 |

|

SU1670673A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

Применение: устройство относится к импульсной технике и может быть использовано в системах синтеза артот. Сущность изобретения: делитель частоты с переменным коэффициентом деления содержит: счетчики импульсов (1, 2, 3) элементы совпадения (4. 5, 10), RS-триг- геры (6, 7, 8), элемент задержки (9). формирователь (11) коротких импульсов, управляемый электронный ключ (12), D- триггер (13). устройство (14) сброса в нуль элементов памяти, входную и выходную шины (15,16) с соответствующими связями. 2 ил.. - -:- V

| Ребристый каток | 1922 |

|

SU121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| -ПТЭ | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-04-30—Публикация

1990-11-26—Подача