(54) СЕЛЕКТОР ЧАСТОТНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов | 1986 |

|

SU1406799A1 |

| Селектор импульсов | 1991 |

|

SU1810992A1 |

| Селектор импульсов | 1990 |

|

SU1780165A1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| Селектор импульсов | 1990 |

|

SU1758879A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Устройство синхронизации | 1982 |

|

SU1053306A1 |

| Устройство для передачи и приема многочастотных сигналов с относительной фазовой манипуляцией | 1984 |

|

SU1259500A1 |

| Селектор импульсов | 1977 |

|

SU738137A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1997 |

|

RU2137313C1 |

1

Изобретение относится к импульсной технике, в частности, к логическим устройствам частотной селекции, и может быть использовано для различения многочастотных гармонических сигналов.

Известен селектор частотных сигналов, содержащий блок формирования ряда взаимосмещенных последовательностей импульсов, схему совпадения и блок формирования Jыxpднoгo сигнала, основанный на выделении периода входного частотного сигнала и сравнении его с длительностью опорного импульса, вырабатываемого внутри устройства схемой формирования импульсов 1).

Однако это устройство имеет ограниченную область применения, поскольку позволяет различать только такие частотные сигналы, период следования Которых соответствует одной конкретной величине, определяемой настройкой схемы формирования опорного импульса.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее формирователь импульсов, выполненный в виде амплитудного ограничителя, и два канала селекции, каждый из которых состоит из последовательно соединенных блока логической селекции импульсов, вход которого соединен с выходом формирователя импульсов, и формирователя выходного сигнала. Период входного частотного сигнала выделяется формировате, лем импульсов, после чего анализируется блоком логической селекции в каждом канале на соответствие одной из двух конкретных величин, определяемых настройкой кана/1ов селекции. Устройство позволяет различать сигналы, представленные последовательной комбинацией двух одночастотных сигналов, т. е. решает задачу различения сигналов в системах частотно-временного уплотнения 2.

Недостатком этого устройства является ограниченность области его применения,

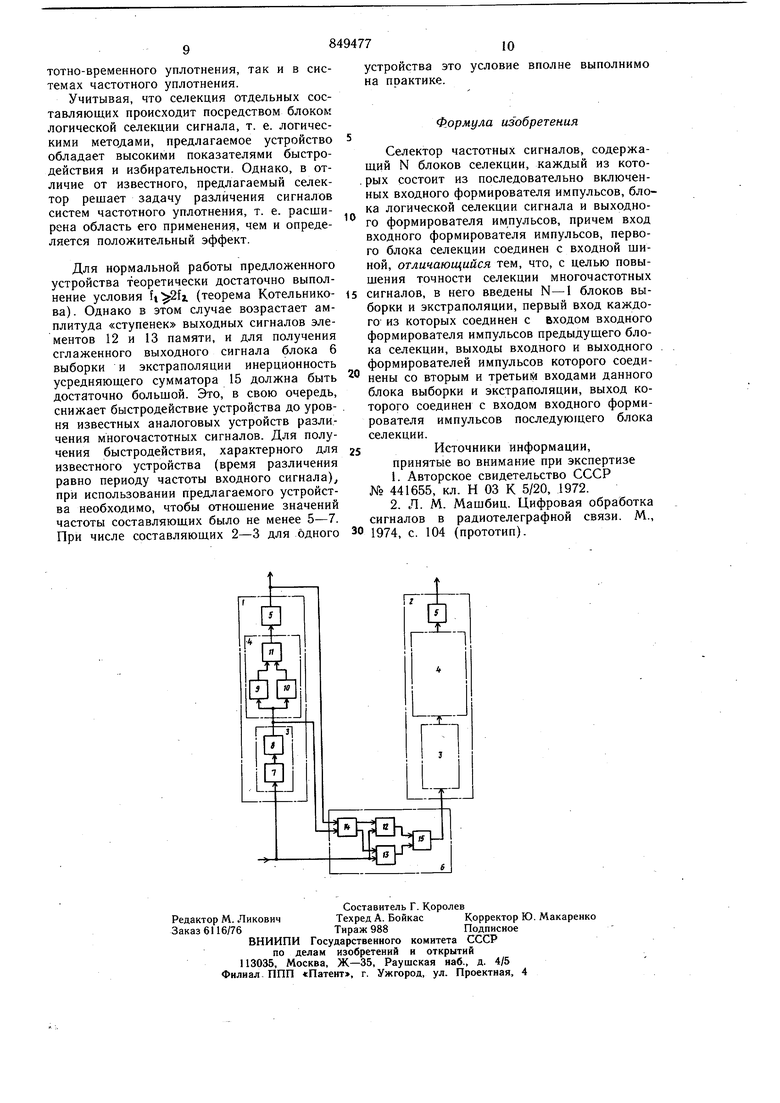

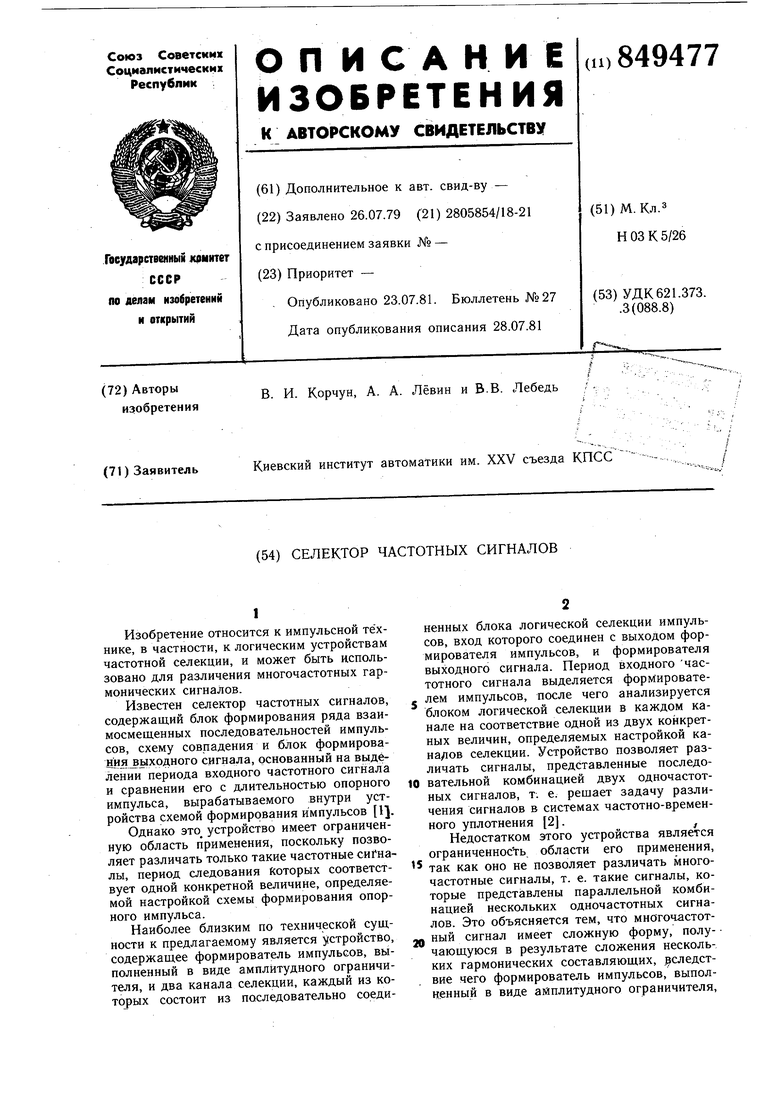

15 так как оно не позволяет различать многочастотные сигналы, т. е. такие сигналы, которые представлены параллельной комбинацией нескольких одночастотных сигналов. Это объясняется тем, что мноточастот2Q ный сигнал имеет сложную форму, полу- чающуюся в результате сложения нескольких гармонических составляющих, следст. вие чего формирователь импульсов, выполненный в виде амплитудного ограничителя. не позволяет выделить периоды конкретных составляющих. Поэтому это устройство нельзя применять, например, в системах частотйого уплотнения. Цель изобретения - повышение точности селекции многочастотных сигналов. Для достижения указанной цели в селектор частотных сигналов, содержащий N блоков селекции, каждый из которых состоит из последовательно включенных входного формирователя импульсов, блока логической селекции сигнала и выходного форт«ирователя импульсов, причем вход входного формирователя импульсов первого блока селекции соединен со входной щиной, введены N-1 блоков выборки и экстраполяции, первый вход каждого из которых соединен со входом входного формирователя импульсов предыдущего блока селекции, выходы входного и выходного формирователей импульсов которого соединены со вторым и третьим входами данного блока выборки и экстраполяции, выход которого соединен с входом входного формирователя импульсов последующего блока селекции. На чертеже приведена структурная электрическая схема устройства конкретного варианта для п 2. Селектор частотных сигналов содержит блоки L и 2 селекции, каждый из которых состоит из последовательно соединенных входного формирователя 3 импульсов, блока 4 логической селекции сигнала и выходного формирователя 5 импульсов. Кроме того, селектор содержит блок 6 выборки и экстраполяции, первый вход которого соедине со входом блока I селекции, второй вход соединен с выходом входного формирователя 3 импульсов блока 1 селекции, а третий вход - с выходом блока 1 селекции. блока б выборки и экстраполяции соединен со входом блока 2 селекции. Формирователь 3 импульсов состоит из последовательно соединенных дифференциатора 7 и компаратора 8. Блок 4 логической селекции сигнала содержит селектор 9 нижних частот и селектор 10 верхних частот. Входы селекторов 9 и 10 соединены с выходом формирователя 3 импульсов. Блок 4 содержит также элемент 11 совпадения, первый и второй входы которого соединены с выходом соответствующего селектора 9 и 10, а выход подключен ко входу формирователя 5. Блок 6 выборки и экстраполяции соде)жит элементы 12 и 13 памяти, первые входы которых подключены ко входу блока 1 селекции, блок 14 управления, первый вход которого соединен с выходом формирователя 3 импульсов, а второй - с выходом блока 1 селекции. Первый и второй выходы блока 14 управления соединены со вторым входом соответствующего элемента 12 и 13 памяти. Блок 6 содержит также усредняющий сумматор 15, первый и второй входы которого соединены с выходом соотзетствующего элемента 12 и 13 памяти, а выход подключен ко входу блока 2 селекции. Селектор частотных сигналов работает следующим образом. Входной многочастотный сигнал, поступающий га вход блока 1 селекции, для рассматриваемого числа блоков селекции представляет собой, в общем случае, сумму двух одночастотных составляющих VW--U,$,,i l7iS.Lh.aJr-fi, () где Ц, -амплитуда составляющих; l,,fi-значение частоты составляющих, причем i, .(I) Формирователь 3 импульсов работает в режиме выделения локальных экстремумов входного сигнала. Для этого входной сигнал блока 1 селекции поступает на вход дифференциатора 7, с помощью которого ° ч() v4t),u;cosiKt,t+iirijJ5.cosi7rf t. (г) с выхода дифференциатора 7 сигнал производной u(t) поступает на вход компаратора 8, предназначе нного для выделения моментов перехода сигнала u.(t) через ноль. Нулевые значения и (t) соответствуют локальным экстремумам (минимумам и максимумам) исходного сигнала и (t). При положительном знаке u(t) на выходе компаратора 8 устанавливается уровень логической «1, а при отрицательном - уровень логического «О. Интервал времени между двумя соседними переходами сигнала u(t) через ноль, равный полупериоду следования импульсов на выходе компаратора 8, можно определить из уравнения ц (Ь 0, т. е. 2lrf.,t lOr zU2CosZ3rf t 0 () Если амплитуды Ui и Uz составляющих равны между собой, то уравнение (4) преобразуется следующим образом. Cos atJTf .f Cosiirf t - оС5) Рещение уравнения (5) показывает, что полупериод Т/2 следования импульсов на выходе компаратора 8 ограничивается диапазоном, задаваемым неравенством arcSlrt (fi/f.,),,. 1 .OPcStnCfi./,) V И.-,- rrf. Учитывая при этом условие (2), можно установить, что частота f следования импульсов на выходе формирователя 3 блока 1 селекции ограничивается пределами неравенстваf.-&i,ix,. где А-Р.-др Следовательно, с выхода формирователя 3 на вход блока 4 логической селекции сигнала блока 1 поступает последовательность импульсов, частота следования которых определяется, в основном, частотой высшей составляющей fi. Блок 4 блока 1 настроен на выделение только тех импульсов, частота следования которых соответствует выражению (7). Выделение нужных импульсов происходит следующим образом. Импульсный сигнал с выхода формирователя 3 поступает на входы селектора 9 нйжних частот и селектора 10 верхних частот. Селекторы 9 и 10 представляют собой аналога фильтров нижних и верхних частот для импульсной техники. Принцип действия подобных селекторов основан на сравнении с помощью ключевого элемента периода входных импульсов с длительностью опорного сигнала, формируемого, например, ждущим мультивибратором. Селектор 9 безпрепятственно пропускает только те импульсы, частота следования которых меньще значения fi + , а селектор 10 - только те импульсы, частота следований которых больще значения . За пределами указанных диапазонов на выходах селекторов устанавливается уровень логического «О. Выходныр сигналы селекторов 9 и 10 поступают сЬответственно на первый н второй входы элемента 11 совпадения. Поскольку до момента, когда частота входных импульсов селекторов 9 и 10 меньще значения f«-ufi, и после того, как частота входных импульсов станет больще значения f(+ Д fi, на одном из входов элемента 11 совпадения будет присутствовать сигнал с уровнем логи ского «О,-поступающим с выхода соответствующего селектора 9 и 10, то, следовательно, на выходе элемента 11 совпадения отличный от нуля импульслыый сигнал формируется только в том случае, когда частота следования входных импульсов селекторов 9 и 10 будет соответствовать (7). При этом на обоих входах элемента 11 появляется синфазный импульсный сигнал, поступающий с выходов селекторов 9 и 10, работающих в режиме безпрепятстбенного пропускания импульсов. Выделенный с помощью элемента 11 совпадения импульсный сигнал поступает на вход формирователя 5, преобразующий входную нмпзльсную последовательность в постоянный уровень логической «Ь. При отсутствии импульсов на входе формйрователя 5 его выходной сигнал cooTBeTCTByet логическому «О. Следовательно, наличие на выходе блока 1 селекции сигнала с уровнем логической «Г свидетельствует о Уалнчии в спектре входного сигнала устройства составляющей с частотой fi. Входной многочастотный сигнал вида (1) поступает также на первые входы элементов 12 и 13 памяти блока 6 выборки экстраполяции. На вторые входы элементов 12 и 13 поступают сигналы с соответствующих выходов блока 14 управления. Если сигнал, поступающий с выхода блока 14 управления, равен логической «1, то на выходе соответствующего элемента 2 и 13 воспроизводится сигнал, поступающий на первые входы этих элементов,т. е. входной сигнал блока 1. Если же сигнал, поступающий с выхода блока 14 управления, принимает значение логического «О, то на выходе соответствующего элемента 12 и 13 запо минается мгновенное значение входного переменного сигнала, подаваемого на первые входы этих элементов, в момент перехода управляющего сигнала с единицы в ноль. Управляющие сигналы на выходах блока 14 формируются под воздействием двух переменных: импульсного сигнала, поступающего на первый вход этой схемы с выхода формирователя 3, и постоянного уровня, подаваемого на второй вход-блока 14 с выхода блока 1. При этом, если выходной сигнал блока 1 селекции равен логической 1, то на первом выходе блока 14 формируется последовательность коротких импульсов, положение которых определяется положительным фронтам выходных импульсов формирователя 3. Поскольку положительный фронт этих импульсов формируется в момент перехода производной u{t) через ноль из отрицательной в положительную область, то временное положение коротких импульсов на первом выходе блока 14 управления будет соответствовать моментам локальных минимумов входного многочастотного сигнала (1) блока 1 селекции. В этом случае элемент 12 работает в режиме последовательного взятия выборок и запоминания (синхронное детектирование). На выходе элемента 12 формируется ступенчатый сигнал U3(t)t, соответствующий выражениюUj(t l7jSLn2.3rfi{T,-l)-u, , (8) где TI - период высщей составляющей f,; i 0,1,2,3... (номер выборки). Параллельно на втором выходе блока 14 управления формируются короткие импульсы, положение которых определяется отрицательным фронтом выходных импульсов формирователя 3. Так как отрицательный фронт импульсов на выходе формирователя определяется моментом перехода производной и (t) через ноль из положительной в отрицательную область, то последовательность управляющих импульсов на втором выходе блока 14 будет соответствовать моментам локальных максимумов входного сигнала (1) блока 1 селекции. В этом случае на выходе элемента 13 памяти под действием управляющего сигнала, поступающего со второго выхода блока 14 на второй вход элемента 13, формируется в результате синхронного детектирования ступенчатый сигнал .ЬЦ(), описываемый выражением U.i,(t)l SLri23rfi(Tt-i-i-T,/2,)Ui . Выходные сигналы элементов 12 и 13 поступают соответственно на первый и второй входы усредняющего сумматора 15, значение выходного сигнала которого описывается выражением %(i) Усредняющий сумматор 15, представляющий собой, например, операционный усилитель ,с масщтабными сопротивлениями и параллельным апериодическим звеном в обратной связи, наряду с суммированием производит сглаживание «ступенек входных сигналов, в результате чего на выходе сумматора 15 формируется сигнал us (t) с достаточной точностью, описываемый выражениемMS Ct) Ц51« Z J jt.(4) Следовательно, после прохождения сигнала вида (I) через блок 6 выборки и экстраполяции из спектра этого сигнала исключается составляющая с частотой fi. При этом о наличии этой составляющей в исходном сигнале свидетельствует уровень логической «1 на выходе блока 1 селекции. С выхода блока б сигнал U5(t) поступает на вход блока 2 селекции. Формирователь 3 блока 2 выполняет последовательно дифференцирование сигнала, U5(t) (с помощью дифференциатора 7) и фиксирование моментов перехода производной U5(t) через ноль (с помощью компаратора 8). Очевидно, что частота следования выходных импульсов формирователя 3 блока 2 селекции равна fa. Блок 4 логической селекции сигнала этого блока настроен таким образом (путем установления границ срабатывания, селекторов 9 и 10, которые для блока 2 равны, соответственно, fi+Ati и fi-Afi), что импульсный сигнал с частотой fi беспрепятственно проходит на вход формирователя 5, в результате чего на выходе формирователя 5 устанавливается уровень логической единицы. Уровень логической единицы на выходе блока 2 селекции свидетельствует о наличии составляющей с частотой fi в спектре входного сигнала устройства. Таким образом, для многочастотного сигнала вида (Л) реакция предлагаемого устройства выражена логическими единицами на выходах блоков 1 и 2 селекции. В том случае, когда входной сигнал устройства не содержит составляющую с частотой f-t, т. е. на вход блока 1 селекции поступает сигнал ) .ijt I Ml) то на выходе формирователя 3 блока 1 формируются импульсы, частота сле овання которых равна f2. Так как блок 4 логической селекции блока 1 настроен на;выделение импульсов, идущих с частотой от l-j-At, до ft+Afi, TD импульсную последовательность с частотой ft, поступающую с вых)да фррмирователя 3 на вход блока 4 блоки 1, блок 4 не пропустит. Вследствие этого ipa выходе 84 78 блока 1 устанавливается нулевой логический уровень, свидетельствующий об отсутствии составляющей с частотой f в спектре входного сигнала. Уровень логического «О, поступающий с выхода блока I на второй вход блока 14 управления блока 6 выборки и экстраполяции, переводит блок 14 в такой режим, что на его выходах устанавливается постоянный уровень логической «1. Этот сигнал поступает на вторые входы элементов 12 и 13 памяти, в результате чего на выходах элементов 12 и 13 воспроизводится сигнал, поступающий на первые входы этих схем, т. е. входной сигнал вида (12). Элементы 12 и 13 при этом работают в режиме слежения. Усредняющий сумматор 15 не вносит изменений в структуру сигнала (12); небольшое уменьщение амплитуды и изменение начальной фазы - вследствие наличия инерционности сумматора - не влияет на дальнейщую обработку этого сигнала. С выхода блока б выборки и экстраполяции сигнал поступает на вход блока 2 селекции. С помощью формирователя 3 выделяется импульсный сигнал с частотой fj, после чего посредством блока 4 осуществляется логический анализ этого сигнала на наличие составляющей с частотой fj. -При этом на выходе блока 2 селекции устанавливается уровень логической «1, свидетельствующий о наличии составляющей с частотой fi в спектре входного сигнала устройства. Если же входной сигнал устройства представлен в виде M(,5LnZ«-f,t,) т. е. на вход блока 1 селекции поступает одночастотный гармонический сигнал, то на выходе формирователя 3 этого блока формируется импульсная последовательность с частотой следования f. Так как положительный фронт выходных импульсов формирователя 3 совпадает с минимумами сигнала (13), а отрицательный фронт - с максимумами, то в результате синхронного детектирования входного одночастотного гармоничёского сигнала с помощью блока 6 выборки н экстраполяции на вход блока 2 селекции подается нулевой уровень сигнала. Следовательно, для рассматриваемого случая реакция предлагаемого устройства выражена единичным логическим уровнем на выходе блока 1 селекции (результат наличия составляющей с частотой f|) и нулевым уровнем на выходе блока 2 селекции (отсутствие составляющей с частотой fj). Таким образом, предлагаемый селектор частотных сигналов позволяет различать как одночастотные, так и многочастотные сигналы, выдавая при этом информацию о наличии или отсутствии отдельных составляющих в виде логических уровней «1 и «О на выходах соответствующих блоков селекции. Следовательно, устройство может быть использовано как в системах час

Авторы

Даты

1981-07-23—Публикация

1979-07-26—Подача