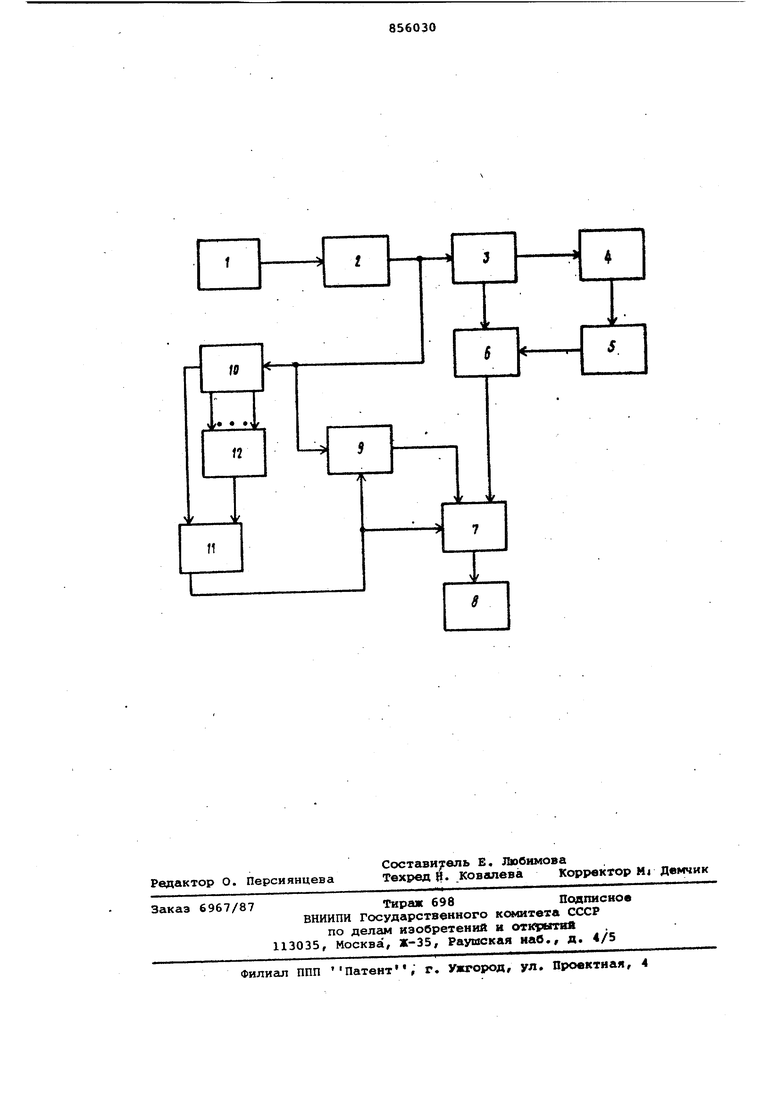

ства на различных скоростях телеграфирования, на вход формирователя 3, где производится дальнейшее понижение частоты следования импульсов. Стартстопный распределитель 4 совместно с формирователем 5 формирует испытательные стартстопные комбинации следующие со скоростью телеграфирования, которые поступают через блок 6 на вход блока 7. Импульсы с выхода первого делителя 2 частоты поступают также на второй делитель 10 частоты, который увеличивает период следования импульсов до величины, превышакнцей период следования кодовых ком бинаций. Дооифратор 12 дешифрирует состояние второго делителя 10 частоты, которое определяет начало формирования заданной длительности импуль са дробления, и сигнал с выхода дешифратора 12 устанавливает триггер 11 в разрешающее состояние. Конец формирования заданной длительности импульса дробления определяет сигнал с последовательного выхода второго делителя 10 частоты, который устанавливает триггер 11 в исходное состояние. В результате на выходе триг гера 11 формируется импульс заданной длительности, который поступает на вход блока 7 для поражения элементов кодовой комбинации искажением одиночные дробления . С выхода блока 7 искаженные кодовые комбинации поступают на блок 8. В режиме измерения исправляющей способности по пачкам дроблений работа устройства происходит ангшогичн описанной, только поражение элементов кодовой комбингщии осуществляется серией.импульсов, поступающих с выхода формирователя 9 на вход блока 7.В режиме измерения исправляющей способности по краевым искажениям второй делитель 10 частоты,триггер 1 дешифратор 12 и формирователь 9 отключаются. Импульсы с задающего гене ратора 1 через первый делитель 2 частоты поступают на вход формировател 3, где формируются импульсы, необходимые для поражения краевыми искажениями элементов кодовых комбинаций Э блокр 6 испытательные стартстопные комбинации, сформированные стартстоп-. ным распределителем 4 совместно с форкп рователем 5, подверггиотся краевым искажениям на требуемую величину С выхода блока 6 искаженные кодовые комбинации поступают через блок 7 на блок 8. В предлагаемом устройстве благодаря введению дешифратора, исключению из устройства элемента И и сокра щению количества соединений достигается упрощение устройства и повышение его надежности. Формула изобретения Устройство для измерения исправляющей способности приемника телеграфных сигналов, содержащее последовательно соединенные задгиощий генератор, первый делитель частоты, формирователь сигнала управления, стартстопный распределитель импульсов. формирователь испытательного сигнала, блок искажений сигнала, второй вход которого соединен со вторым выходом формирователя сигнала управления, блок ввода дроблений сигнгша и блок согласования, а также последовательно соединенные второй делитель частоты, триггер и формирователь пачек дроблений, второй вход и выход которого соединены соответственно с объединеннытим входами второго делителя частоты и формирователя сигнала управления и со вторым входом блока ввода дроблений сигнала, третий вход которого соединен с выходом триггера, отли.чаю1цееся тем, что, с целью упрощения устройства путем сокращения общего числа элементов, введен дешифратор, при этом выходы разрядов второго делителя частоты соединены с соответствующими входами дешифратора, рыход которого соединен со вторым входом триггера. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 696623, кл. Н 04 t 11/08, 1978 (прототип).

Авторы

Даты

1981-08-15—Публикация

1979-06-19—Подача