(54) АНТИЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Экспоненциальный функциональный преобразователь | 1978 |

|

SU752373A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Устройство для ускоренного заряда аккумуляторной батареи | 1988 |

|

SU1557630A2 |

| Устройство автоматического регулирования выходной мощности передатчика | 1989 |

|

SU1707763A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1495766A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Антилогарифмический функциональный преобразователь | 1980 |

|

SU920763A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| СПОСОБ УПРАВЛЕНИЯ ИМПУЛЬСНЫМ СТАБИЛИЗАТОРОМ НАПРЯЖЕНИЯ | 2012 |

|

RU2509337C1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU836794A1 |

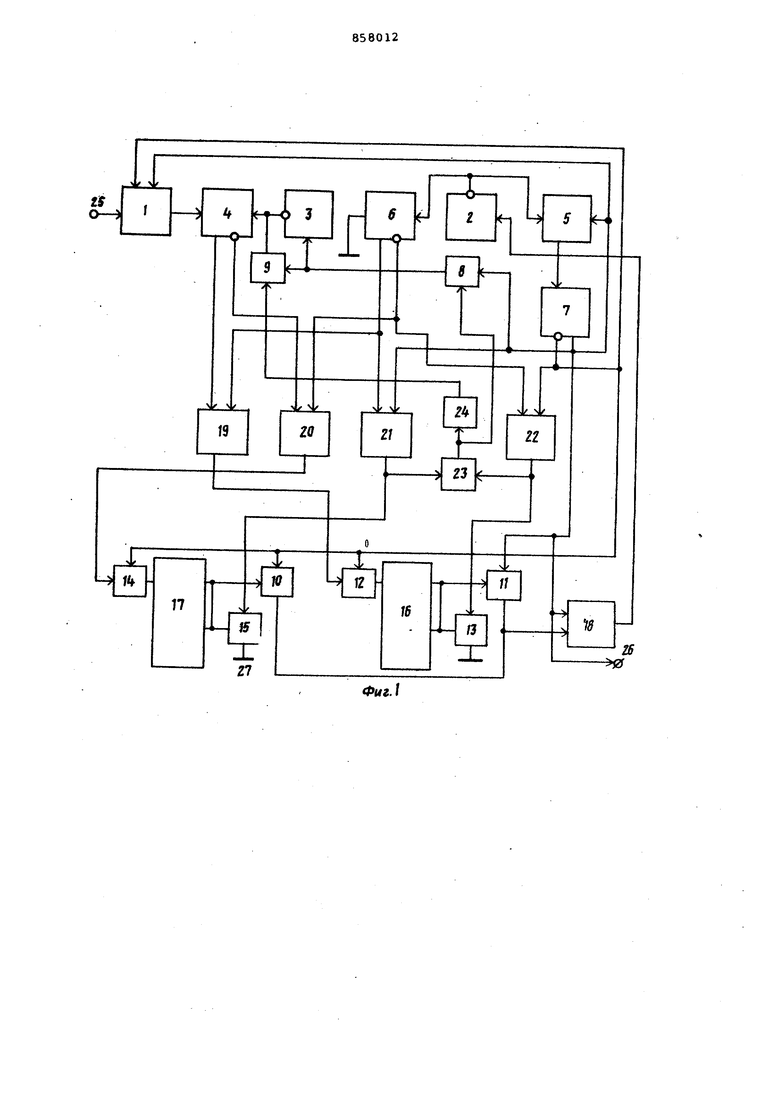

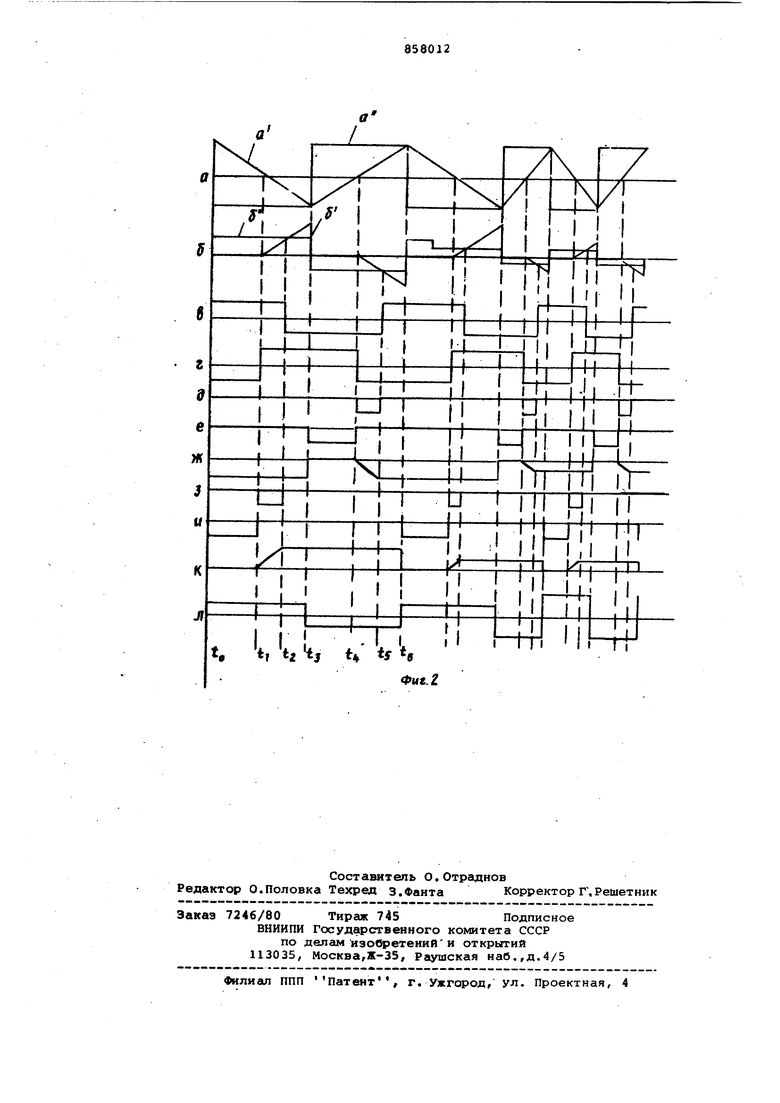

Изобретение относится к устройствам функционального преобразования сигналов, в частности к устройствам преобразования сигналов по экспоненциальному закону, и может быть испол зовано в вычислительных машинах. Известен антилогарифмический функ циональный преобразователь, содержащ генератор импульсов и КС-цепь, соеди ненную через диод с источником напря жения заряда и через управляемый ключ - со сглаживающим фильтром, бло вычитания, входы которого подключены к источнику и к генератору импуль сов, и дополнительный управляемый ключ, через который резистор КС-цепи связан с шиной нулевого потенциала, причем управляющий вход дополнительного ключа соединен с выходом блока вычитания, а управляющий вход первого ключа - с выходом генератора импульсов t4 . Недостаток - пониженная точность из-за паразитного разряда конденсато RC-цепи через сопротивление закрытого диода и низкое быстродействие, обусловленной наличием сглаживающего фильтра на выходе. Наиболее близким к предложенному являемся антилогарифмический преобра ователь, содержащий стабилизатор амплитуды опорных импульсов, ренераор линейного напряжения, дифференциальный усилитель, первый формь ватель зкспоненциального напряжения, первую и вторую схемы сравнения, первый элемент И, зарядный и разрядный ключи, первый, второй, третий и четвертый ключи, выход зарядного ключа соединен с входом первого формирователя зкспоненциального напряжения,овыход которого подключен к входу разрядного ключа, выход генератора линейного напряжения присоединен к первому входу первой схемы сравнения, прямой выход которого соединен с первым входом первого элемента И, выход которого подключен к управляющему входу зарядного ключа, выход второй схемы сравнения присоединен к входу стабили-, затора амплитуды опорных импульсов С2. Недостатком этого устройства также является низкая точность работы. Цель изобретения - повышение точности работы. Поставленная цель достигается тем, что в известный антилогарифмический преобразователь введены амплитудный модулятор, интегратор, инвертор, элемент ИЛИ, второй, третий и четвертый элементы И, второй формирователь экспоненциального напряжения и дополнительные зарядный и разрядный ключи, третья схема срав нения, выход амплитудного модулятора соединен с вторым входом первой схемы сравнения, инверсный выход ко.торой подключен к первому входу второго элемента И, выход которого присоединен к управляющему входу дополнительного зарядного ключа, выход которого подключен к входу второго формирователя экспоненциальн го напряжения, выход стабилизатора амплитуды опорных импульсов соединен с первыми входами амплитудного модулятора второй схемы сравнения, третьего элемента И, с входом первого ключа, с управляющим входом-четве того ключа и инвертирующим входом дифференциального усилителя, выход которого подключен к входу интеграто первый вход третьей схемы сравнения присоединен к шине нулевого потенциала, выход интегратора соединен с вторыми входами второй и третьей схем сравнения, выход первого ключа присоединен к входам второго ключа и генератора линейного напряжения, к в ходу которого подключен выход второг ключа, выход третьей схелнсрайнения соединен с вторыми входами первого и третьего элементов И, инверсный вы ход стабилизатора амплитуды опорных импульсов подключен к второму входу амплитудного модулятора, к первому входу четвертого элемента И, к входа зарядного ключа и дополнительного зарядного ключа и к управляющему входу третьего ключа, выход второго формирователя экспоненциального напр жения соединен с входами третьего ключа и дополнительного разрядного ключа, выход которого присоединен к выходу разрядного ключа и к шине, нулевого потенциала, инверсный выход третьей схемы сравнения соединен с вторыми входами второго и четвертого элементов И, выход третьего элемента И подключен к управляющему входу дополнительного разрядного ключа и к первому входу элемента ИЛИ, второй вход которого присоединен к -выходу четвертого элемента Ник управляющему входу разрядного ключа, выход элемента ИЛИ соединен с входЬм инвертора и управляющим входом первого ключа, выход инвертора подключен к управлякадему входу второго ключа, третий вход амплитудного модулятора являетеjf входом антилогарифмического преобразователя, выходы третьего и четвертого ключей присоединены к леинвертирующему входу дифференциального усилителя, вход четвертого ключа соединен с выходом первого форми рователя экспоненциального напряжени выход стабилизатора амплитуды опорных импульсов является выходом антилогарифмического преобразователя. На фиг.1 изображена функциональная схема предложенного антилогарифмического преобразователя на фиг.2.напряжения, действующие в преобразователе. Преобразователь содержит амплитудный модулятор 1, интегратор 2, генератор 3 линейного напряжения, первую 4, вторую 5 и третью 6 схекы сравнения, стабилизатор 7 амплитуды опорных импульсов, первый 8, второй 9 третий 10 и четвертый 11 ключи, зарядный 12 и разрядный 13 ключи, дополнительные зарядный 14 и разрядный 15 ключи, первый 16 и второй 17 формирователи экспоненциального напряжения, дифференциальный усилитель 18, первый 19, второй 20, третий 21 и четвертый 22 элементы И, элемент ИЛИ 23, инвертор 24, вход 25 и выход 26 антилогарифмического преобразователя, шина 27 нулевого потенциала. На фиг.2 изображены напряжения; интегратора 2, а - стабилизатора 7 амплитуды опорных импульсов, б - генератора 3 линейного напряжения, б - амплитудного модулятора 1, в - первой схемы 4 сравнения, г - третьей схемы 6 сравнения, д - первого элемента И 19, е - третьего элемента И 22, ж - первого формирователя 16 экспоненциального напряжения, 3 - второго элемента И 20, и - третьего элемента И 21, к - второго формирователя 17 экспоненциального напряжения, л - дифференциального усилителя 18. Рассмотрим работу устройства, начиная с момента времени t (фиг.2). В этот момент с выхода интегратсчза 2 снимается положительное напряжение- (фиг.2а),а на выходе второй схемы 5 сравнения и стабилизатора 7 амплитуды опорных импульсов устанавливается отрицательное напряжение, так как выходное напряжение интегратора 2 подано на инвертирующий вход второй схемы 5 сравнения, на. первый вход которой подается отрицательное напряжение с выхода блока 7, то на выходе амплитудного модулятора 1 устанавливается положительное напряжение, первый ключ 8 размыкается, а второй ключ 9 замыкается, в результате чего на выходе генератора 3 линейного напряжения устанавливаетая нулевой потенциал (фиг. 26) . Так как на второй вход первой схемы 4 сравнения подается положительное напряжение с выхода амплитудного модулятора 1, а на первый вход - нулевой потенциал с выхода генератора 3 линейного напряжения, то на ее выходе устанавливается положительное напряжение, а на инверсном - отрицательное (на фиг.2в показана диаграмма напряжений, снимаемых с п мого выхода) . На второй вход третьей схемы 6 сравнения подается положительное напряжение с выхода интегратора 2, а ее первый вход соединен с шиной 2 нулевого потенциала, следовательно, на выходе третьей схемы б сравнения имеется отрицательный потенциал (фиг.2г), а на инверсном - положите ный. В момент времени t (фиг.2) заря ный ключ 12 разомкнут нулевым потен циалом с выхода первого элемента И 19 (фиг.2д), так как на его входах действуют отрицательный потенциал с выхода третьей схемы 6 сравнения (фиг.2г) и положительный потенциал с выхода первой схемы 4 сравнения (фиг.2в). Разрядный ключ 13 также находится в разомкнутом состоянии, так как на входах четвертого элемента И 22 действуют положительные сигналы с инверсных выходов третьей схемы 6 сравнения и стабилизатора 7 амплитуды опорных импульсов (фиг.2е). Дополнительный зарядный ключ 14 разомкнут нулевым потенциалом с выхода второго элемента И 20 (фиг.2з) на входах которого действуют отрица тельный потенциал с инверсного выхо да первой, схемы 4 сравнения и поло.жительный потенциал с выхода третьей cxeNbJ 6 сравнения. Дополнительный разрядный ключ 15 замкнут отрицательным потенциало с выхода третьего элемента И 21 (фиг.2и), на входах которого действуют отрицательные потенциалы с прямых выходов третьей cxejvw 6 срав нения (фиг.2г) и стабилизатора 7 ам плитуды опорных импульсов (фиг.2а) Первый ключ 8 разомкнут нулевым потенциалом, снимаемым с выхода эле мента ИЛИ 23, а второй ключ 9 замкнут отрицательным потенциалом с ил да инвертора 24. Четвертый ключ 11 замыкается отрицательным потенциало с выхода стабилизатора 7 амплитуды опорных импульсов (фиг.2а), а третий ключ 10 замыкается положительным потенциалом с его инверсного выхода. Таким образом, к неинвертирующему входу дифференциального усилителя 18 оказывается приложенным отрицательное напряжение, снимаемое с выхода первого формирователя 16 экс поненциального напряжения (фиг.2ж) , к инвертирующему входу дифференциального усилителя 18 приложено отрицательное напряжение с выхода стаби лизатора 7 амплитуды опорных импуль сов. Под действием положительного н.ап ояжения, поступающего на вход интег ратора 2, последний вырабатывает линейно спадающее напряжение (фиг.2а11, В момент t (фиг.2) уровень напряжения интегратора 2 снижается до нуля. При этом срабатывает третья схема б сравнения,переходя иэ одного устойчивого состояния в другое и меняя полярность напряжения на своих выходах (фиг.2г) на противоположную. В результате этого оба сигнала на входах схемы второго элемента И 20 становятся отрицательными и вырабатывают замыкающий сигнал (фиг.2з) для дополнительного зарядного ключа 14, который замыкает цопь заряда . второго формирователя 17 экспоненциального напряжения от положительного напряжения, снимаемого с инверсного выхода стабилизатора 7 амплитуды опорных импульсов. . Кроме того, в момент времени t первый ключ 8 замыкается отрицательным потенциалом с выхода элемента ИЛИ 23, а второй ключ 9 размыкается нулевым потенцисшом инвертора 24. Благодаря этому генератор 3 линейного напряжения начинает вырабатывать линейно нарастающее напряжение, которое в момент времени t сравнивается с положительным напряжением с выхода амплитудного модулятора 1 (фиг.26), в результате чего срабатывает первая схема 4 сравнения, меняя полярность своих выходных сигналов на противоположную. В результате срабатывания первой сх.емы 4 сравнения на вход второго элемента И 20 с инверсного выхода первой схемы 4 сравнения подается положительное напряжение, при этом второй элемент И 21 формирует на выходе нулевой потенциал и дополнительный зарядный ключ 14 размлкается (фиг.2з), фиксируя определенное напряжение второго формирователя 17 экспоненциального напряжения (фиг.2к). В момент Ьремени t3 (фиг.2) значение линейно спадающего напряжения интегратора 2 достигает равенства с опорным напряжением (фиг.2а). При этом вторая схема 5 сравнения лавинообразно переходит из одного устойчивого состояния в другое, меняя полярность напряжения на выходах стабилизатора 7 аг«тлитуды импульсов. При этом на его выходе устанавливается положительный потенциал (фиг.2а), а на инверсном - отрицательный. - После опрокидывания второй схекы 5 сравнения начинается следующий цикл преобразовашия, при этом в результате изменения лолярности управляющих сигналов, снимаемых с выходов стабилизатора 7 амплитуды опорных импульсов на входах амплитудного модулятора 1, на его выходе устанавливается отрицательное напряжение, равное входному напряжению (фиг.26). Разрядный ключ 13 замыкается, обнуляя

первый формирователь 16 экспоненциального напряжения.Первый ключ 8 размыкается, а второй ключ 9 aaivwкается, в результате чего генератор 3 линейного напряжения также приводится в исходное нулевое состояние (фиг, 26), Четвертый ключ И раз№лкается положительным сигналом с выхода стабилизатора 7 амплитуды опорных импульсов (фиг.2а), а третий ключ 10 замыкается отрицательным напряжением с его инверсного выхода в результате к неинвертирующему входу оказывается приложенным положительное напряжение, зафиксированное первом палупериоде преобразования на выходе второго формирователя 17

экспоненциального напряжения (фиг.2к К инвертирующему входу дифференциального усилителя 18 в этот момент прикладывается положительное напряже ние с прямого выхода стабилизатора 7 амплитуды опорных импульсов. На выходе дифференциального усилителя 18 формируется отрицательное напряжение (фиг,2л), под действием которого интегратор 2 начинает формировать линейно нарастающее напряжение {фиг.2а) ,

В момент времени t4. (фиг.2) напряжение на выходе интегратора 2 вновь достигает нулевого уровня, при этом опрокидывается третья схема 6 сравнения, меняя полярность напряжения на своих выходах (фиг,2г). Благодаря этому первый элемент И 19 вырабатывает отрицательное напряжение .. (фиг.2д) , зальакающее зарядный ключ 1 Четвертый элемент И 22 вырабатывает нулевой потенциал (фиг,2е), в результате чего первый ключ 8 замыкается а второй ключ 9 размыкается и на

выходе генератора 3 линей ого напряжения под действием положительного напряжения с выхода стабилизатора 7 амплитуды опорных импульсов появляетс линейно спадающее напряжение (фиг,26

В момент времени 1(фиг,2) линейно спадающее напряжение сравнивается с отрицательным уровнем входного напряжения, при этом опрокидывается первая схема 4 сравнения (фйг,2в), в результате чего первый элемент И 1 вырабатывает нулевой потенциал, размыкающий зарядный ключ 12,

В момент времени t напряжение на выходе интегратора 2 достигает уровня, при котором вторая cxef-a 5 сравнения опрокидывается (фиг,2а), преобразователь возвращается в исходное состояние (рассмотренное- для момента t --i) ; таким образом заканчивается полный период Т колебаний преобразователя. Далее в преобразователе происходят автоколебательные процессы, аналогичные описанным выше.

Период колебаний на выходе 26 антилогарифмического преобразователя равен

Т-4Г )4tr/ra)

(1)

Де Sj - постоянная времени интегратора 2 ; и - значение напряжения на вход

.25;

Up - значение опорного напряжения с инверсного выхода блока 7J

Jr. - постоянная времени генератора 3 линейного напряжения; Щ - постоянная времени формирователей 16 и 17 экспоненциального напряжения. Амплитуда импульсов с выхода дифференциального усилителя 18 равна

(ивх/ио)-(Гг/Гд)

и.

(2)

Технико-экономическим преимуществом предлагаемого изобретения перед известными преобразователями является повышение точности благодаря практически полной компенсации погрешности (обусловленной смещением порогов срабатывания схем сравнения) так как в нем в течение периода колебаний сравнение напряжений на всех схемах сравнения происходит при подходе линейно изменяющего напряжения снизу и сверху. При этом погрешности Ксисдого из полупериодов имеют при абсолютном раивенстве значений противоположные знаки и при сложении взаимно уничтожаются. Таким образом, период колебаний не зависит от дрейфа напряжения смещения.

Формула изобретения

Антилогарифмический преобразователь, содержащий стабилизатор амплитуды опорных импульсов, генератор линейного напряжения, дифференциальный усилитель, первый формирователь экспотенциального напряжения, первую и вторую схекы сравнения, первый элемент И, зарядный и разрядный ключи, первый, второй, третий и четвертый ключи, гаыход зарядного ключа соединен со входом первого формирователя экспоненциального напряжения, выход которого подключен к входу разрядного ключа, выход генератора линейного напряжения присоединен к первому входу первой схемы сравнения, прямой которой соединен с первым входом первого элемента И/ выход которого подключен к управляющему входу зарядного ключа, выход второй схемы сравнения присоединен к входу стабилизатора амплитуды опорных импульсов, о т л и ч а ющ и и с я тем, что, с целью повышения точности работы, в него введены амплитудный модулятор, интегратор, инвертор, элемент ИЛИ, второй, третий и четвертый элементы И, второй формирователь экспоненциального нап ряжения и дополнительные зарядный и раэрядный ключи, третья схема сравнения, выход амплитудного модулятора соединен с вторым входом первой схемы сравнения, инверсный выход которой подключен к первому входу второго элемента И, выход которого присоединен к управляющему входу дополнительного зарядного ключа, выход которого подключен к входу второго формирователя экспоненциаль ного напряжения, выход стабилизатор амплитуды опорных импульсов соедине с первыми входами амплитудного модулятора, второй схемы сравнения, третьего элемента И, с входом перво го ключа, с управляющим входом четвертого ключа и инвертирующим входо дифференциального усилителя, выход которого подключен к входу интегратора, первый вход третьей сх&ла сра нения присоединен к шине нулевого потенциала, выход интегратора соеди нен с вторыми входами второй и трет ей схем сравнения, выход первого ключа присоединен к входам второго ключа и генератора линейного напряж ния, к выходу которого подключен выход второго ключа, выход третьей схемы сравнения соединен с вторыми входами первого и третьего элементо И, инверсный выход стабилизатора амплитуды опорных импульсов подключен к второму входу амплитудного мо лятора, к первому входу четвертого элемента И, к входам зарядного ключ и дополнительного зарядного ключа и к управляющему входу третьего ключа, выход второго формирователя экспотенциального напряжения соединены с входами третьего ключа и дополнительного разрядного ключа,выход которого присоединен к выходу разрядного ключа и к шине нулезого потенциала, инверсный выход третьей схемы сравнения соединен с вторыми .входами второго и четвертого элементов И, выход третьего элемента И подключен к управляющему входу дополнительного разрядного ключа и к первому входу элемента ИЛИ, второй вход которого присоединен к .выходу четвертого элемента Ник управляющему входу разрядного ключа, выход элемента ИЛИ соединен с входом инвертора и управлжощим входом первого ключа, выход инвертора подключен к управляющему входу второго ключа, третий вход амплитудного модулятора является входом антилогарифмического преобразователя, выходы третьего и четвертого ключей присоединены к неинвертирующему входу дифференциального усилителя, вход четвертого ключа соединен с выходом первого формирователя экспоненциешьного напряжения, выход стабилизатора амплитуды опорных импульсов является выходом антилогарифмического преобразователя.. Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР .304575, кл. G 06 G 7/24, 1970. 2. Авторское свидетельство СССР 444207, кл, G 06 G 7/24, 1972 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-12-12—Подача