(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное устройство | 1982 |

|

SU1040607A1 |

| Счетное устройство | 1985 |

|

SU1256195A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Устройство для вычисления модуля вектора полярных координат | 1989 |

|

SU1725217A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1015443A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство для сортировки чисел | 1990 |

|

SU1737441A1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

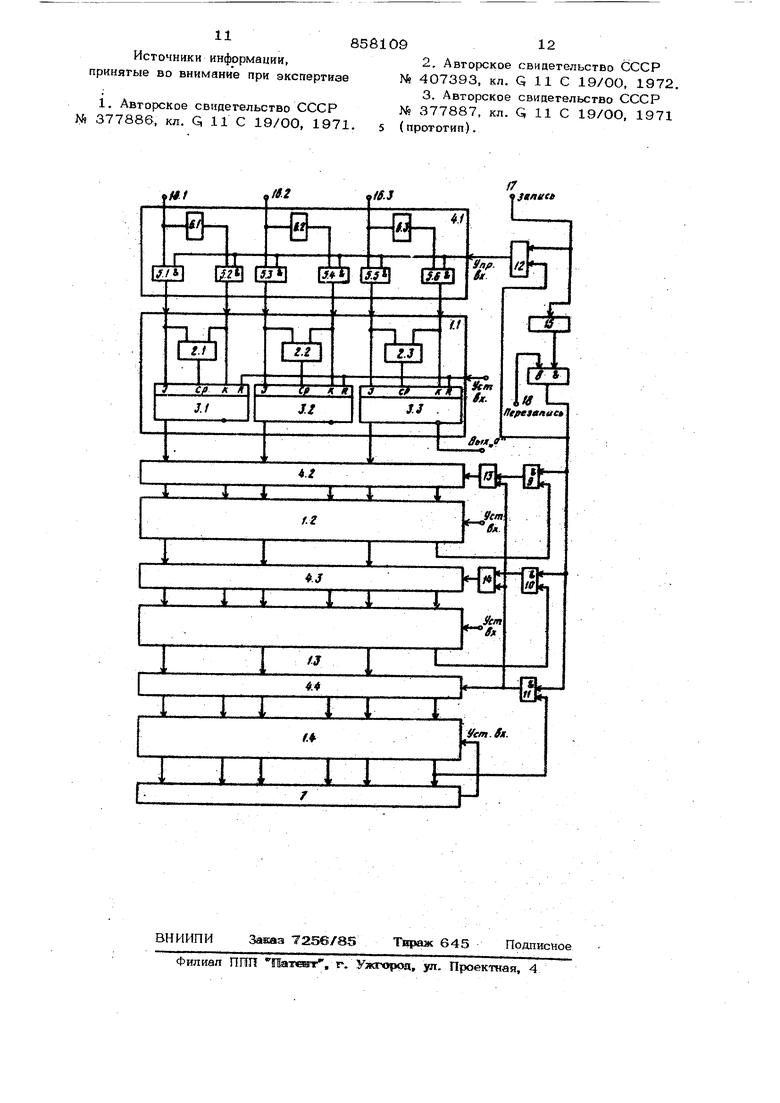

Изобретение относигс я к области вычислительной технике, а именно к запоми нающим устройствам электронных вычислительных машин и может быть использовано при построении буферных устройст хранения информации в системах дискрет ной техники. Известно запоминающее устройство, содержащее поразрядно соединенные регистры, схемы управления перезаписью по числу регистров, коммутатор, переклю чатель, элемент ИЛИ 11. Недостатком этого устройства является сложная схема при сравнительно Малом объеме памяти, что усложняет аппаратурную реализацию устройства. Известно также буферное запоминающее устройство, содержащее регистры хр нения чисел, элементы И, управляющий двухтактный регистр сдвига, в каждом разряде которого основной и вспомогател ный триггеры соединены через элементы И Г21. Недостатком этого устройства является сложная скема управления перезаписью, требующая наличие многотактной системы управления перезаписью. Наиболее близким по технической сущности к предлагаемому устройству является запоминающее устройстве, содержащее регистры, выполненные йа элементах ИЛИ и JK -триггерах, Р - входы которых в каждом регистре соединены между собой и подключены к установочному входу регистра, а информационные входы J и К соединены с выходами элементов И соответствующих: узлов записи, выполненных на элементах И и НЕ, единичные выходы JK -триггеров каждого регистра, кроме последнего, соединены с информационными входами соответствующего узла записи, а выходы последнего регистра подключены ко входам приемно-регистрирующего блока Гз. Недостатком данного устройства является то, что оно не обеспечивает непрерывного режима передачи информации с ройства на медленнодействующее приемно-регистрирующее устройство, что существенно снижает быстродействие канала обмена между вычислительным устройством и приемно-регистрирующим устройством. Цель изобретения - расширение области применения устройства аа счет обеспечения непрерЬшного режима приема и выцачи информации, например, с быстродействующего вычислительного устройства на медленнодействующее приемно-регистрирующее устройство. Указанная цель достигается тем, что в буферное запоминающее устройство, содержащее блоки записи, выходы которых соединены с информационными входами ре гистров, информационные выходы каждого из регистров, кроме последнего, соединены с информационными входами каждого из последующих блоков записи, шины записи и перезаписи, информационные входы первого блока записи являются входами устройства, а выходы последнего регистра являются выходами устройства, ввеце- ны элементы И, ИЛИ и НЕ. При этом вход элемента НЕ подключен к шине записи и к первому входу первого элемен- та ИЛИ, выход которого соединен с управ ляющим входом первого блока записи. Вы- ход элемента НЕ подключен к первому входу первого элемента И, второй вход которого подключен к шине перезаписи, а выхоц соединен со вторым входом первого элемента ИЛИ, с первыми входами ВТОрых элементов И и с первым входом Vpeтьего элемента И, второй вход которого подкл,ючен к маркерному выходу последнего регистра, а выход соединен с управляющим входом последнего блока записи и со вторыми входами вторых элементов ИЛИ, первые входы которых подключены к выходам соответствующих вторых элементов И, а выходы - к управляющим входам соответствующих блоков записи. Вторые вхоаы вторых элементов И соединены с маркерными выходами соответствующих регистров. Каждый регистр предлагаемого устройства содержит Tk -триггеры и элемен ты ИЛИ, причем входы элементов ИЛИ соединены с информационными входами ре гистра, Т -входами и К -входами JK триггеров соответственно, а выходы со - строби| ующими Ср -входами Jk -триггеров, единичные выходы которых являются информационными выходами регистра. ра является маркерным выходом регистра. R -входы всех Jk -триггеров подключены к установочному входу регистра. Каждый блок записи предлагаемого устройства содержит элемент И и НЕ, причем входы элементов НЕ соединены с информационными входами блока записи и первыми входами соответствующих первых элементов И, а выходы - с первыми входами соответствующих вторых элементов И. Вторые входы элементов И подключены к управляющему входу блока записи. Выходы элементов И подключены к соответствующим выходам блока. На чертеже представлена блочная схема предлагаемого устройства, содержащего, например, четыре регистра, обеспечивающих прием, хранение и передачу трехразрядных чисел. Буферное запоминающее устройство содержит регистры 1.1-1.4, выполненные на элементах ИЛИ 2.1-2.3 и JK -триггерах 3.1-3.3, блоки 4.1-4.4 записи, выполненные на элементах И 5.1-5.6 и НЕ 6.1-6.3, приемно-регистрирующий блок 7, дополнительные элементы И 8- 11, ИЛИ 12-14, НЕ 15, информационные входы 16.1-16.3, шину 17 записи. шину 18 перезаписи, R -входы Тk -триггеров 3.1-3.3 в каждом регистре 1.11.4 соединены между собой и подключены к установочному входу регистра 1.1-1.4, информационные входы 3 и К соединены с выходами элементов И 5.1-5.6 соответствующих блоков 4.1-4.4 записи, еди- i ничные выходы JK -триггеров 3.1-3.3 каждого регистра, кроме последнего 1.4 соединены с информационными входами соответствующего блока 4.1-4.4 записи. а выходы последнего регисгра 1.4 подключены ко входам приемно-регистрирующего блока 7,в кажяом блоке 4.1-4.4 записи выход каждого элемента НЕ 6.1- 6.3 соединен с первым входом четного элемента И 5.2, 5.4 и 5.6, вход каждого элемента НЕ 6.1-6.3 подключен к первому входу нечетного элемента И 5.1, 5.3 и 5.5, а вторые входы элементов И 5.1-5.6 соединены с управляющим входом блока 4.1-4.4 записи, в каждом регистре 1.1-1.4 входы каждого элемента ИЛИ 2.1-2.3 соединены соответственно с информационными входами О и К каждого СГК -триггера 3.1-3.3, а выход каждого элемента ИЛИ 2.1-Р.З подключен к стробирующему входу Ср каждого J к триггера 3.1-3.3, первый вход пе|.)Во1о

дополнительного элемента ИЛИ 12 подключен к шине 17 записи, а выход соединен с управляющим входом первого блока 4.1 записи, шииа 18 перезаписи подключена к первому входу первого дополнигел кого элемента И 8, второй вход которого через элемент НЕ 15 подключен к шине 17 записи, выход первого дополнительно- го элемента И 8 соединен с первыми входами вторых дополнительных элеменгов И 9 и 10, третьего элемента И 11 и вторым входом первого дополнительного элемента ИЛИ 12, вторые входы вторых дополнительных элементов И 9 и 1О соединены с нулевыми выходами последних JK -триггеров 3.3 второго третьего регистров 1.2 и 1.3 соответственно, а . выход вторых дополни тел элементов И 9 и 1О подключены к первым входам вторых дополнительных элементов ИЛИ 13 и 14 соответственно. Нулевой выход последнего JK -триггера последнего регистра 1.4 соединен со вторым входом третьего дополнительного элемента И 11 выход которого подключен ко вторым вхо дам вторых дополнительных элементов ИЛИ 13 и 14, а также к управляющему входу четвертого блока 4.4 записи. Выход вторых дополнительных элементов ИЛИ 13 и 14 соединены с управ/гякзэдимн входами второго блока 4.2 и третьего блока 4.3 записи соответственно. Управляющий выход приемно-регистрирующего блока 7 подключен к установочному вкоду последнего регистра 4.4.

Перед началом работы устройства схема приводится в исходное состоание, в результате че го Т К -триггеры 3.1-3.3 всех регистров 1.1-1.4 будут находиться в нулевом состоянии.

После этого схема готова к работе.

Для обеспечения непрерьтного режима передачи информации с быстродействующего вычислительного устройства на медленнодействующее приемно-регистрирующее устройство количество приемных регистров в данном буферном запоминающем устройстве определяется из соотношения

(v.,-Va),

где п - общее количество регистров, необходимых цля обеспечения непрерывного режима передачи информации;

Т - время передачи информации из вычислительного устройства;

V- - скорость передачи информации из вычислительного устройства.

т.е. количество слов, передаваемых в единицу времени; Vn - скорость приема информации приемно-регистрирующим блоком, т.е. количество слов, принимаемых в единицу времени; СьП - количество регистров, необходимых для компенсации времени, затраченной на перезапись информации с первого приемного регистра в последний, которое составляет 5-1О% от общего Количества регистров.

Устройство работает следующим образом.

На входы 16.1-16.3 поступает первое 3-разрядное число, которое затем поступает на первые входы нечетных элементов И 5.1, 5.3 и 5.5 первого блока 4.1 записи в прямся коде и четных элементов И 3.2, 3.4 и 3.6 в обратном коде. Поступающее информационное слово сопровождается сигналом записи, поступающим по шине 17 записи, который поступает на один из входов первого дополнительного элемента ИЛИ 12. Первый До полнительный элемент ИЛИ 12 срабатывает и выдает сигнал записи на управляющий вход первого блока 4.1 записи, по которому, в зависимости от кода поступающего многоразрядного числа, открываются определенные элементы И 5.1-5.6 первого блока 4.1 записи, и информация поступает на информацисжные входы J и К и через апеманты ИЛИ 2.1-2.3 на стробирующие входы каждого JK -триггера аервого регистра 1.1. По заднему фронту сигнала записи первое информационное слово позволяет на единичных выходах JK -триг-геров 3.1-3.3 первого регистра 1.1.

Сигнал записи, поступающей по шине 17 записи, через дополнительный элемент НЕ 15 запрещает работу вторых и третьего дополнительных элементов И 9-11, предотвращая запись ложной информации во все остальные регистры 1.2-1.4.

Каждое информационное слово, поступающее в устройство, сопровождается наличием признака, соответствующего единице в последнем разряде, так как передаваемое информационное слово может содержать и нулевую информацию, поэтому в каждом регистре последний JK -триггер 3.3 предНасзначен для формирования признака, принятого информационного слова. В результате чего, после приема первого информационного слова послецний-ТК 7fiS триггер 3.3 первого регистра 1.1 будет находиться в единичном состоянии. На этом заканчивается процесс записи перового информационного слова в первый ре гистр 1.1. Далее начинается процесс перезаписи принятого информационного слова из первого регистра 1.1 в последний регистр 1.4. Для этого по шине 18 перезаписи поступает сигнал перезаписи, совпадающий по фазе с сигналом записи, но с частотой следования на порядок выше, чем сигнал записи. Сигнал перезаписи поступает на первый вход первого дополнительного элемента И 8, на второй вход кого porD с элемента НЕ 15 поступает запрещающий сигнал записи, предотвращаю- шнй прохождение сигнала перезаписи в момент приема очередного информационно го слова. С выхода первого дополнитель- кого элемента И 8 сигнал перезаписи поступает на первые входы вторых и третьего допапнительных элементов И 9-11, которые подготовлены к работе сигналами поступающими с нулевых выходов послед- нихТК -триггеров 3.3 соответствующих регисгров. Сигналь( с выходов вторых дополнител ных элементов И 9 и 1О поступают на первые входы вторых дополнительных зле ментов ИЛИ 13 и 14 и далее на управляющие входы соответствующих блоков 4.2 и 4.3 записи, а сигнал с выхода тре тьего дополнительного элемента И 11 по ступает на вторые входы вторых дополни- тельных элементов ИЛИ 13 и 14 и на управляющий вход последнего блока 4.4 записи. Сигнал перезаписи с выхода первого йополнительного элемента И 8 через пбервый дополнительный элемент ИЛИ 12 поступает на управлшощий вход первого блока 4.1 записи. По сигналам, поступающим на управляющае входы блоков 4.14,4 записи, открываются элементы И 5.1-5.6 соответствующих блоков записи и первое информационное слово, находящееся в первом регистре 1.1 поступает на информационные входы Т и К через элементы ИЛИ 2.1-2.3 на стробирующие входы каждого Jk. -триггера второго регистра 1,2. По заднему фронту сигнала перезаписи первое информационное слово переписывается во второй приемный регистр 1.2, а в остальных регистрах 1.3 И 1.4 по заднему фронту сигнала переааписи происходит подтверждение нулевой информации, так как в третий регистр 1.3 переписывается по заднему фронту 0в игнала перезаписи нулевая информация, аходящаяся во втором-регистре 1.2, а четвертый регистр 1.4 -- нулевая инфорация, находящаяся в г-ретьем регистре 1.3. Первый регистр 1.1 по заднему фрону сигнала перезаписи обнуляется, так ак на информационных входах 16.1-16.3 данный момент отсутствует входная инормация. По приходу второго сигнала ерезаписи первое информационное слово ерезаписывается в третий оегистр 1.3 о описанному способу. По третьему сигналу перезаписи первое информационное слово переписывается в четвертый регистр 14. Сигнал поступающий с нулевого выхода последнего Л k -триггера последнего регистра 1.4 запрещает работу третьего дополнительного элемента И, предотвращая искажение принятого информационного слова. По этому сигналу приемно-регистрирующий блок 7 осуществляет прием информационного слова, находящегося в последнем регистре 1.4. При поступлении второго информационного слова на информационные входы 17.1-16.3, сопровождаемого сигналом записи по шине 17 записи, запрещается поступление сигнала перезаписи и осуществляется запись второго информационного слова в первый регистр 1.1 по описанному способу. После окончания запяси второго информационного слова в первый регистр 1.1 начинается процесс перезаписи принятого информационного слова в последующие регистры 1.2-1.4. Информационное слово будет переписываться в свободные регистры до первого занятого регистра по ранее описанному способу. Таким образом, оно будет записано в последнем свободном регистре. Прием последующих информационных слов и перезапись их в свободные регистры аналогичен описанному способу. Приемно-регистрирующий блок 7 по сигналу, поступающему с нулевого выхода последнего JK -триггера последнего регистра 1.4, начинает обрабатывать поступившее в последний регистр 1.4 информационное слово, к после его регистрации приемно-регистрирующий блок 7 по управляющему выдает сигнал на установочный вход последнего регистра, который 1 оступает в паузе между сигналами перезаписи и обнуляет последний регистр 1.4. В результате чего, с нулевого выхода посл- днего ТК. -триггера последногп регистра 1.4 поступает разрешающий сиг нал на грегий дополнительный элемент И 11, и очередной сигнал перезаписи с выхода третьего дополнительного элемента И 11 через вторые допопнигельные элементы ИЛИ 13 и 14 осуществляет перезапись всего массива информационных сло находящихся в устройстве, на один шаг, т.е. каждое информационное слово хранимого массива информации, находящееся в соответствующем i -ом регистре, где i 1, 2, 3 ... (« -1), перезаписывается одновременно со всеми другими информационными словами данного массива информации в соответствующий i +1 ре- гистр, расположенный ниже данного регистра, в котором хранилось информацион ное слово. Таким образом, на входах приемно-регистрирующего блока 7 появляется очеред нов информационное слюо, которое затем обрабатывается приемно-регистрируюшим блоком 7 по описанному способу. Далее запись, перезапись и обртботка поступающих инфо{Я4ационных слеш осу- ществляется по описанному способу. Данное устройство может быть построено на любое рассчитанное количество регистров с требуемым количеством дое в каждом регистре. Использование данного устройсгва обес печивает по сравнению с известными следующие преимущества: расширяется применения устройства, так как обеспечи-вается непрерывный режим передачи ин- фо{Яи1ации. с быстродействующего вычисли тельного устройства на медленнодействую щее приемно-регистрирующее устройство, это позволяет передавать информацию по каналу обмена со скоростью ее t paботки в быстродействующем вычислительном устройстве, что существенно псдаышает эффективность работы вычислительного устройства, так как исключаются задержки в работе вычислительного устройства, связанные с обработкой информации медленнодействующим приемно-регистрирующим устройством. Формула изобретения 1. Буферное запоминающее устройство содержащее блоки записи, выходы которых соединены с информационными входами регистров, информационные выходы каждого из регистров, кроме последнего, соединены с информационными входами каждого- из псюледующих олоков записи, шины записи и перезаписи, ин||юрмаиион- ные входы первого блока записи являются входами устройства, выходы последнего регистра являются выходами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения непрерывного режима приема п выдачи информации, в него введены элементы И, ИЛИ, НЕ, причем вход элемента НЕ подключен к шнне записи и к первому входу первого элемента ИЛИ, выход которого соединен с управляющим входом первого блока записи, выход элемента НЕ подключен к первому входу первого элемента И, второй вход которого псдаключен к шине перезаписи, а выход соединен со вторым входом первого элемента ИЛИ, с первыми входами вторых элементов И и с первым входом третьего элемента И, второй вход которого подключен к маркерному выходу последнего регистра, а выход соединен с управляющим входом последнего блока записи н со вторыми входами вторых элементов ИЛИ, первые входы которых подключены к выходам соответствующих вторых элементов И, а выходы - к управляющим входам соответствующих блоков записи, вторые входы вторых элементе И соединены с маркерными выходами соответствующих регистров, 2.Устройство по п. 1,отличающее с я тем, что каждый регистр содержит J k -триггеры и элементы ИЛИ, причем входы элементов ИЛИ соединены с информационными входами регистра, J -входами и К -входами JK -триггеров соответственно, а выходы - со стро- бирующими Ср -выходами J К -триггеров, единичные выходы которых являются информационными выходами рбгистра, а нулевой выход последнего . -триггера является маркерным выходом регистра, R-входы всех JK -триггеров подключены к установочному входу регистра. 3.Устройство по п. 1, отличающееся тем, что каждый блок записи содержит элементы И и НЕ, причем входы элементов НЕ соединены с информацион 1ыми входами блока записи и первыми входами соответствующих первых элементов И, а выходы - с первыми входами соответствующих вторых элементов И, вторые входы элементов И подключены к управляющему входу блока записи, а выходы элементов И подключены к соответствующим выходам блока.

85810912

Источники информации,2. Авторское свидетельство СССР

принятые во внимание при экспертизеN 407393, кл. Q 11 С 19/ОО, 1972.

1, Авторское свидетельство СССР№ 377887, кл. Q 11 С 19/ОО 1971

№ 377886, кл. Q 11 С 19/00, 1971. s (прототип).

Авторы

Даты

1981-08-23—Публикация

1980-01-10—Подача