Предлагаемые объекты изобретения объединены единым изобретательским замыслом, относятся к радиотехнике, а именно к автоматике и технической диагностике параметров сигналов, и могут быть использованы при построении распознающих автоматов для комплексов технического анализа и распознавания классов сигналов.

Известен способ распознавания классов сигналов [см. А. С. СССР N 1304045 A2, G 06 K 9/00, 15.04.87]. Данный способ предусматривает одновременный прием сигнала на m демодулирующих устройств (где m=1, 2, 3,... - количество различных классов сигналов, которые можно распознать). Путем последующего анализа ширины спектров, а также гармонических составляющих входного сигнала на выходах демодуляторов и умножителей частоты обнаруживается, к какому из m классов принадлежит сигнал или делается вывод, что принимаемый сигнал не принадлежит ни к одному из возможных классов.

Однако указанный аналог имеет недостатки. Например, его реализация приводит к излишней громоздкости устройства, его реализующего, т.к. на каждый возможный класс сигнала необходим индивидуальный канал распознавания. Узка область применения, т.к. не позволяет распознавать сигналы, применяющие сигнально-кодовые конструкции (СКК) с решетчатым кодированием.

Наиболее близким по своей технической сущности по отношению к заявленному способу является способ корреляционного сравнения Q реализаций сигнала, реализованный в известном устройстве [см. А.с. СССР N 1667117, A2, кл. G 06 K 9/00, 10.05.89] . Данный способ относится к числу синхронных способов и предусматривает потактную работу с частотой 1/T, где T - длительность такта работы сети. Способ-прототип заключается в следующем: принимают Q реализаций сигнала, клиппируют их, коммутируют все Q реализаций попарно, каждая с каждой, и подсчитывают коэффициенты корреляции в каждой паре, умножают коэффициент корреляции каждой пары на весовой коэффициент данной пары, хранящийся в базе данных и соответствующий определенному классу сигналов, складывают полученные произведения, а результат сравнивают с пороговым значением и идентифицируют класс сигнала. При таком способе обеспечивается распознавание более широкого класса сигналов за счет хранения индивидуальных признаков большого числа классов сигналов в базе данных и возможности функционирования способа в режиме обучения.

Однако способ-прототип имеет недостатки:

- узкая область применения, т.к. данный способ предназначен для распознавания N-мерных сигналов, как правило, давно и широко используемых, с хорошими корреляционными свойствами. Однако он не приспособлен к распознаванию сигналов, реализующих технологию СКК с решетчатым кодированием;

- устройство, реализуемое по данному способу, отличается громоздкостью и сложностью, особенно при повышении точности распознавания, т.к. даже незначительное увеличение объема выборки реализаций приводит к существенному возрастанию количества необходимых элементов устройства.

Известны устройства для распознавания различных классов сигналов. Так, устройство для распознавания классов сигналов [см. А.с. СССР N 1317463 A2, кл. G 06 K 9/00, 26.03.85] содержит первый и второй умножители частоты, первый, второй и третий анализаторы мгновенного спектра, первый и второй блоки сравнения, первый и второй компараторы, элемент И, первый и второй фазовые детекторы, генератор опорного напряжения, инвертор; входы первого анализатора мгновенного спектра, умножителя на восемь, умножителя на четыре, первого фазового детектора и генератора опорного напряжения включены в параллель и являются сигнальным входом устройства, а выход генератора опорного напряжения подключен ко второму входу фазового детектора, выход первого анализатора мгновенного спектра подключен к первым входам первого и второго блоков сравнения сигналов, вход инвертора подключен к выходу второго компаратора, вторые входы первого и второго блоков сравнения подключены соответственно к выходам второго и третьего анализаторов мгновенного спектра, выходы умножителя на восемь и умножителя на четыре подключены соответственно ко входам второго и третьего анализаторов мгновенного спектра, а выходы первого и второго блоков сравнения сигналов подключены соответственно к первым входам первого и второго компараторов, вторые входы которых являются входами первого и второго пороговых напряжений, выход первого компаратора подключен к первому входу элемента И, ко второму входу которого подключен выход инвертора.

Однако известное устройство имеет недостатки:

- узкую область применения;

- неприемлемо для распознавания сигналов СКК с решетчатым кодированием;

- имеет относительно сложную конструкцию.

Наиболее близким по своей технической сущности является устройство, описанное в [А.с. СССР N 1667117 A2, кл. G 06 K 9/00, 10.05.89].

Устройство прототип состоит из пороговых элементов 1-1,..., 1-N, первого ключа, первого счетчика, генератора тактовых импульсов, второго ключа, N элементов И, второго счетчика, первого элемента задержки, элемента ИЛИ, второго элемента задержки, блока памяти, перемножителя, накапливающего сумматора, блока принятия решения, мультиплексора, M счетчиков, M элементов совпадения (где M=N(N-1)/2), информационные входы мультиплексора подключены к информационным выходам соответствующих счетчиков группы, а его выход соединен с первым входом перемножителя, второй вход и выход которого соединены соответственно с выходом блока памяти и информационным входом накапливающего сумматора, вход блока принятия решения соединен с выходом накапливающего сумматора, а выход блока принятия решения является информационным выходом устройства, выход генератора тактовых импульсов подключен к первым входам первого и второго ключей, вторые входы которых соединены с выходом переполнения первого счетчика, выход первого ключа соединен с информационным входом второго счетчика, выход переполнения которого подключен к входу первого элемента задержки, выход которого подключен к третьим входам первого и второго ключей и входам сброса первого и второго счетчиков, накапливающего сумматора и счетчиков групп, информационные входы которых соединены с выходами соответствующих элементов совпадения группы, информационный выход второго счетчика подключен ко входу управления мультиплексора, адресному входу управления блока памяти и входу элемента ИЛИ, выход которого подключен ко входу второго элемента задержки, выход которого соединен со входом синхронизации накапливающего сумматора, выход второго ключа подключен к информационному входу первого счетчика и к первым входам элементов И группы, вторые входы которых соединены с выходами соответствующих пороговых элементов группы, входы которых являются информационными входами устройства, при этом первый и второй входы каждого элемента совпадения группы подключены соответственно к выходам соответствующих i-го и j-го элементов И группы, где i=1,.. . N-1; j=2...N; i<j.

Однако устройство прототип имеет недостатки:

- узкая область применения, т.к. данное устройство предназначено для распознавания N-мерных сигналов, как правило, давно и широко используемых, с хорошими корреляционными свойствами. Однако оно не приспособлено к распознаванию сигналов, реализующих технологию СКК с решетчатым кодированием;

- реализуемое устройство отличается громоздкостью и сложностью, особенно при повышении точности распознавания, т.к. даже незначительное увеличение объема выборки реализаций приводит к существенному возрастанию количества необходимых элементов устройства.

Целью заявленных объектов изобретения является разработка способа и устройства распознавания классов сигналов, обеспечивающих возможность распознавания СКК с решетчатым кодированием и одновременно не усложняющих конструкцию устройства, его реализующего.

Поставленная цель достигается тем, что в известном способе, заключающемся в приеме Q реализаций сигнала, по Y разрядов в каждой реализации сигнала, их обработке и на основе обработки идентификации класса принятого сигнала. После приема Q реализаций сигнала, их запоминают, а для обработки реализаций сигнала их группируют по K реализаций в группе, где Kmin<K<Kmax. Сравнивают попарно группы реализаций. Выделяют пары групп реализаций, отличающиеся друг от друга лишь одной реализацией. Сравнивают младшие разряды отличающихся друг от друга реализаций в каждой выделенной паре групп реализаций. Вычисляют общее число несовпадений младших разрядов в сравниваемых реализациях. Сравнивают общее число несовпадений S с заданным пороговым значением Sп. И при выполнении условия S<Sп сигнал идентифицируют, как имеющий сигнально-кодовую конструкцию с решетчатым кодированием.

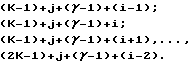

При группировании Q реализаций сигнала, последовательно числу K реализаций, включаемых в группу реализаций, присваивают значения начиная, с K= Kmax-(j-1) до K=Kmin, где j=1, 2, 3,...,(Kmax-Kmin+1), а номеру γ реализации, начиная с которого группируют соответствующую группу реализаций, присваивают последовательно значения γ = 1, 2, 3,..., Q-(2K-1), после чего для каждой пары значений K и γ в первую группу включают реализации с номерами:

j+( γ -1); j+1+( γ -1);...,(K-1)+j+( γ -1);

во вторую - K+j+( γ -1); (K+1)+j+( γ -1); (K+2)+j+( γ -1),..., (2K-1)+j+( γ -1);

а в i-e группы, где i=3,4,5,..., Q-2(K-1), включают реализации с номерами:

(K-1)+j+( γ -1)+(i-1); (K - 1)+j+(γ-1)+i; (K-1)+j+( γ -1)+(i+1),..., (2K-1)+j+( γ -1)+(i-2);

Общее число Q принимаемых реализаций сигнала выбирают из условия Q>100, а значения Kmin и Kmax выбирают в пределах Kmin=2...3, Kmax=4,...100, а пороговое значение числа несовпадений Sп выбирают в зависимости от качества канала связи в пределах Sп= 10...1000.

Указанная выше совокупность существенных признаков, благодаря статистической обработке реализаций сигнала и на ее основе выделении индивидуальных распознающих признаков класса сигнала, позволяет распознавать сигналы СКК с решетчатым кодированием и определять длину памяти помехоустойчивого решетчатого кодера.

Поставленная цель в заявленном устройстве достигается тем, что в известное устройство распознавания классов сигналов, содержащее блок памяти и блок принятия решения, первый информационный выход которого является первым информационным выходом устройства, дополнительно введены блок формирования адресов и блок определения запрещенных событий. Синхронизирующий вход блока формирования адресов является синхронизирующим входом устройства. Два N-адресных выхода блока формирования адресов подключены соответственно к двум N-адресным входам блока памяти. Выход управления режимом блока формирования адресов подключен ко входу выбора режима блока памяти. Выход конец окна блока формирования адресов подключен к решающему входу блока определения запрещенных событий. Сигнализирующий выход блока формирования адресов подключен к блокирующему входу блока принятия решения. Установочный вход блока формирования адресов подключен к выходу стоп - анализ блока принятия решения. N-разрядный вход размер окна блока формирования адресов подключен соответственно к N-разрядному выходу размер окна блока принятия решения. Синхронизирующий выход блока формирования адресов подключен к синхронизирующему входу блока памяти. Режимный вход блока формирования адресов подключен к режимному выходу блока принятия решения. Первые и вторые Y-разрядные выходы данных блока памяти подключены соответственно к первым и вторым Y-разрядным входам данных блока определения запрещенных событий. Y информационных входов блока памяти являются Y информационными входами устройства. Решающий выход блока определения запрещенных событий подключен к счетному входу блока принятия решения. А второй N-разрядный информационный выход блока принятия решения является соответственно вторым N-разрядным информационным выходом устройства.

Блок формирования адресов состоит из первого и второго двоичных N-разрядных счетчиков, двоичного N-разрядного счетчика с предустановкой, первого, второго, третьего, четвертого и пятого элементов 2И, первого, второго, третьего, четвертого и пятого элементов 2ИЛИ, JK-триггера, элемента ИЛИ-НЕ, первого и второго N-разрядных сумматоров. Синхронизирующий вход блока формирования адресов подключен соответственно к синхронизирующему выходу блока формирования адресов, тактовому входу JK- триггера, второму входу третьего элемента 2И, второму входу пятого элемента 2И. Установочный вход блока формирования адресов подключен ко второму входу четвертого элемента 2ИЛИ, выход которого подключен к сигнализирующему выходу блока формирования адресов и установочным входам второго двоичного N-разрядного счетчика, двоичного N-разрядного счетчика с предустановкой и первому входу пятого элемента 2ИЛИ, выход которого подключен к установочному входу первого двоичного N-разрядного счетчика. Режимный вход блока формирования адресов подключен ко второму входу третьего элемента 2ИЛИ. Выход третьего элемента 2ИЛИ подключен к первому и второму информационным входам JK-триггера, выход которого подключен ко входу элемента ИЛИ-НЕ, выходу управления режимом блока формирования адресов, первому входу второго элемента 2И, первому входу третьего элемента 2И, второму входу четвертого элемента 2И. Инверсный выход элемента ИЛИ-НЕ подключен к первому входу первого элемента 2И и первому входу пятого элемента 2И. Выход первого элемента 2И подключен к первому входу первого элемента 2ИЛИ, второй вход которого подключен к выходу второго элемента 2И, а выход к счетному входу первого двоичного N-разрядного счетчика. Выход третьего элемента 2И подключен к счетному входу двоичного N-разрядного счетчика с предустановкой, выход переполнения которого подключен ко второму входу второго элемента 2И и является выходом конец окна блока формирования адресов. N-разрядный информационный вход двоичного N-разрядного счетчика с предустановкой является N-разрядным входом размер окна блока формирования адресов. Выход четвертого элемента 2И подключен ко второму входу пятого элемента 2ИЛИ и первому входу второго элемента 2ИЛИ, второй вход которого подключен к выходу пятого элемента 2И, а выход к счетному входу второго двоичного N-разрядного счетчика. N-разрядный выход которого подключен ко второму N-разрядному информационному входу второго сумматора. Выход переполнения второго сумматора подключен к первому входу четвертого элемента 2ИЛИ и первому входу третьего элемента 2ИЛИ. N-разрядный выход счетчика с предустановкой подключен соответственно ко второму N-разрядному информационному входу первого сумматора и первому N-разрядному информационному входу второго сумматора. N-разрядный выход первого счетчика подключен к первому N-разрядному информационному входу первого сумматора, N-разрядный выход которого является первым N-адресным выходом блока формирования адресов, а выход переполнения подключен к первому входу четвертого элемента 2И. N-разрядный выход второго сумматора является вторым N-адресным выходом блока формирования адресов.

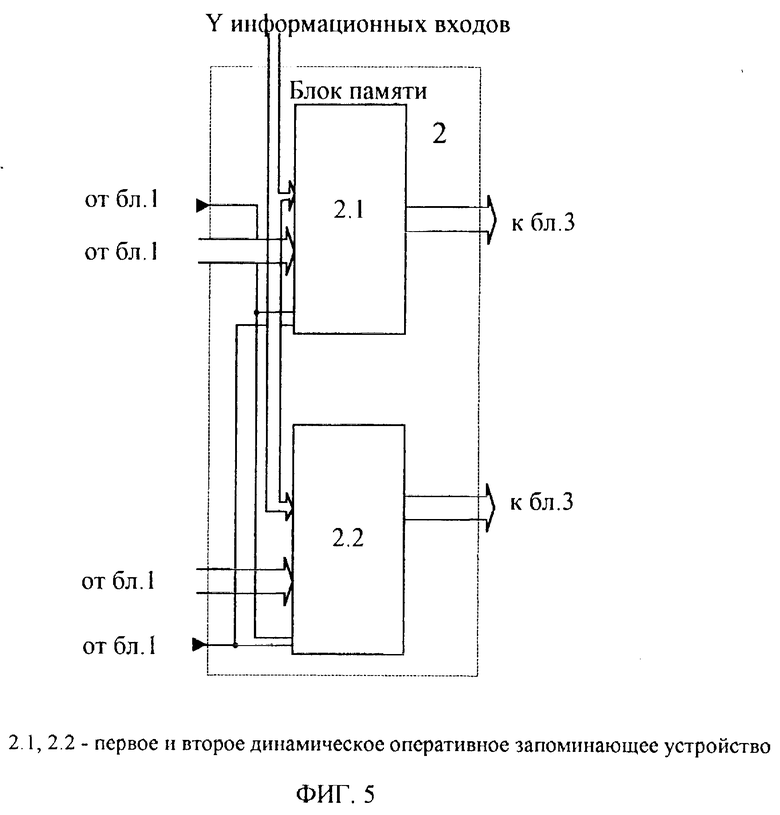

Блок памяти состоит из первого и второго динамических оперативных запоминающих устройств. Y информационных входа первого и второго динамических оперативных запоминающих устройств являются соответственно Y информационными входами блока памяти. N-разрядные адресные входы первого и второго ОЗУ являются соответственно первыми и вторыми N-адресными входами блока памяти. Входы выбора режима первого и второго ОЗУ являются соответственно первыми и вторыми входами выбора режима блока памяти. Y-разрядные выходы данных первого и второго ОЗУ являются соответственно первым и вторым Y-разрядным выходом данных блока памяти. Синхронизирующий вход блока памяти подключен к тактовым входам первого и второго ОЗУ.

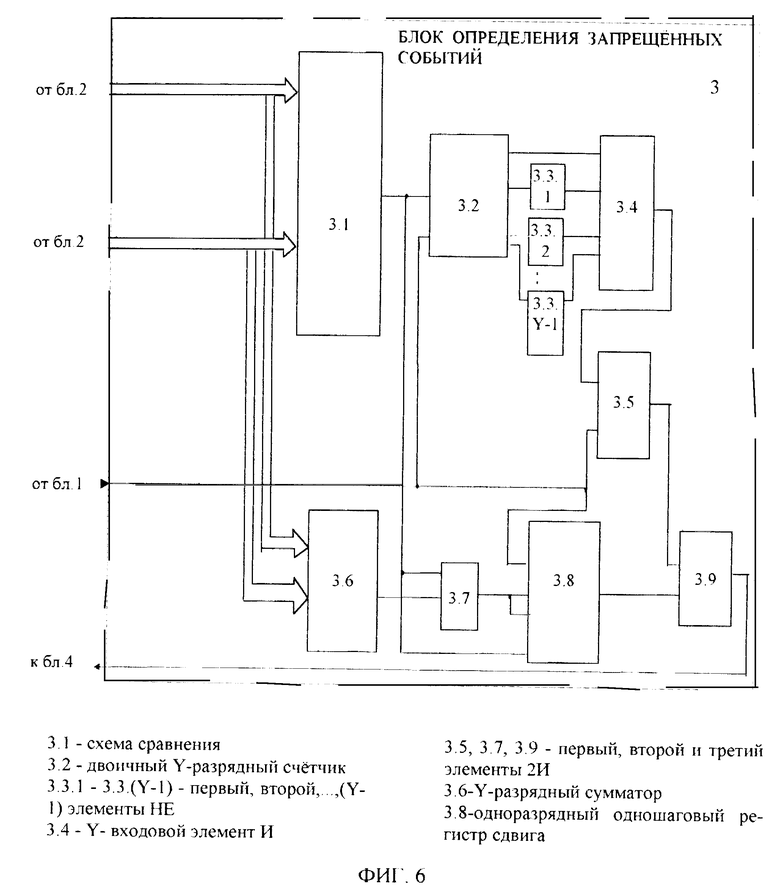

Блок определения запрещенных событий состоит из схемы сравнения, двоичного Y-разрядного счетчика, (Y-1) элементов НЕ, Y-входового элемента И, первого, второго и третьего элементов 2И, Y-разрядного сумматора, одноразрядного одношагового регистра сдвига. Первые и вторые Y-разрядные входы данных сумматора, первые и вторые Y- разрядные входы данных схемы сравнения, являются соответственно первыми и вторыми Y-разрядными входами данных блока определения запрещенных событий. Инверсный выход схемы сравнения подключен к счетному входу счетчика, а также к первому входу второго элемента 2И и управляющему входу одноразрядного регистра сдвига. Выход младшего выходного разряда счетчика прямо, а остальные (Y-1) выхода счетчика через (Y-1) элемента НЕ соответственно, подключены ко входам Y-входового элемента И, выход которого подключен к первому входу первого элемента 2И, выход которого подключен к первому входу третьего элемента 2И, выход которого является решающим выходом блока определения запрещенных событий. Решающий вход блока определения запрещенных событий подключен к обнуляющему входу счетчика, второму входу первого элемента 2И и обнуляющему входу одноразрядного регистра сдвига. Выход младшего разряда сумматора подключен ко второму входу второго элемента 2И, выход которого подключен к первому и второму информационным входам одноразрядного регистра сдвига, выход которого подключен ко второму входу третьего элемента 2И.

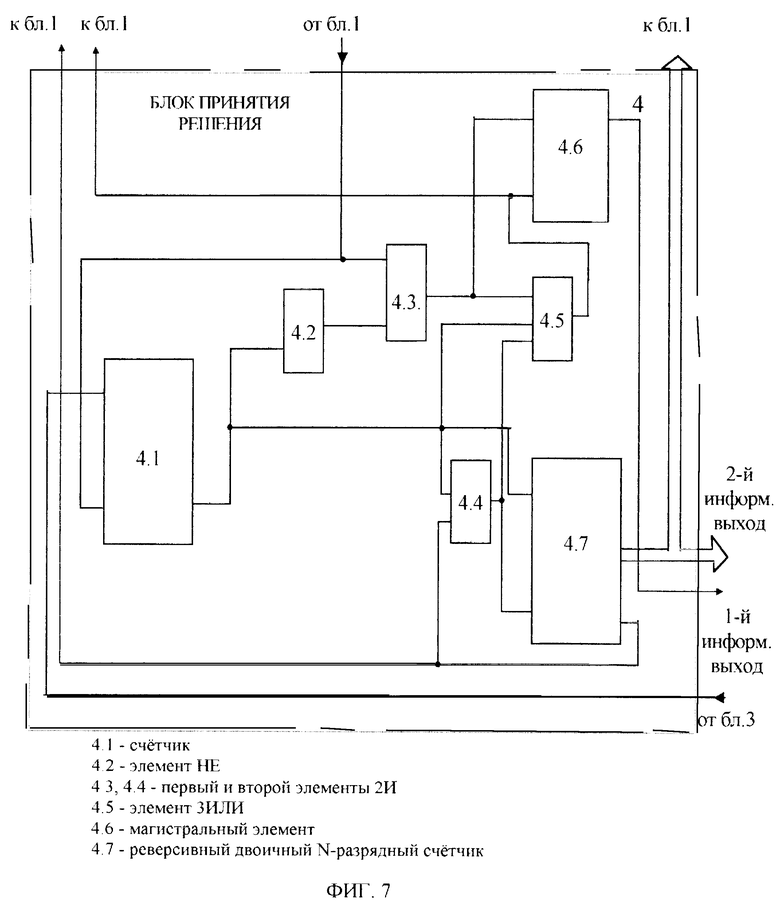

Блок принятия решения состоит из счетчика, элемента НЕ, первого и второго элементов 2И, элемента 3ИЛИ, магистрального элемента, реверсивного двоичного N-разрядного счетчика. Счетный вход счетчика является счетным входом блока принятия решения. Блокирующий вход блока принятия решения подключен к обнуляющему входу счетчика и первому входу первого элемента 2И. Выход переполнения счетчика соединен со счетным входом реверсивного счетчика, первым входом второго элемента 2И, вторым входом элемента 3ИЛИ, а также через элемент НЕ со вторым входом первого элемента 2И, выход которого подключен к первому входу элемента 3ИЛИ и входу данных магистрального элемента, выход которого является первым информационным выходом блока принятия решения. Выход второго элемента 2И подключен к третьему входу элемента 3ИЛИ и установочному входу реверсивного счетчика, N-разрядный выход данных которого является N-разрядным выходом размер окна и вторым N-разрядным информационным выходом блока принятия решения. Выход переполнения реверсивного счетчика соединен со вторым входом второго элемента 2И и является режимным выходом блока принятия решения. Выход элемента 3ИЛИ соединен со входом управления магистрального элемента и является выходом стоп анализа блока принятия решения.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленным техническим решениям, отсутствуют, что указывает на соответствие заявленных изобретений условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками заявленных объектов, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленных изобретений преобразований на достижение указанных технических результатов. Следовательно, заявленные изобретения соответствуют условию патентоспособности "изобретательский уровень".

Заявленный способ и устройство, его реализующее, поясняются чертежами:

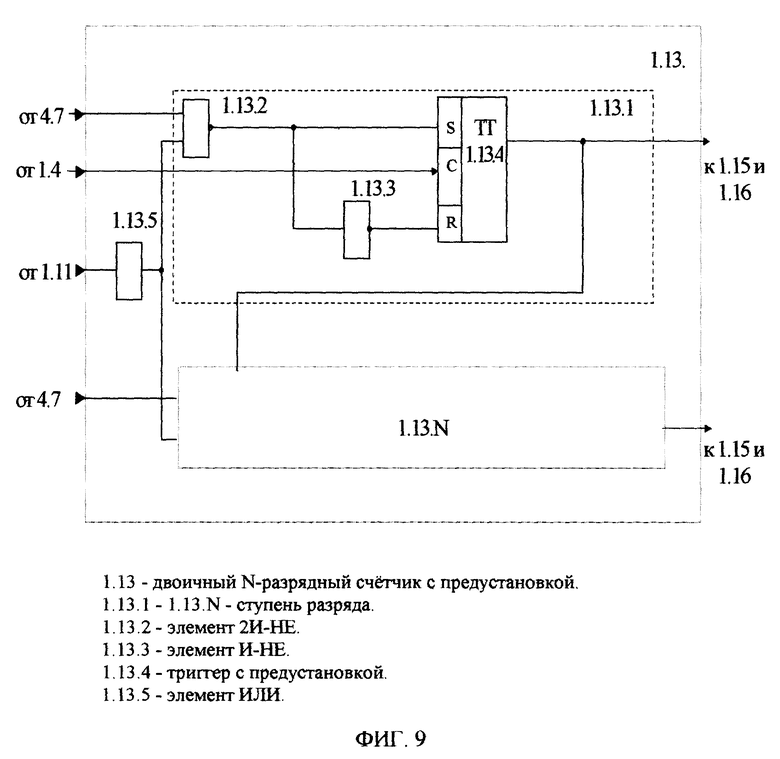

фиг. 1 - схема разбиения сигнала с СКК на вложенные подансамбли;

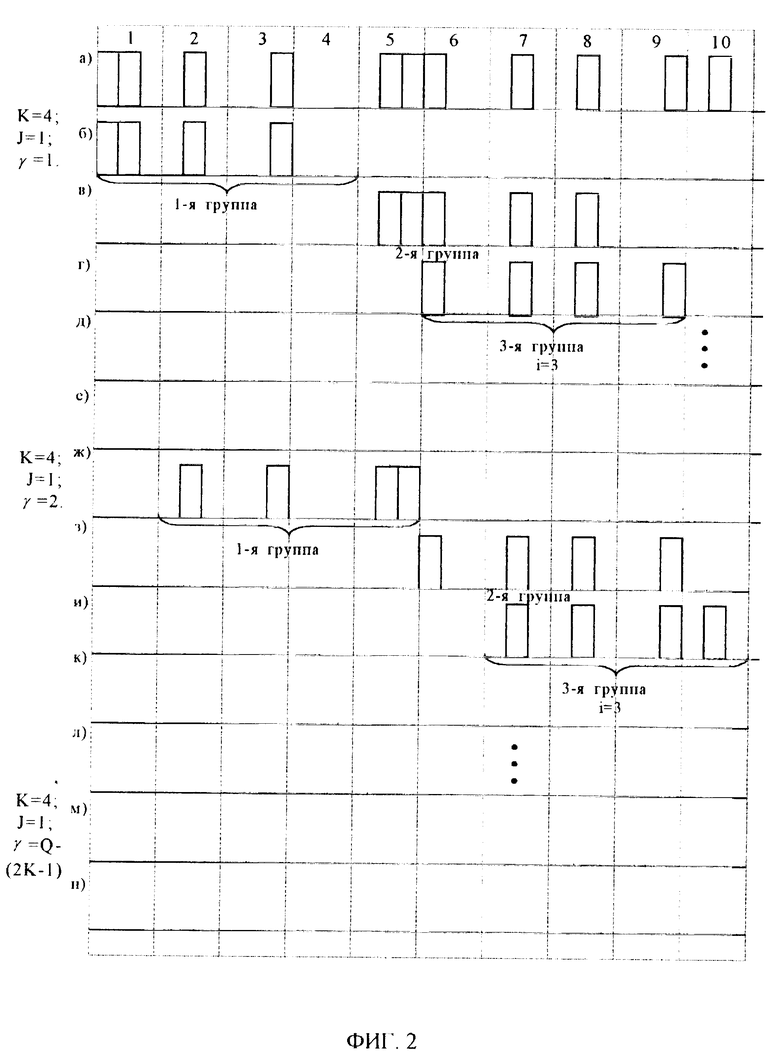

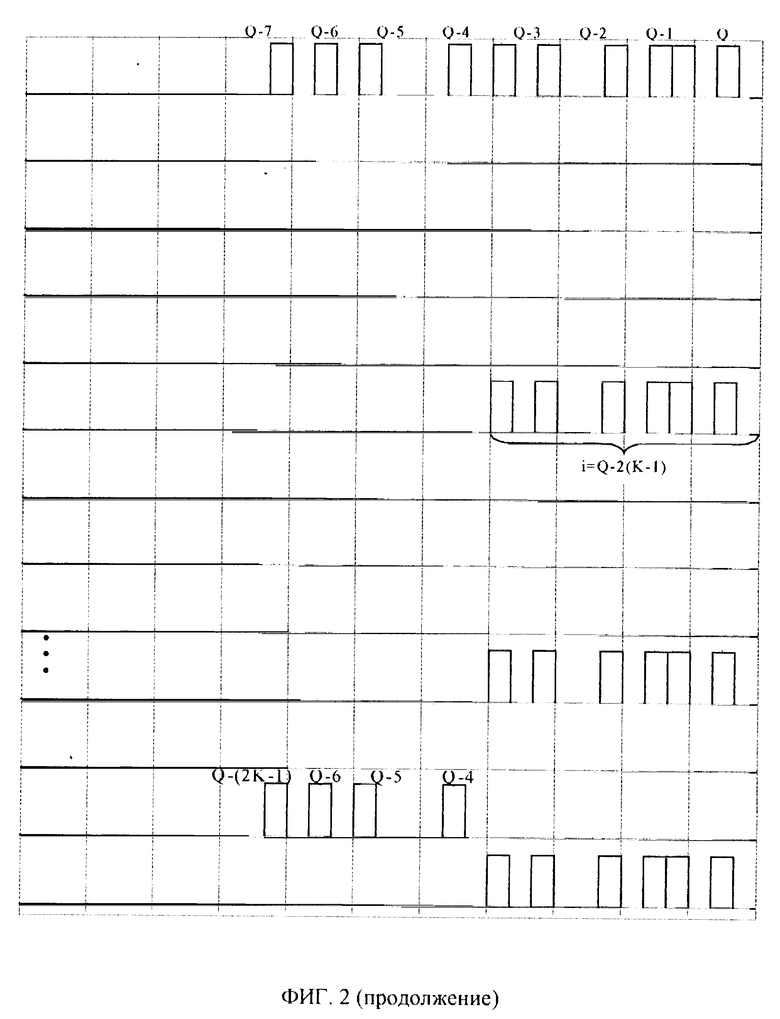

фиг. 2 - схема, поясняющая предлагаемый способ распознавания;

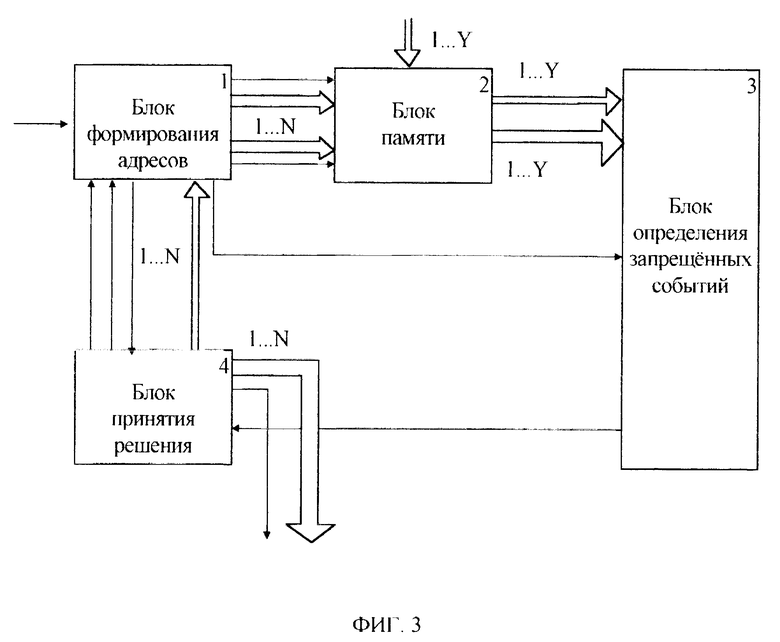

фиг. 3 - общая структурная схема устройства;

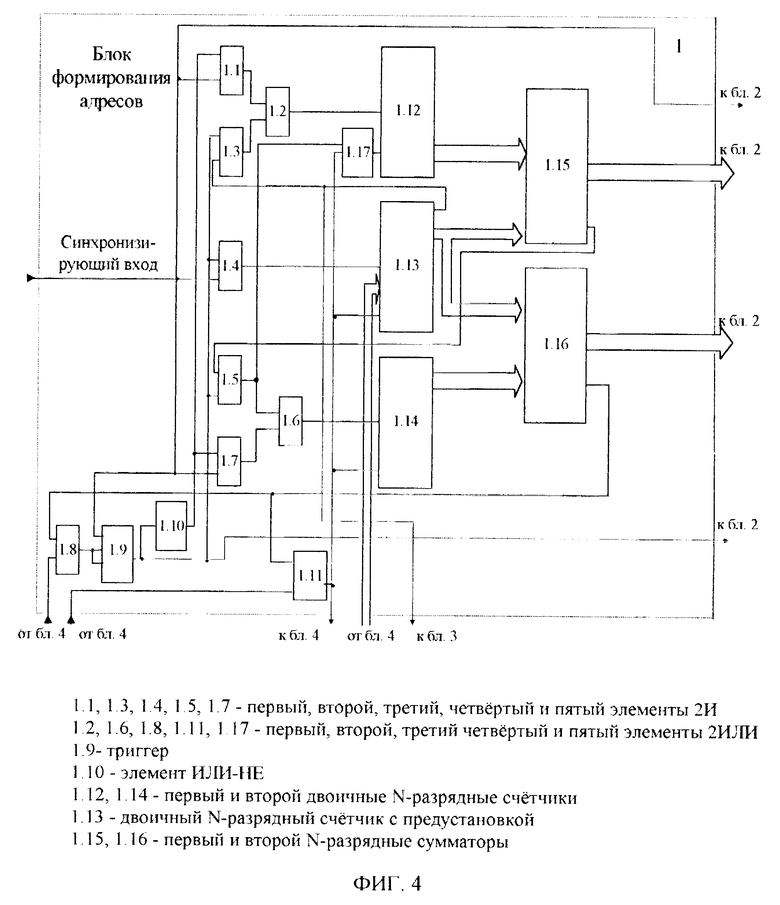

фиг. 4 - схема блока формирования адресов;

фиг. 5 - схема блока памяти;

фиг. 6 - схема блока определения запрещенных событий;

фиг. 7 - схема блока принятия решения;

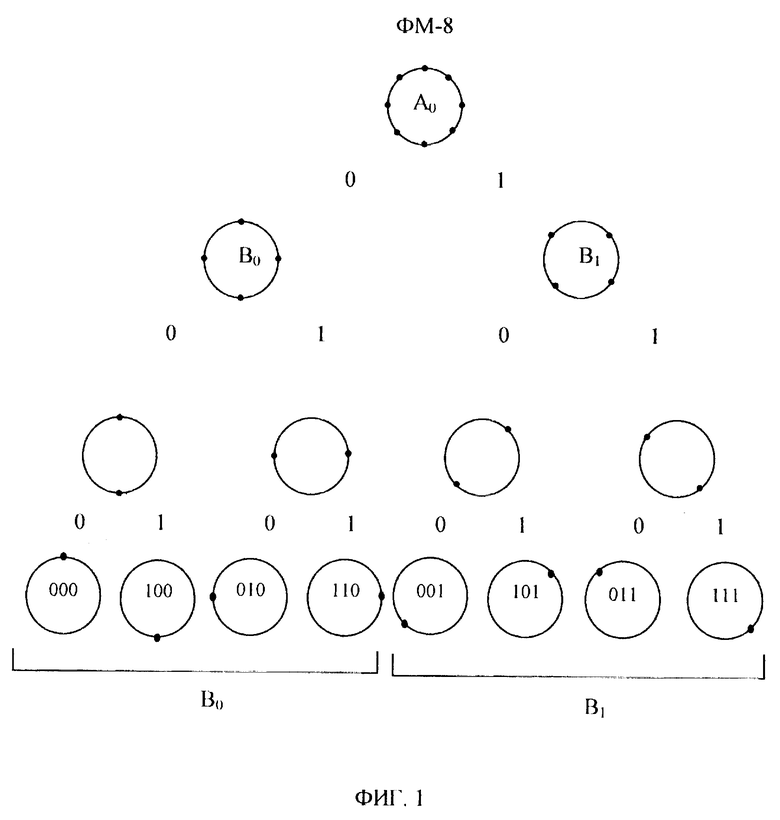

фиг. 8 - схема двоичного N-разрядного счетчика;

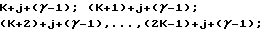

фиг. 9 - схема двоичного N-разрядного считчика с предустановкой.

Возможность реализации заявленного способа объясняется следующим образом.

Сигнально-кодовыми конструкциями (СКК) называются согласованные варианты ансамбля сигналов, помехоустойчивого и манипуляционного кодов, обеспечивающие улучшение энергетической и частотной эффективности канала связи (см. В. А. Григорьев. Передача сигналов в зарубежных информационно-технических системах. Санкт-Петербург: ВАС, 1995г.).

Широко используемый в СКК способ согласования кодера и модулятора основан на разбиении M-позиционного ансамбля сигналов на подансамбли с увеличивающимися минимальными расстояниями между сигнальными точками подансамблей при определенном правиле их двоичного кодирования. Правило такого разбиения для ансамбля сигналов ФМ-8 показано на фиг. 1. Здесь, в качестве геометрической интерпретации сигнала с фазовой манипуляцией ФМ-8 каждый из восьми возможных сигналов будет отображаться на поверхности окружности (радиус которой соответствует амплитуде сигнала) в виде сигнальных точек через каждые 45 градусов. Отбор сигналов, попадающих в каждый подансамбль, производится по кольцу через одну сигнальную точку.

Преимущественное развитие и практическое применение получили СКК на основе решетчатого кодирования. В СКК данного вида для передачи m бит применяется решетчатое кодирование с относительной скоростью R=m/m+1 совместно с ансамблем, состоящим из 2m+1 сигналов.

Способ распознавания передач, применяющих СКК на основе решетчатого кодирования, заключается в сравнении на выборке длиной Q канальных символов "скользящим окном" всех комбинаций длиной К друг с другом, где K/2 - предполагаемая память помехоустойчивого сверхточного кодера, и последующем подсчете частоты появления запрещенных событий. При отсутствии последних, или если их количество обусловлено только действием шумов в канале, выносится решение об обнаружении сигнально-кодовой конструкции и о величине памяти помехоустойчивого решетчатого кодера, равной половине длины окна.

Способ распознавания передач, применяющих СКК на основе решетчатого кодирования, основан на следующих утверждениях [9, стр. 55-67].

Утверждение 1. Для кодера решетчатого кода с относительной скоростью кодирования R=m/(m+1) и памятью K/2 максимальная длина двух различных путей в решетчатой диаграмме, порождающих одинаковые последовательности символов, равна ((K/2)-1).

Это утверждение справедливо и для известных решетчатых нелинейных кодов, так как привносимая нелинейность, как правило, не изменяет свойств симметричности, присущей линейным СКК. В любом случае длина двух различных путей должна быть ограничена, в противном случае код становится катастрофическим.

Обозначим через B0 и B1 вложенные подансамбли, полученные на первом шаге разбиения исходного ансамбля сигналов A0, и приведем второе утверждение (фиг. 1).

Утверждение 2. Если для СКК на основе решетчатого кодирования с относительной скоростью кодирования R=m/(m+1) длина двух различных путей в решетчатой диаграмме, порождающих одинаковые последовательности, равна (K/2)-1 символов, то у любых двух отрезков длиной K символов, взятых из кодовой последовательности, у которых совпадают все пары символов, кроме одной, символы этой пары принадлежат одновременно подансамблю B0 или B1.

Таким образом, при сравнении двух кодовых последовательностей друг с другом, или кодовой последовательности самой с собой окнами длиной K по принципу "каждое с каждым" будут отсутствовать события, называемые запрещенными, когда у сравниваемых окон будет единственная пара несовпадающих символов, и эти символы одновременно не принадлежат подансамблю B0 или B1.

Q реализаций анализируемого сигнала в виде последовательности Y-разрядных двоичных кодовых комбинаций принимаются и запоминаются на время полного цикла анализа. Указанная последовательность из Q Y-разрядных реализаций представлена в строке а) фиг. 2, где Y выбрано равной 3. В данной двоичной последовательности "1" соответствует импульс, а "0" его отсутствие. Каждая Y разрядная реализация запоминается под определенным номером γ от 1 до Q. Таким образом, появляется возможность проводить статистический анализ, полученной выборки реализаций, по интересующим признакам.

Для обработки: из имеющейся последовательности кодовых комбинаций группируют пару групп последовательностей по K реализаций в группе. Причем, Kmin= 2, выбирается из того расчета, что минимальное количество ячеек памяти в решетчатом кодере - одна, а значит минимальная допустимая труппа реализаций включает две кодовые комбинации. В настоящее время решетчатый кодер включает до нескольких десятков ячеек памяти, как правило не больше 30, поэтому ограничиваем доступное значение Kmax100, т.к. увеличение Kmax ведет к увеличению времени анализа. В первую группу входят первые K реализаций, во вторую входят реализации, начиная с K+1 по 2K. Например, в строке б) фиг. 2 показана первая группа реализаций для K=4, которая включает первую реализацию - 110, вторую - 010, третью - 001 и четвертую - 000. Во вторую группу - строка в) фиг. 2, входят соответственно пятая реализация (4+1=5)-011, шестая - 100, седьмая - 010 и восьмая - 010. В этих двух группах последовательно сравниваются соответствующие реализации и на основании сравнения принимается решение об их одинаковости или различии. Так первая реализация сравнивается с пятой, вторая с шестой, третья с седьмой, четвертая с восьмой и в результате делается вывод о том, что все они различны. После сравнения первой пары групп реализаций анализу подвергается вторая пара групп длиной K. Причем первая группа остается прежней, а вторая группа начинается уже с K+2 реализации, которая показана в строке г) фиг. 2 и включает соответственно шестую, седьмую, восьмую и девятую реализации. Они сравниваются так же, как и первая пара групп, но в отличие от первой пары, в данной паре групп реализаций вторая реализация первой группы - 010 и соответствующая ей седьмая реализация второй группы совпадают. На каждом следующем цикле сравнения первая группа реализаций в паре остается без изменений, а вторая смещается от начала на одну реализацию. Так продолжается до тех пор, пока во второй группе пары в K реализаций не запишется последняя Q реализация, например 010, показанная в строке е) фиг. 2. После этого в первой группе производится смещение на одну реализацию от начала и тогда первая группа будет включать вторую - 010, третью - 001, четвертую - 000 и пятую 011 реализации - строка ж) фиг. 2, соответственно сместится на одну реализацию и начало 2-ой группы, которая будет включать шестую - 100, седьмую - 010, восьмую - 010 и девятую - 001 реализации - строка з) фиг.2. Так же, как и в первом цикле, осуществляется сравнение групп. Процесс формирования групп и их сравнение будет продолжаться до тех пор, пока имеется возможность сохранить длину группы в K, т.е. до момента, показанного в строке м) и н) фиг.2, когда в первую группу реализаций входят Q-(2K-1) или (Q-7) - 001, (Q-6) - 010, (Q-5) - 100, (Q-4) - 010 реализации, а во вторую соответственно (Q-3) - 101, (Q-2) - 001, (Q-1) - 011, Q - 010 реализации.

Затем количество реализаций в группе уменьшается на одну, т. е. например, в первую группу будут входить 1, 2 и 3 реализации, а во вторую 4, 5 и 6, т. е. их становится K-1 реализация в группе и цикл их сравнения повторяется, пока длина групп не достигнет выбранного порогового значения - Kmin. Этим реализуется способ сравнения групп "скользящим окном" каждая с каждой.

На каждом цикле сравнения пары групп реализаций в "скользящем окне" подсчитывается число не совпавших реализаций. Если число несовпадений равно "1", то проверяют, принадлежит ли данная отличающаяся пара реализаций разным подансамблям разбиения (B0 или B1). Это делается сравнением младших разрядов кодовых комбинаций, т. к. из фиг.1 следует, что реализации, принадлежащие одному подансамблю, имеют одинаковое значение младшего разряда. Например, пусть сравниваются две группы по четыре реализации:

первая - 100, 010, 111, 101

вторая - 001, 010, 111, 101

видно, что различны только первые реализации этих групп - 100 и 001, которые принадлежат соответственно подансамблям B0 и B1, т.е. разным подансамблям. Следовательно, суммированием значений младших разрядов кодовых комбинаций принимается решение о принадлежности реализаций к разным подансамблям, если сумма равна "1" и одинаковым, если равна "0". Затем подсчитывается количество реализаций, принадлежащих разным подансамблям, сравнивается их число с пороговым значением, после чего идентифицируется класс сигнала. При превышении порога принимают решение об отсутствии СКК, в противном случае - о наличии СКК. Причем, в случае обнаружения СКК, длина памяти кодера равна K/2.

Результаты расчетов и моделирования позволяют сделать вывод о том, что этот способ не требует значительных временных затрат, так для СКК с K/2=2, 3 и 4 требуемый объем выборки не превышает Q=200, 640 и 2500 канальных символов соответственно.

Устройство распознавания классов сигналов, показанное на фиг. 3, состоит из: блока формирования адресов 1, блока памяти 2, блока определения запрещенных событий 3, блока принятия решения 4, первый информационный выход которого является первым информационным выходом устройства. Синхронизирующий вход блока формирования адресов 1 является синхронизирующим входом устройства. Два N-адресных выхода блока формирования адресов 1 подключены соответственно к двум N-адресным входам блока памяти 2. Выход управления режимом блока формирования адресов 1 подключен ко входу выбора режима блока памяти 2. Выход конец окна блока формирования адресов 1 подключен к решающему входу блока определения запрещенных событий 3. Сигнализирующий выход блока формирования адресов 1 подключен к блокирующему входу блока принятия решения 4, а установочный вход блока формирования адресов 1 подключен к выходу стоп - анализа блока принятия решения 4. N-разрядный вход размер окна блока формирования адресов 1 подключен соответственно к N-разрядному выходу размер окна блока принятия решения 4. Синхронизирующий выход блока формирования адресов 1 подключен к синхронизирующему входу блока памяти 2. Режимный вход БФА 1 подключен к режимному выходу БПР 4. Первые и вторые Y-разрядные выходы данных блока памяти 2 подключены соответственно к первым и вторым Y-разрядным входам данных блока определения запрещенных событий 3. Y-информационных входов блока памяти 2 являются Y информационными входами устройства. Решающий выход блока определения запрещенных событий 3 подключен к счетному входу блока принятия решения 4, а второй N-разрядный информационных выхода блока принятия решения 4 является вторым N-разрядным информационным выходом устройства.

Блок формирования адресов 1, показанный на фиг. 4, предназначен для управления записью и чтением Q реализаций сигнала в блоке памяти 2 путем формирования соответствующей последовательности адресов записи/чтения и состоит из первого 1.12 и второго 1.14 двоичных N-разрядных счетчиков, двоичного N-разрядного счетчика с предустановкой 1.13, первого 1.1, второго 1.3, третьего 1.4, четвертого 1.5 и пятого 1.7 элементов 2И, первого 1.2, второго 1.6, третьего 1.8, четвертого 1.11 и пятого 1.17 элементов 2ИЛИ, JK-триггера 1.9, элемента ИЛИ-НЕ 1.10, первого 1.15 и второго 1.16 N-разрядных сумматоров. Синхронизирующий вход блока формирования адресов 1 подключен соответственно к синхронизирующему выходу блока формирования адресов 1, тактовому входу JK-триггера 1.9, второму входу первого элемента 2И 1.1, второму входу третьего элемента 2И 1.4, второму входу пятого элемента 2И 1.7. Установочный вход блока формирования адресов 1 подключен ко второму входу четвертого элемента 2ИЛИ 1.11, выход которого подключен к сигнализирующему выходу блока формирования адресов 1, установочному входу второго двоичного N-разрядного счетчика 1.14, двоичного N-разрядного счетчика с предустановкой 1.13 и первому входу пятого элемента 2ИЛИ 1.17, выход которого подключен к установочному входу первого двоичного N-разрядного счетчика 1.12. Режимный вход БФА1 подключен ко второму входу третьего элемента 2ИЛИ 1.8. Выход третьего элемента 2ИЛИ 1.8 подключен к первому и второму информационным входам JK-триггера 1.9, выход которого подключен к входу элемента ИЛИ-НЕ 1.10, выходу управления режимом блока формирования адресов 1, первому входу второго элемента 2И 1.3, первому входу третьего элемента 2И 1.4, второму входу четвертого элемента 2И 1.5. Инверсный выход элемента ИЛИ-НЕ 1.10 подключен к первому входу первого элемента 2И 1.1 и первому входу пятого элемента 2И 1.7. Выход первого элемента 2И 1.1 подключен к первому входу первого элемента 2ИЛИ 1.2, второй вход которого подключен к выходу второго элемента 2И 1.3, а выход к счетному входу первого двоичного N-разрядного счетчика 1.12. Выход третьего элемента 2И 1.4 подключен к счетному входу двоичного N-разрядного счетчика с предустановкой 1.13, выход переполнения которого подключен ко второму входу второго элемента 2И 1.3 и является выходом конец окна блока формирования адресов 1. N-разрядный информационный вход двоичного N-разрядного счетчика с предустановкой 1.13 является N-разрядным входом размер окна блока формирования адресов 1. Выход четвертого элемента 2И 1.5 подключен ко второму входу пятого элемента 2ИЛИ 1.17 и первому входу второго элемента 2ИЛИ 1.6, второй вход которого подключен к выходу пятого элемента 2И 1.7, а выход к счетному входу второго двоичного N-разрядного счетчика 1.14. N-разрядный выход которого, подключен ко второму N-разрядному информационному входу второго сумматора 1.16, выход переполнения которого подключен к первому входу четвертого элемента 2ИЛИ 1.11 и первому входу третьего элемента 2ИЛИ 1.8. N-разрядный выход счетчика с предустановкой 1.13 подключен соответственно ко второму N-разрядному информационному входу первого сумматора 1.15 и первому N-разрядному информационному входу второго сумматора 1.16. N-разрядный выход первого счетчика 1.12 подключен к первому N-разрядному информационному входу первого сумматора 1.15, N-разрядный выход которого является первым N-адресным выходом блока формирования адресов, а выход переполнения подключен к первому входу четвертого элемента 2И 1.5. N-разрядный выход второго сумматора 1.16 является вторым N-адресным выходом блока формирования адресов 1.

В свою очередь триггер 1.9 предназначен для формирования управляющих напряжений выбора режима работы устройства - запись Q реализаций сигнала или их анализ. Схема такого триггера известна и его работа описана например в [5, стр. 49, рис. 2.32 б], где инверсный выход и вход обнуления не используются.

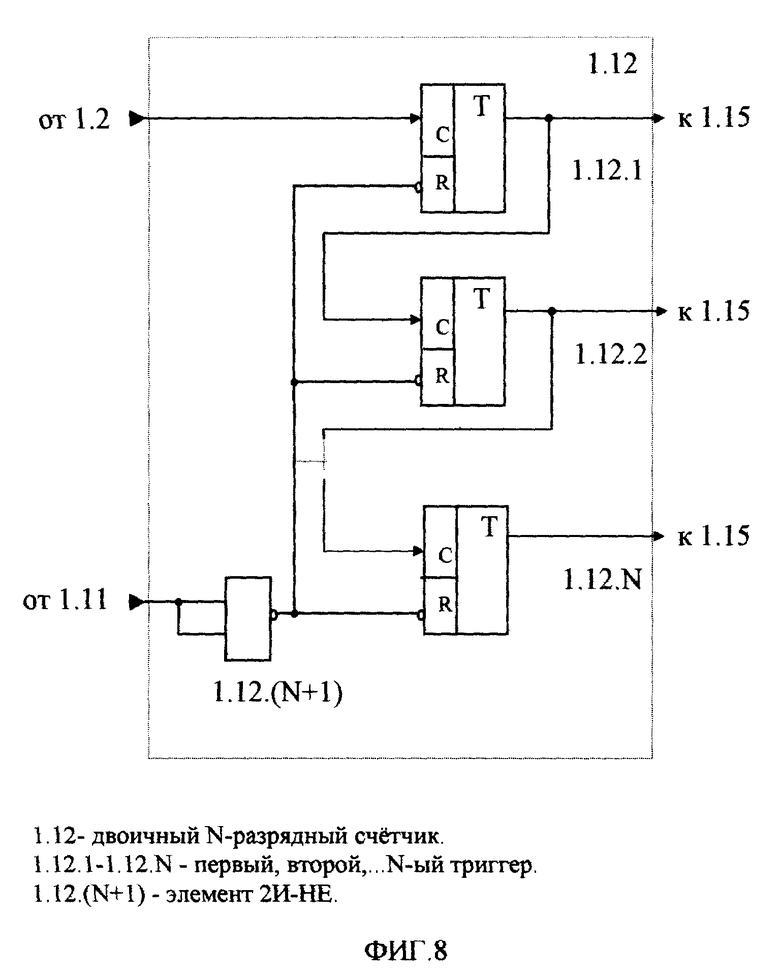

Двоичный N-разрядный счетчик 1.12 предназначен для подсчета тактовых импульсов синхронизации, поступающих на его вход в режиме записи реализаций, а также подсчета импульсов смещения, поступающих с выхода переполнения двоичного десятиразрядного счетчика с предустановкой 1.13 в режиме анализа. Схема такого счетчика 1.12 известна и его работа описана например в [5, стр. 63, рис. 2.51]. В заявляемом блоке формирования адресов 1 с учетом особенностей взаимосвязей с другими элементами схема счетчика 1.12 приобретает вид, показанный на фиг. 8, и включает: совокупность N двухступенчатых триггеров JK типа. Выходы триггеров соединены соответственно со счетными входами последующего триггера и являются соответственно N выходами счетчика 1.12, а вход первого триггера - счетным входом счетчика 1.12. Параллельно к установочным входам всех триггеров 1.12.1-1.12.N через элемент 2И-НЕ 1.12.(N+1) подключен установочный вход счетчика 1.12.

Двоичный N-разрядный счетчик 1.14 предназначен для подсчета тактовых импульсов синхронизации, поступающих на его вход в режиме записи реализаций, а также подсчета импульсов смещения, поступающих с выхода переполнения сумматора 1.15 при работе устройства в режиме анализа. Схема счетчика 1.14 и его работа аналогична схеме и работе счетчика 1.12.

Двоичный N-разрядный счетчик с предустановкой 1.13 предназначен для подсчета тактовых импульсов синхронизации, поступающих на его вход в режиме анализа, и формирует тем самым размер окна, анализируемый в конкретный момент времени анализа.

Схема счетчика 1.13 известна и ее работа описана, например в [5, стр. 70, рис. 2.58.б].

В заявляемом БФА 1, с учетом особенностей взаимосвязей с другими элементами схемы счетчик 1.13 приобретает вид, показанный на фиг. 9, и включает совокупность N триггеров 1.13.1-1.13.N и элемент ИЛИ 1.13.5. Выходы триггеров соединены соответственно со счетными входами последующего триггера и являются соответственно N выходами счетчика 1.13, а вход первого триггера - со счетным входом счетчика 1.13, кроме того каждая ступень 1.13.1- 1.13.N включает: элемент 2И-НЕ 1.13.2, элемент И-НЕ 1.13.3 и триггер 1.13.4, выход элемента 2И-НЕ 1.13.2 соединен с S входом триггера 1.13.4 и через элемент И-НЕ 1.13.3 с R входом триггера 1.13.4, вход элемента ИЛИ 1.13.5 подключен к установочному входу счетчика 1.13, а его выход параллельно подключен ко вторым входам элементов 2И-НЕ 1.13.2 каждой из N ступеней 1.13.1- 1.13.N счетчика соответственно, а первые входы элемента 2И-НЕ 1.13.2 каждой ступени соединены соответственно с информационными входами счетчика 1.13.

Сумматор 1.15 предназначен в режиме записи для формирования адреса записываемой в блок памяти 2 комбинации, а в режиме чтения формирует адрес извлекаемой из блока памяти комбинации и при достижении конечного значения выдает сигнал смещения анализируемого окна на один символ.

Схема построения сумматора 1.15, реализующая такие задачи в заявляемом устройстве, известна и описана, например в [5, стр. 75, рис. 2.63 б.].

Сумматор 1.16 предназначен в режиме "записи" для формирования адреса записываемой в блок памяти 2 комбинации, а в режиме "чтения" формирует адрес извлекаемой из блока памяти комбинации. При переполнении сумматора он формирует сигнал о переводе устройства в режим "анализа" ("чтения") или "записи".

Схема построения сумматора 1.16, реализующая такие задачи в заявляемом устройстве, известна и описана, например в [5, стр. 75, рис. 2.63 б.].

Блок памяти 2, показанный на фиг. 5, предназначен для запоминания Q реализаций сигнала на время, необходимое для их анализа, и состоит из первого и второго динамических оперативных запоминающих устройств 2.1 и 2.2. Y информационных входа ОЗУ 2.1 и 2.2 являются соответственно Y информационными входами блока памяти 2. N-разрядные адресные входы первого и второго ОЗУ 2.1 и 2.2 являются соответственно первыми и вторыми N адресными входами блока памяти 2. Входы выбора режима первого и второго ОЗУ 2.1 и 2.2 являются входом выбора режима блока памяти 2. Тактовые входы первого 2.1 и второго 2.2 ОЗУ являются синхронизирующим входом блока памяти. Y-разрядные информационные выходы первого 2.1 и второго 2.2 ОЗУ являются соответственно первыми и вторыми Y-разрядными выходами данных блока памяти 2.

Блок определения запрещенных событий 3, показанный на фиг. 6, предназначен для выявления запрещенных событий путем сравнения двух групп реализаций длиной K, селекции вариантов, когда в паре групп реализаций только одна пара реализаций не совпадает и определении, принадлежат ли эти реализации подансамблю B0 или B1. Состоит из схемы сравнения 3.1, двоичного Y-разрядного счетчика 3.2, (Y-1) элементов НЕ, Y-входового элемента И 3.4 первого 3.5, второго 3.7 и третьего 3.9 элементов 2И, сумматора 3.6, одноразрядного одношагового регистра сдвига 3.8. Первые и вторые Y-разрядные входы данных сумматора 3.6, первые и вторые Y-разрядные входы данных схемы сравнения 3.1 являются соответственно первыми и вторыми Y-разрядными входами данных блока определения запрещенных событий 3. Инверсный выход схемы сравнения 3.1 подключен к счетному входу счетчика 3.2, а также к первому входу второго элемента 2И 3.7 и управляющему входу одноразрядного регистра сдвига 3.8. Выход младшего выходного разряда счетчика 3.2 прямо, а остальные (Y-1)выхода счетчика 3.2 через (Y-1) элемента НЕ 3.3.1- 3.3.(Y-1) соответственно подключены ко входам Y-входового элемента И 3.4, выход которого подключен к первому входу первого элемента 2И 3.5, выход которого подключен к первому входу третьего элемента 2И 3.9, выход которого является решающим выходом блока определения запрещенных событий 3. Решающий вход блока определения запрещенных событий 3 подключен к обнуляющему входу счетчика 3.2, второму входу первого элемента 2И 3.5 и обнуляющему входу одноразрядного регистра сдвига 3.8. Выход младшего разряда сумматора 3.6 подключен ко второму входу второго элемента 2И 3.7, выход которого подключен к первому и второму информационным входам одноразрядного регистра сдвига 3.8, выход которого подключен ко второму входу третьего элемента 2И3.9.

Схема сравнения 3.1 предназначена для сравнения пары реализаций между собой и выдачи соответственно информационного сигнала, в случае если реализации различаются.

Схема построения схемы сравнения 3.1, реализующая такие задачи в заявляемом устройстве, известна и описана, например в [5, стр. 83, рис. 2.71 б], где выходы А>Б и А<Б не используются.

Двоичный Y-разрядный счетчик 3.2 предназначен для подсчета числа различающихся комбинаций в анализируемом окне.

Схема построения Y-разрядного счетчика 3.2, реализующая такие задачи в заявляемом устройстве, известна и аналогична схемам двоичных N-разрядных счетчиков 1.12 и 1.14. Двоичный Y-разрядный сумматор 3.6 предназначен для проверки анализируемой пары комбинаций на четность в младшем разряде.

Схема построения двоичного Y-разрядного сумматора 3.6, реализующая такие задачи в заявляемом устройстве, известна и состоит из Y одноразрядных полных сумматоров, описанных, например в [5, стр. 75, рис. 2.63. б], где используется только выход младшего разряда.

Одноразрядный одношаговый регистр сдвига 3.8 предназначен для запоминания и передачи на его выход значения нечетности младшего разряда суммы пары неодинаковых анализируемых комбинаций.

Схема построения одноразрядного одношагового регистра сдвига, реализующая такие задачи в заявленном устройстве, известна и описана, например в [5, стр. 49, рис. 2.32 б], которая представляет собой счетный JK триггер с установкой.

Блок принятия решения 4, показанный на фиг.7, предназначен для последовательного перебора прогнозируемого размера окна для анализа, выдачи на выход устройства признака наличия СКК с решетчатым кодированием и размера памяти помехоустойчивого решетчатого кодера.

Блок принятия решения состоит из счетчика 4.1, элемента НЕ 4.2, первого 4.3 и второго 4.4 элементов 2И, элемента 3ИЛИ 4.5, магистрального элемента 4.6, реверсивного двоичного N-разрядного счетчика 4.7. Счетный вход счетчика 4.1 является счетным входом блока принятия решения 4. Блокирующий вход блока принятия решения 4 подключен к обнуляющему входу счетчика 4.1 и первому входу первого элемента 2И 4.3. Выход переполнения счетчика 4.1 соединен со счетным входом реверсивного счетчика 4.7, первым входом второго элемента 2И 4.4, вторым входом элемента 3ИЛИ 4.5, а также через элемент НЕ 4.2 со вторым входом первого элемента 2И 4.3, выход которого подключен к первому входу элемента 3ИЛИ 4.5 и входу данных магистрального элемента 4.6, выход которого является первым информационным выходом блока принятия решения 4. Выход второго элемента 2И 4.4 подключен к третьему входу элемента 3ИЛИ 4.5 и установочному входу реверсивного счетчика 4.7, N-разрядный выход данных которого является N-разрядным выходом размер окна и вторым N-разрядным информационным выходом блока принятия решения 4. Выход переполнения реверсивного счетчика 4.7 соединен со вторым входом элемента 2И 4.4 и является режимным выходом БПР 4. Выход элемента 3ИЛИ 4.5 соединен со входом управления магистрального элемента 4.6 и является выходом стоп анализа блока принятия решения 4.

Счетчик 4.1 предназначен для подсчета сигналов - "запрещенное событие", поступающих из блока определения запрещенных событий на счетный вход счетчика, счетчик 4.1 с предустановкой, порог переполнения счетчика может быть фиксированным, тогда счетчик 4.1 работает в режиме обычного N-разрядного двоичного счетчика или изменяться в процессе функционирования, в этом случае значение порога будет подаваться на информационные входы счетчика 4.1. В любом случае в качестве информационного выхода будет использоваться один из N выходов счетчика.

Схема построения счетчика 4.1, реализующая такие задачи в заявляемом устройстве, в режиме фиксированного порога известна и описана, например в [5, стр. 63-64, рис. 2.51. б], где счетный вход C1 не используется.

Магистральный элемент (МЭ) 4.6 предназначен для формирования помехоустойчивого выходного сигнала на первый информационный выход устройства.

Схема построения МЭ 4.6, реализующая такие задачи в заявляемом устройстве, известна и описана, например в [5, стр. 32, рис. 2.11.б].

Реверсивный двоичный N-разрядный счетчик 4.7 предназначен для формирования информационного сигнала о величине анализируемого окна и выдачи формируемых результатов в блок формирования адресов 1 и на второй информационный выход устройства, счетчик 4.7 работает в режиме вычитания.

Схема построения реверсивного счетчика 4.7, реализующая такие задачи в заявляемом устройстве, известна и описана, например в [10, стр. 123, рис. 3.16], где N-разрядный выход снимается с выходов Tу триггеров.

Все остальные элементы, входящие в заявляемое устройство (фиг. 4, 5, 6, 7, 8, 9), известны. Так принцип работы и схема элемента 2И и (У-1)И приведены в [10, стр.48, рис. 2.7], ИЛИ-НЕ в [10, стр.62, рис. 2.18], ОЗУ в [II, стр.267].

Заявленное устройство работает следующим образом.

Устройство имеет два режима работы:

- "запись" - запоминаются в соответствующих ячейках памяти ОЗУ 2.1 и 2.2 принимаемые значения реализаций, объемом Q

- "анализ" (или "чтение") - производится распознавание СКК в принимаемом сигнале и определение длины памяти помехоустойчивого решетчатого кодера.

Исходному состоянию устройства в режиме "запись" соответствуют нулевые значения на выходах всех сумматоров, счетчиков, регистра сдвига, магистрального элемента и триггера 1.9, кроме счетчика 4.7, на выходах данных которого - значение, соответствующее Kmax, в этом режиме тактовые импульсы, подаваемые на синхронизирующий вход устройства, поступают на элементы 2И 1.1, 1.4, 1.7 и синхронизирующие входы ОЗУ 2.1 и 2.2. В это время на выходе триггера 1.9 "0", который через элемент ИЛИ-НЕ 1.10 инвертируется в "1", которая поступает на входы элементов 2И 1.1 и 1.7 и открывает их, причем тактовые импульсы через элементы 2ИЛИ 1.2 и 1.6 поступают соответственно на счетные входы двоичных N-разрядных счетчиков 1.12 и 1.14, а с выходов счетчиков на счетные входы сумматоров 1.15 и 1.16 соответственно, формируя тем самым последовательность адресов от 1 до Q, равных по объему памяти ОЗУ 2.1 и 2.2. В блоке памяти 2, синхронно с тактовыми импульсами, в соответствующие ячейки памяти ОЗУ 2.1 и 2.2 запоминаются соответствующие значения реализаций сигнала, т.к. с выхода триггера 1.9 поступает "0", который соответствует режиму "запись" для ОЗУ 2.1 и 2.2. Сумматор 1.16 подсчитывает число адресов и по достижении Q вырабатывает на выходе переполнения "1". Этот сигнал поступает на вход элемента 2ИЛИ 1.11, открывает его и подает сигнал "1" на входы начальной установки счетчиков 1.13, 1.14, а через элемент 2ИЛИ 1.17 на вход начальной установки счетчика 1.12 блока формирования адресов 1 и счетчика 4.1 блока принятия решения 4. Кроме того, этот же сигнал, попадая через элемент 2ИЛИ 1.8 на информационные входы триггера 1.9, перебрасывает его состояние из "0" в "1", тем самым переводя все устройство в режим "анализа" ("чтения").

В этом режиме БФА 1 формирует адреса для выборки реализаций из ОЗУ 2.1 и 2.2 блока памяти 2. В режиме "анализа" сигналом "0" с выхода элемента ИЛИ-НЕ 1.10 закрываются элементы 2И 1.1 и 1.7 и таким образом тактовые импульсы не проходят через них на счетчики 1.12 и 1.14 соответственно. Одновременно "1" с выхода триггера 1.9 подается на элементы 2И 1.3, 1.4 и 1.5. Таким образом, элемент 1.4 пропускает тактовые импульсы на вход счетчика с предустановкой 1.13. Счетчик 1.13 подсчитывает число тактовых импульсов, причем порог переполнения счетчика устанавливается соответствующим значением N-разрядного выхода данных реверсивного двоичного N-разрядного счетчика 4.7 БПР 4, которое соответствует анализируемому в настоящий момент времени размеру окна K. С выхода счетчика 1.13 значения от 1 до K поступают соответственно на второй вход сумматора 1.15 и первый вход сумматора 1.16, а выход переполнения счетчика 1.13 формирует сигнал, пропускающий счетный импульс на счетчик 1.12 через элемент 2И 1.3 и 2ИЛИ 1.2, а также формирует сигнал "конец окна" выход БФА 1. Счетчик 1.12 последовательно формирует числа от 0 до Q-K, а соответственно сумматор 1.15 формирует числа от 1 до Q, которые являются адресами для блока памяти 2. При переполнении сумматора 1.15 с его выхода переполнения подается сигнал, открывающий элемент 2И 1.5 и, во-первых, устанавливающий через пятый элемент 2ИЛИ 1.17, в начальное положение счетчик 1.12, а во-вторых, пропускающий через элемент 2ИЛИ 1.6 счетный импульс на счетчик 1.14. Т.О. счетчик 1.14 последовательно формирует значения от 0 до Q-K и передает эту информацию на сумматор 1.16, который соответственно формирует в блоке памяти 2 адреса, сначала от 1 до K, затем от 2 до K+1 и т.д. до от Q-(2K-1) до Q-K, причем, когда с выхода переполнения сумматора 1.15 поступает "1", происходит увеличение на "1" значения счетчика 1.14 и повторный проход сравнения пар реализаций до переполнения сумматора 1.15, этим реализуется принцип сравнения по методу "скользящего окна". В режим "запись" устройство переводится при переполнении сумматора 1.16, а также при поступлении положительного импульса на элемент 2ИЛИ 1.8 с выхода переноса разряда реверсивного счетчика 4.7 блока принятия решения 4, которые переводят триггер 1.9 в состояние "0".

Далее, в режиме "анализа" осуществляется последовательное попарное сравнение реализаций сигнала, поступающих из соответствующих ячеек ОЗУ 2.1 и 2.2 на схему сравнения 3.1 и Y-разрядный сумматор 3.6 БОЗС 3. Схема сравнения вырабатывает управляющие сигналы для счетчика 3.2 только тогда, когда реализации сигнала не равны между собой. Счетчик 3.2 подсчитывает количество несовпадений и, если их ровно одно в анализируемом окне, т.е. в младшем разряде счетчика "1", то Y-входовой элемент И 3.4 пропускает положительный импульс на элемент 2И 3.5. Y-разрядный сумматор 3.6 работает как схема сравнения, причем нас интересует только значение суммы в младшем разряде сумматора, если сравниваемые реализации сигнала отличаются в младшем разряде, то на выходе сумматора 3.6 "1". Эта "1" поступает на вход элемента 2И 3.7 и в зависимости от сигнала с выхода схемы сравнения 3.1 ("0" - если реализации совпали и "1" - если не совпали) пропускает на вход регистра сдвига 3.8 управляющий сигнал. В свою очередь регистр сдвига 3.8 вырабатывает положительный управляющий сигнал на вход элемента 2И 3.9 только в том случае, если приходит "1" с элемента 2И 3.7 и схемы сравнения 3.1. Поэтому, на выходе элемента 2И 3.9 и БОЗС 3 решающий сигнал, равный "1", может появиться в конце каждого цикла, равного размеру окна, который в качестве сигнала логической "1" (конец окна) поступает на решающий вход БОЗС 3 с выхода конец окна БФА 1. Сигнал конец окна в случае, если на первом входе элемента 2И 3.5 "1" через второй вход открывает этот элемент и подает на первый вход элемента 2И 3.9 положительный импульс, в свою очередь регистр сдвига 3.8 формирует сигнал логической "1" и подает его на второй вход элемента 2И 3.9 только в том случае, если в младшем разряде регистра сдвига записана "1". Сигнал "запрещенное событие", равный "1", на выходе элемента 2И 3.9 появляется только в том случае, если в анализируемом окне только одна пара реализаций отличается между собой и причем обе они одновременно не принадлежат подансамблям B0 и B1. Добавим, что сигнал - конец окна дополнительно переводит в исходное состояние счетчик 3.2 и регистр сдвига 3.8 для последующего цикла анализа.

В блоке принятия решения (БПР) 4 сигнал "запрещенное событие" с решающего выхода БОЗС 3 поступает на счетный вход счетчика 4.1, причем этот счетчик выдает управляющий сигнал, равный "1", только при превышении установленного для него порога. В остальных случаях на его выходе присутствует логический "0". Если же число запрещенных событий окажется больше установленного порога, то управляющий сигнал счетчика 4.1 открывает элемент 3ИЛИ 4.5 и формирует сигнал стол-анализ, который обнуляет счетчики 1.12. 1.13, 1.14 БФА 1, одновременно сигнал, равный "1", подается на счетный вход реверсивного счетчика 4.7, который работает в режиме вычитания и уменьшает его состояние на единицу, т. е. размер окна, по которому производится анализ, уменьшается, новое значение окна записывается с выхода данных счетчика 4.1 на установочные входы счетчика с предустановкой 1.13 БФА 1. Анализ реализаций сигнала, хранящихся в БП 2, повторится с новой длиной окна. По достижении минимально достижимого размера окна выход переполнения счетчика 4.7 формирует сигнал логической "1", который переводит триггер 1.9 БФА 1 в состояние "0", что соответствует режиму работы устройства "запись". Открывает элемент 2И 4.4, который через элемент 3ИЛИ 4.5 и 1.11 обнуляет счетчики 1.12, 1.13, 1.14. При этом на выходе магистрального элемента 4.6 будет присутствовать логический "0", что сигнализирует об отсутствии СКК в сигнале, т.к. "1" на выходе счетчика 4.1 инвертируется элементом НЕ 4.2, запирает элемент 2И 4.3 и подает "0" на вход данных магистрального элемента 4.6. Если же на выходе счетчика 4.1 "0", то при переполнении сумматора 1.16 БФА 1 на первый вход элемента 2И 4.3 поступает сигнал логической "1", такой же сигнал будет присутствовать и на его втором входе, т.к. элемент НЕ 4.2 инвертирует "0" с выхода счетчика 4.6 в "1". Т.о., на входе данных магистрального элемента 4.6 будет "1", что свидетельствует о наличии СКК в анализируемом сигнале. Одновременно на выходе данных реверсивного счетчика 4.7 присутствует значение размера окна, соответствующего длине памяти помехоустойчивого сверточного кодера. Сигнал логической "1" с выхода элемента 2И 4.3 открывает элемент 3ИЛИ 4.5 и формирует сигнал, переводящий устройство в исходное состояние. Произойдет запись новых реализаций в блок памяти и их анализ. При тактовой частоте 1 МГц на цикл полного анализа потребуется не более 0,5 секунды.

Таким образом, предлагаемое устройство полностью реализует способ распознавания классов сигналов, применяющих СКК с решетчатым кодированием, и кроме того определяет длину памяти кодера.

Источники информации.

1. Гоноровский И.С. Радиотехнические цепи и сигналы. М.: Советское радио, 1977, 671 с.

2. А.С. СССР N 1304045 A2, кл. G 06 K 9/00, от 15.04.87.

3. А.С. СССР N 1667117 A2, кл. 5 G 06 K 9/00, от 10.05.89 (прототип).

4. А.С. СССР N 1317463 A2, кл. G 06 K 9/00, от 26.03.85.

5. Справочник. Цифровые интегральные микросхемы.- М.: Радио и связь, 1994 г.

6. CCITT Study Group XVII, "Recomendation V.32 for a fammily of 2-wire, duplex modems operating at data signalling rates of up to 96 bit/s for use on the general switched telephone network and on leased telephone-type circuits", Document AP VII-43-E, May 1984.

7. CCITT Study Group XVII, "Draft recomendation V.33 for 144 bits per second modem standardized for use on point to-point 4-wire leased telephonetype circuits, " Circular 12, СОМ XVII/YS, Geneva, Switzerland, May 17, 1985.

8. G. Ungerboeck, "Channel coding with multilevel/phase signals", IEEE Trans. Inform. Theory, vol. IT-28, pp. 55-67, Jan. 1982.

9. G. Ungerboeck, "Channel coding with mulilevel/phase signals", IEEE Trans. Inform. Theory, vol. IT-28, pp. 55-67, Jan. 1982. 8. G. Ungerboeck, "Trellis-coded modulation with redundant signal sets: Parts I and II," IEEE Commun. Mag., vol., pp. 5-21, Feb. 1987.

10. В. И. Шляпоберский, "Основы техники передачи дискретных сообщений" -М: "Связь", 1973.

11. Б. В. Тарабрин, Справочник. Интегральные микросхемы.- М.: Радио и связь, 1984.

12. G. Zou and H. Weinrichter, "Structured trellis encoding," IEE Proceedings, vol. 137, pp. 335-344, Dec. 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ ПЕРЕДАЧ | 1995 |

|

RU2099786C1 |

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| СПОСОБ ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100812C1 |

Предлагаемые объекты изобретения, объединенные единым изобретательским замыслом, относятся к радиотехнике, а именно к автоматике и технической диагностике параметров сигналов, и могут быть использованы при построении распознающих автоматов для комплексов технического анализа и распознавания классов сигналов. Достигаемым техническим результатом изобретения является разработка способа и устройства распознавания классов сигналов, обеспечивающих возможность распознавания СКК с решетчатым кодированием и одновременно не усложняющих конструкцию устройства, его реализующего. Способ распознавания классов сигналов заключается в приеме Q реализаций сигнала, их запоминании и нахождении на основе обработки событий, называемых запрещенными, подсчете их общего числа S и сравнении вычисленного значения с заданным пороговым Sп, при выполнении условия S < Sп сигнал идентифицируют, как имеющий СКК с решетчатым кодированием. Устройство распознавания классов сигналов содержит блок формирования адресов 1, блок памяти 2, блок определения запрещенных событий 3, блок принятия решения 4. Блок 1 управляет запоминанием и считыванием принимаемых реализаций в блоке 2. Блок 2 запоминает реализации на время анализа и передает сформированные под управлением блока 1 две группы реализации в блок 3. Блок 3 выявляет запрещенные события путем сравнения этих двух групп реализаций, селекции вариантов, когда в паре групп только одна пара не совпадает и сравнении младших разрядов реализаций в этой паре. Блок 4 подсчитывает число запрещенных событий, управляет процессом анализа и принимает решение о наличии в сигнале СКК с решетчатым кодированием. 2 с. и 6 з.п. ф-лы, 9 ил.

γ = 1, 2, 3, ..., Q - (2К - 1),

после чего для каждой пары значений К и γ в первую группу включают реализации с номерами

j+(γ-1); j+1+(γ-1);...,(K-1)+j+(γ-1);

во вторую

а в i-е группы, где i = 3, 4, 5, ..., Q - 2 (К - 1), включают реализации с номерами:

3. Способ распознавания классов сигналов по п.1 или 2, отличающийся тем, что общее число Q принимаемых реализаций сигнала выбирают из условия Q > 100, а значения Kmin и Kmax выбирают в пределах Kmin = 2 ... 3, Kmax = 4, .. . 100, а пороговое значение числа несовпадений Sп выбирают в зависимости от качества канала связи в пределах Sп = 10 ... 1000.

| Устройство для распознавания N-мерных сигналов | 1989 |

|

SU1667117A1 |

| Устройство для распознавания радиосигналов | 1985 |

|

SU1304045A2 |

| US 4177448 A, 04.12.79 | |||

| Устройство для исследования нефтяных скважин | 1974 |

|

SU685814A1 |

Авторы

Даты

1999-07-20—Публикация

1998-02-04—Подача