ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне | 1990 |

|

SU1758632A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ИНТЕГРАЛЬНОГО ПОКАЗАТЕЛЯ | 2017 |

|

RU2661749C1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

Изобретение относится к вычислительной технике и может быть использовано в спектральных анализаторах, в устройствах преобразования координат. Цель изобретения - сокращение количества оборудования. Устройство содержит два квадратора, сумматор и блок извлечения корня, а также тактовый генератор и делитель частоты, причем каждый квадратор содержит схему сравнения, счетчик, сумматор, регистр, два элемента И, элемент задержки и триггер, а блок извлечения корня содержит схему сравнения, счетчик, сумматор, регистр, элементы И, ИЛИ, задержки, триггер и делитель частоты. 1 ил.

Изобретение относится к вычислительной технике и может быть использовано в спектральных анализаторах, устройствах преобразования координат и т.д.

Известно устройство для вычисления полярных координат вектора, выполняющее функцию х2+ у2, содержащее подключённые к входам устройства первый и второй блоки определения модуля, п сумматоров с подключенными к выходу каждого из них масштабирующими усилителями, п-1 блоков выбора максимума, при этом первые входы первого сумматора и первого блока максимума подключены к выходу первого блока определения модуля, а их вторые входы - к выходу второго блока определения модуля, первые входы каждого последующего сумматора и блока выбора максимума соединены с выходом предыдущего по номеру масштабирующего элемента, их вторые входы подключены к выходу предыдущего блока выбора максимума, дополнительно содержащее дешифратор, блок определения квадранта, блок сравнения знаков, п компараторов и п элементов ЭКВИВАЛЕНТНОСТЬ, каждый из которых первым входом соединен с выходом соответствующего компаратора, первый и второй входы каждого компаратора соединены с одноименными входами соответствующего сумматора, первый и второй входы блока определения квадранта и блока сравнения знаков подключены к соответствующим входам устройства, второй вход первого элемента ЭКВИВАЛЕНТНОСТЬ соединен с выходом блока сравнения знаков, вторые входы каждого последующего элемента ЭКВИВАЛЕНТНОСТЬ соединены с выходами предыдущего элемента ЭКВИВАЛЕНТНОСТЬ, выходы первого, второго и третьего

XI

ю ел

hO

l

разрядов блока определения квадранта, а также выходы всех элементов ЭКВИВАЛЕНТНОСТЬ подключены к соответствующим входам дешифратора.

Недостатком устройства является низ- кая точность.

Наиболее близким по технической сущности к заявляемому является устройство, содержащее два квадратора, сумматор, регистр, блок извлечения корня и выходной регистр, причем входами устройства являются входы квадраторов, выходы которых подключены к сумматору, выход которого соединен с регистром, выход которого соединен с входом блока извлечения корня, выход которого соединен с выходным регистром.

Недостатком известного устройства является сложность конструкции квадраторов и блока извлечения корня.

Цель изобретения - сокращение количества оборудования.

Указанная цель достигается тем, что в устройство для вычисления модуля полярных координат вектора, содержащее два квадратора, сумматор и блок извлечения корня, введены последовательно включенные тактовый генератор и делитель частоты, являющиеся источником тактовых частот, каждый квадратор содержит схему сравне- ния, счетчик, сумматор, регистр, два элемента И, элемент задержки и триггер, причем выход схемы сравнения соединен с R-входом триггера, выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен со счетным входом счетчика, выход которого соединен с первыми входами схемы сравнения и сумматора, выход которого соединен с информационным входом реги- стра, выход которого соединен с вторым входом сумматора и выходом квадратора, информационный вход которого соединен с вторым входом схемы сравнения, а управляющий вход-суправляющим входом устрой- ства и с S-входом триггера, входом обнуления счетчика и управляющим входом регистра, выход второго элемента И через элемент задержки соединен с тактовым входом регистра, вторые входы первого и вто- рого элементов И соединены с соответствующими тактовыми входами квадратора, которые подключены соответственно к первому и второму частотным входам устройства, блок извлечения корня содержит схему сравнения, счетчик, сумматор, регистр, элементы И, ИЛИ, задержки, триггер и делитель частоты, причем первый вход схемы сравнения соединен с информационным входом блока, а первый, второй и

третий выходы соединены соответственно с первым и вторым входами элемента ИЛИ и S-входом триггера, R-вход которого соединен с выходом элемента ИЛИ, а выход - с первым входом элемента И, выход которого соединен с информационным входом делителя частоты и счетным входом счетчика, выход которого соединен с выходом блока и первым входом сумматора, выход которого соединен с информационным входом регистра, выход которого соединен с вторыми входами сумматора и схемы сравнения, выход делителя частоты через элемент задержки соединен с тактовым входом регистра, управляющий вход которого соединен с входами обнуления счетчика и делителя частоты и управляющими входами блока, который подключен к управляющему входу устройства, второй выход элемента И соединен с тактовым входом блока, который подключен к первому частотному входу устройства, выход тактового генератора является первым тактовым выходом, подключен к делителю частоты, выход которого является источником второй тактовой частоты.

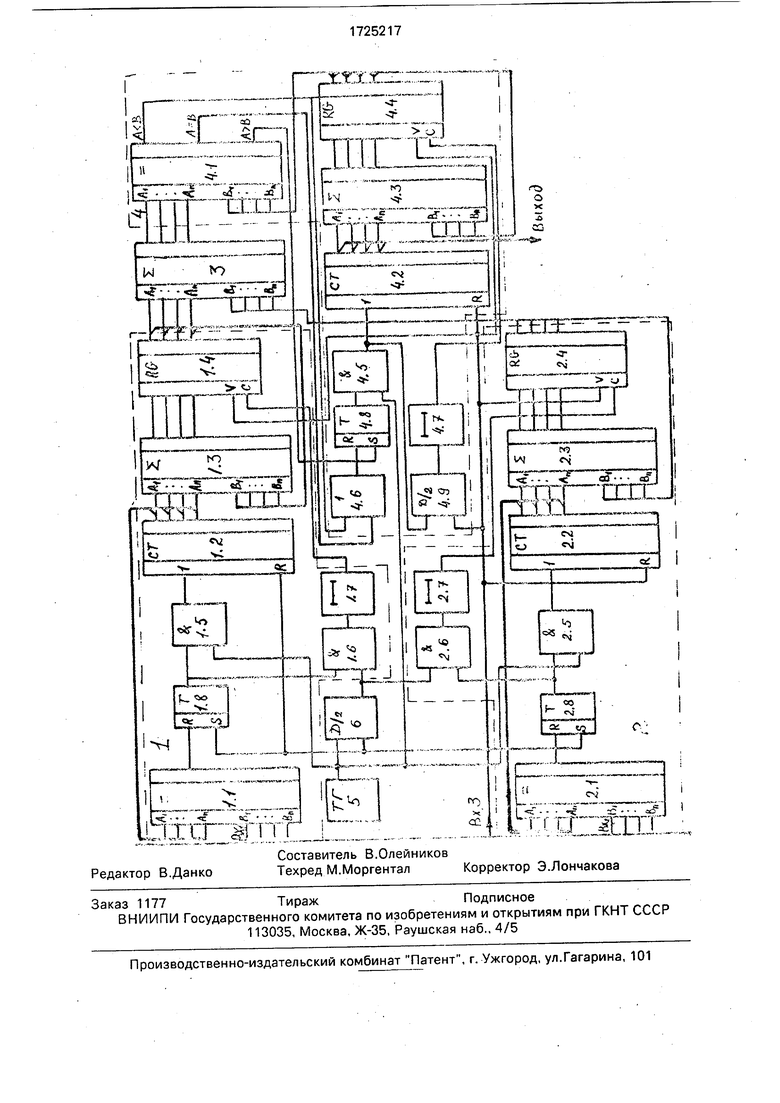

На чертеже представлена блок-схема устройства для вычисления модуля полярных координат вектора.

Устройство содержит квадраторы 1, 2, сумматор 3, блок 4 извлечения корня, тактовый генератор 5, первый делитель 6 частоты, причем информационные входы квадратора 1 и 2 соединены соответственно с первым и вторым входами устройства, а выходы - с входами сумматора 3, выход которого подключен к входу блока 4 извлечения корня, выход которого соединен с выходом устройства, квадратор 1 содержит схему 1,1 сравнения, счетчик 1.2, сумматор 1.3, регистр 1.4, элементы И 1.5, 1.6, элемент 1.7 задержки, триггер 1.8, причем выход схемы 1.1 сравнения соединен с R-входом триггера 1.8, выход которого соединен с первыми входами элементов И 1.5,1.6, выход элемента 1.5 - со счетным входом счетчика 1,2, выход которого соединен с первыми входами схемы 1.1 сравнения и сумматора 1.3, выход которого соединен с информационным входом регистра 1.4, выход которого соединен с вторым входом сумматора 1.3 и выходом квадратора 1, информационный вход которого соединен с вторым входом схемы 1.1 сравнения, а управляющий вход- с управляющим входом устройства и с S- входом триггера 1.8, входом обнуления счетчика 1,2 и управляющим входом регистра 1.8, выход элемента И 1.6 через элемент 1.7 задержки соединен с тактовым входом регистра 1.4, вторые входы элементов И 1.5, 1.6 соединены с соответствующими тактовыми входами квадратора 1, которые подключены соответственно к первому и второму частотным входам устройства, блок 4 извлечения корня содержит схему 4.1 сравнения, счетчик 4.2, сумматор 4.3, регистр 4.4, элемент И 4.5, элемент ИЛИ 4.6, элемент 4.7 задержки, триггер 4.8, второй делитель 4.9 частоты, причем первый вход схемы 4.1 сравнения соединен с информационным входом блока, а первый, второй и третий выходы соединены соответственно с первым и вторым входами элемента ИЛИ 4.6 и S-входом триггера 4.8, R-вход которого соединен с выходом элемента ИЛИ 4.6, а выход - с первым входом элемента И 4,5, выход которого соединен с информационными входами второго делителя 4.9 частоты и счетным входом счетчика 4.2, выход которого соединен с выходом блока и первым входом сумматора 4.3, выход которого соединен с информационным входом регистра 4.4, выход которого соединен с вторыми входами сумматора 4.3 и схемы 4.1 сравнения, выход делителя 4.9 частоты через элемент 4.7 задержки соединен с тактовым входом регистра 4.4, управляющий вход которого соединен с входами обнуления счетчика 4.2 и делителей 6, 4.9 частоты и к управляющим входам блока, который подключен к управляющему входу устройства, второй вход элемента И 4.5 соединен с тактовым входом блока, который подключен к первому частотному входу устройства, выход тактового генератора 5 является первым тактовым выходом, подключен к делителю 6 частоты, выход которого является источником второй тактовой частоты.

Устройство работает следующим образом.

Коды, соответствующие полярным векторам X, Y, поступают на входы первого и второго квадраторов, являющиеся первым и вторым входами устройства. В момент поступления короткого импульса разрешения преобразования кодов на третий вход устройства обнуляются счетчики 1.2. 2.2, 4.2, делители 6, 4.9 частоты и регистры 1.4, 2.4,

Рассмотрим операцию возведения в квадрат на примере возведения в квадратX. Сумматор 1.3 выполняет операцию А + В, поэтому при поступлении первого импульса, задержанного на время переходного процесса счетчика 1.2 и сумматора 9, на вход записи регистра 1.4 в него заносят код, равный 1+0, так как и счетчик 1.2 и регистр

0 трем, а на второй вход сумматора 1.3 - код регистра 1.4, соответствующий единице, таким образом будет зарегистрирован код, соответствующий четырем. При поступлении третьего импульса на вход записи регистра

5 1.4 на входы сумматора 1.3 поступит код счетчика 1.2, соответствующий пяти, и код регистра 1.4, соответствующий четырем. Таким образом, в регистре 1.4 по фронту третьего импульса будет занесен код, равный

0 девяти, и т.д. до тех пор, пока код счетчика 1.2, сдвинутый в сторону уменьшения на один разряд за счет сдвинутой распайки проводов, не сравняется с кодом числа X в схеме сравнения 1.1.

5 Так как с помощью делителя 6 частоты получаем передние фронты импульсов, соответствующие 1, 3, 5 и т.д. нечетным импульсам счетчика 1.2, а для получения числа в счетчике 1.2, соответствующего удвоенно0 му числу импульсов 1, 2,3, 4, 5 и т.д. необходимо, чтобы код счетчика был четным, т.е. 2, 4, 6, 8 и т.д. для этого необходимо добавить в счетчик еще один импульс для сравнения кодов.

5 Аналогичным образом работает и канал возведения в квадрат Y. Полученные коды суммируются сумматором 3 и поступают на вход блока извлечения корня или на вход схемы 4.1 сравнения, который управляет

0 триггером 4.8. В том случае, когда код сумматора 3 окажется больше кода регистра 4.4. на S-вход триггера 4.8, разрешающего своим выходным потенциалом прохождение через элемент И 4.5 импульсов тактово5 го генератора 5 на счетный вход счетчика 4.2, проходит сигнал с выхода А В. Если код регистра 4.4 окажется равным или большим кода сумматора 3, то на выходах или А В схемы 4.1 сравнения появится

0 потенциал, поступающий на R-вход триггера 4.8, который закроет своим выходным потенциалом счетный вход счетчика 4.2.

Схема, состоящая из элемента И 4.5, счетчика 4.2, сумматора 4.3. регистра 4.4,

5 второго делителя 4.9 частоты, работает аналогично схеме возведения в квадрат. Отличие заключается в том, что схемой 4.1 сравнения сравниваются входной код не с текущим кодом счетчика 4.2, а с кодом регистра 4.4, соответствующим квадрату числа

выходных импульсов. Поэтому при сравнении кодов в схеме 4.1 сравнения на выходе счетчика 4.2 получаем код 2А, где А - выходной код регистра 4.4. С той целью, чтобы на выходе счетчика 4.2 получить код. равный А, сдвигают выходные коммутирующие контакты счетчика 4.2 на разряд в сторону уменьшения.

Формулаизобретения

Устройство для вычисления модуля вектора полярных координат, содержащее два квадратора, сумматор и блок извлечения корня, причем информационные входы первого и второго квадраторов соединены соот- ветственно с первым и вторым входами устройства, а выходы - с входами сумматора, выход которого подключен к входу блока извлечения корня, выход которого соединен с выходом устройства, отличающееся тем. что, с целью сокращения количества оборудования, каждый квадратор содержит схему сравнения, счетчик, сумматор, регистр, два элемента И. элемент задержки и триггер, причем выход схемы сравнения со- единен с R-входом триггера, выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен со счетным входом счетчика, выход которого соединен с первыми входа- ми схемы сравнения и сумматора, выход которого соединен с информационным входом регистра, выход которого соединен с вторым входом сумматора и выходом квадратора, информационный вход которого со- единен с вторым входом схемы сравнения, а управляющий вход - с управляющим входом устройства и с S-входом триггера, входом обнуления счетчика и управляющим входом регистра, выход второго элемента И через элемент задержки соединен с тактовым входом регистра, вторые входы первого и второго элементов И соединены с соответствующими тактовыми входами квадратора, которые подключены соответственно к первому и второму частотным входам устройства, блок извлечения корня содержит схему сравнения, счетчик, сумматор, регистр, элементы И, ИЛИ, задержки, триггер и делитель частоты, причем первый вход схемы сравнения соединен с информационным входом блока, а первый, второй и третий выходы соединены соответственно с первым и вторым входами элемента ИЛИ и S- входом триггера, R-вход которого соединен с выходом элемента ИЛ.И, а выход - с первым входом элемента И, выход которого соединен с информационным входом делителя частоты и счетным входом счетчика, выход которого соединен с выходом блока и первым входом сумматора, выход которого соединен с информационным входом регистра, выход которого соединен с вторыми входами сумматора и схемы сравнения, выход делителя частоты через элемент задержки соединен с тактовым входом регистра, управляющий вход которого соединен с входами обнуления счетчика и делителя частоты и с управляющим входом блока, который подключен к управляющему входу устройства, второй вход элемента И соединен с тактовым входом блока, который подключен к первому частотному входу устройства.

til3i cz;:r™::

| Авторское свидетельство СССР № 762012, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения мыла | 1920 |

|

SU364A1 |

Авторы

Даты

1992-04-07—Публикация

1989-12-05—Подача