(54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1978 |

|

SU748477A1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| ВСЕСОЮЗНАЯ 1 | 1972 |

|

SU328497A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1365353A2 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1113830A2 |

| Преобразователь угловых перемещений в код | 1976 |

|

SU641480A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1347186A1 |

| Многоканальный преобразователь угла поворота вала в код | 1980 |

|

SU947895A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационно-из мерительных системах для построения аналого-цифровых преобразователей . (АЦП) угловых перемещений входного вала, связанного с контролируемым объектом. Известны устройства, содержащие синусно-косинусный вращающийся транс форматор (СКВТ), обмотка возбуждения которого подключена к шине питания, а синусная и косинусная обмотки чере два Преобразователя напряжение-код и коммутатор - к одному из входов преобразователя кода и логического блока, и блок определения квадранта угла поворота, входы которого подклю чены к обмоткам СКВТ, а выход - к др гому входу логического блока, выходы которого непосредственно и через, блок констант, кратных 45 соединены с другими входами преобразователя ко да, выход которого является вых:од 1 устройства СО I Недостаток данного устройства - сложность конструкции, обусловленная наличием двух преобразователей напряжение-код, и невысокая точность из-за : нелинейности характеристики преобразования датчика углового положения (сквт)... Известно такясе устройство, содержащее СКВТ, обмотка возбуждения которого подключена к шине питания, выходные синусные и косинусная обмотки через последовательно соединенвые двухиозиционный переключатель, преобразователь напряжение-код и блок передачи кода - к одному из входов блока сложения кодов, выход которого является выходом устройства, и селектор октанта, входы которого подключен ны к noHtie питания и выходным обмоткам СКВТ, а выходы - к управляющим вход двухпоаициоиного переключателя и блока передачи кода непосредстенно и к другому входу блока сложеия кодов через блок констант, кратых 45° 2J. ,

Недостаток такого устройства - неысокая точность, обусловленная порешностью аппроксимации синусоидальой характеристики преобразования КВТ (отрезком прямой линии) на ее начальном 45-градусном участке, прилегакщем к угловой оси. Ю

. Наиболее близким к предложенному является устройство, содержащее синусно-косинусный датчик угла (СК,ТУ) , оботка возбуждения которого подключена к источнику напряжения питания, а 15 синусная и косинусная обмотки через селектор октанта - ко входам вычитатёля непосредственно и через первый . блок масштабирования, фазовый детекTdif), входы которого подключены к си- 20 нусной обмотке СКДУ и выходу вычитатеяя, а выходы - ко входу счетчика и к управляющему входу преобразователя напряжение-код, второй блок масштабирования, вход которого подключен к 25 выходу вычитателя, а выход -.ко входу преобразователя напряжение-код, и блок управления, выходы которого соединены с управляющими входами обоих блоков масштабирования 13J.30

Недостаток этого устройства - невысокая точность, обусловленная нелинейностью кодируемого напряжения в выбранном селекторе д 0 угловой оси.35

Цель изобретения--повышение точности преобразователя угла поворота вала в код.

Поставленная цель достигается тем, что в преобразователь угла поворота о вала в код., содержащий синусно-косинусный вращаищийся трансформатор, обмотка возбуждения которого подключена к источнику. Питания, а синусная и косинусная обмотки соединены со вхо-45 дами селектора октантов, три выхода которого соединены с вьпсодньми клеммами преобразователя, четвертый выход - с пврвьм входом блока вычитания, а пятый выход соединен через пер-,., вый блок масштабирования со вторым входом блока вычитания, выход которого соединен с первым входом фазового дискриминатора и через второй блок масштабирования - со входом „ преобразователя напряжение-код, синусная обмотка синусно-косинусного вращающегося трансформатора соединена со вторым входом фазового дискриминатора, первый выход которого соединен со входом счетчика, выходы блока управления соединены с управляющими входами первого и второго блоков масштабирования, введены регистр, блок сравнения кодов, блок передачи кода, блок выдачи кода, элементы задержки, элементы И и элементы ИЛИ, первый выход фазового дискриминатора соединен с первым входом первого элемента И, второй выход фазового дискриминатора соединен спервьм выходом второго эле мента И, первый и второй в.ыход преобразователя напряжение-код соединены со в-т.орыми входами первого и второго элементов И соответстве-нно, информационные выходы преобразователя напряжение-код соединены .с первыми ,информационньй и входами блока сравнения и с информационными входами блока передачи кода, выходы которого соединены через регистрсо вторыми информационными входами блока сравнения кодов и через блок вьщачи кодов - с выходными клеммами преобразователя, выход второго элемента И соединен со входом блока сравнения кодов, первый выход которого соединен с первыми входами первого и второго элементов ИЛИ, а второй выход соединен через первый элемент задержки с первым управляющим входом блока передачи кода, выход первого элемента задержки соединен через второй элемент задержки со вторым входом первого элемента ИЛИ, вькгод которого соединен с управляющим входом блока вьщачи кода, выход первого элемента И соединен со вторым входом второго элемента ИЛИ, а через третий элемент задержки - со вторым управляющим входом блока передачи кода, выход второго элемента ИЛИ соединен с управляющим входом регистра.

I

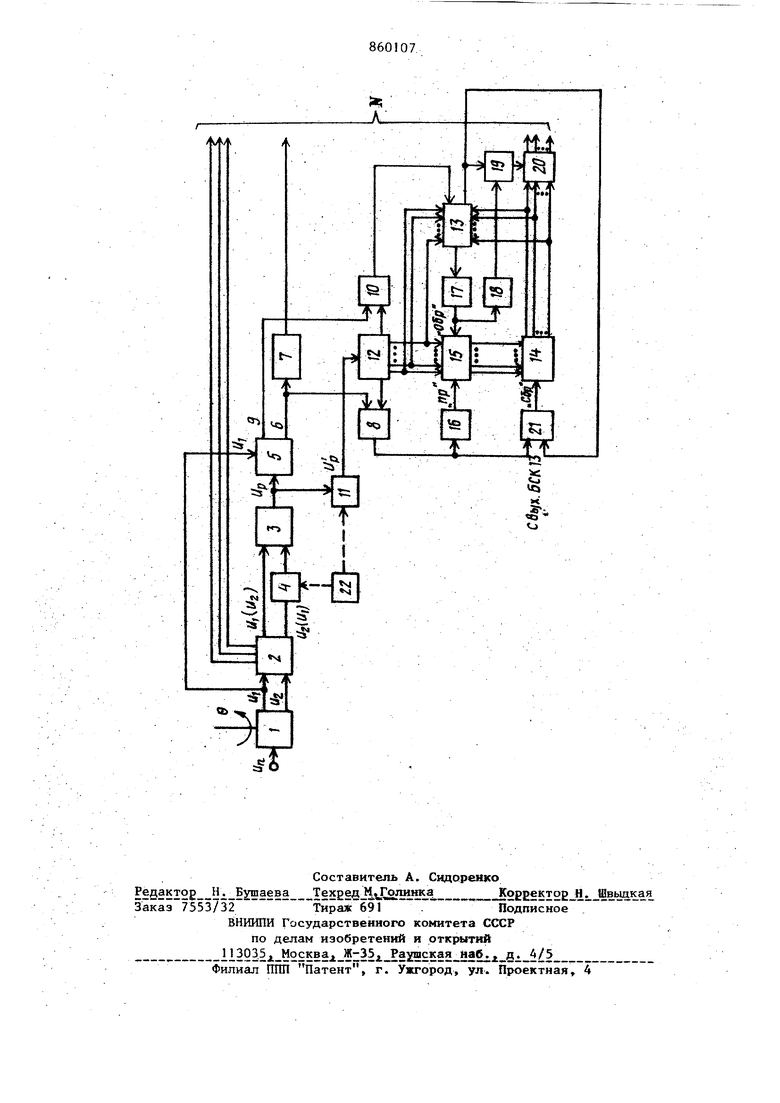

Сущность изобретения заключается в том, что в любом секторе Дв изменения угла поворота 0 вала в г-том такте осущесгвляется преобразование в код напряжения Vp и перенос результата N0;} преобразования в регистр, а в J-TOM такте - аналогичная операция для напряжения Vpj (знак фазы огибающей которого изменяется в точке угловой оси, сдвинутой относительно Vpl на л9 ), причем результат Npj преобразования в те;кущем такте при условии протИвофазности напряжений Vpj и V, сравнивается с Np, а по результатам сравнения выбирается и считывает ся (через блок выдачи кода) меньший из них: NP, (в первом полусектрре, а форме прямого кода) или Npj (во втором полусекторе, в форме обратног кода). На чертеже показана структурная схема.предложенного устройства. Преобразователь угла поворота вал в код содержит СКВТ.1 , обмотка возбуждения которого подключена к источнику напряжения V, питания (на схеме не показан), а синусная и коси нусная обмотки через селектор 2 октанта - ко .входам блока 3 вычитания непосредственно и через блок 4 масшт бирования, фазовый дискриминатор .5, входы которого подключены к синусной обмотке GKBT 1 и выходу блока 3, пер вый выход 6 - ко.входу счетчика 7 и к одному из входов элемента И 8, а второй выход 9 - к одному из входов элемента И 10, блок П масштабирова.ния, вход которого подключен к вькоду блока 3 вычитания, а выход - ко входу преобразователя 12 напряжениекод, выходы разрядов которого соединены с первыми входами блока 13 срав нения кодов непосредственно и со вхо дзми разрядов регистра 14 через блок 15 передачи .кода, а его управля Ю1ЦИЙ выход Окончание преобразования с другим входом элементов И 8 и 10, вьг-ода 1 которых подключены соответственно к первому управляющему входу блока передачи кода через элемент 16 задержки и ко второму управляющему входу того же блока через последовательно соединенные блок 13 сравнения кодов и элемент 17 задержки, элемент 18 задержки, вход которого соединен с выходом элемента 17 задержки, а выход - с одним из входов элемента ИЛИ 19, другой вход которого подключен ко второму выходу блока 13 срашнения кодов, а выход - к управля щему входу блока 20 выдачи кода, эле мент ИЛИ 21, входы которого подключе ны .к выходу элемента И 8 и первому выходу блока 13 сравнения кодов, а выход - ко входу Сброс регистра 14 выходы разрядов которого соединены со вторыми входами блока 13 сравнения кодов и входами блока 20 вьщачв кода выход которого является выходом устройства, и блок 22 управления, которого соединены с управляющими входами обоих блоков 4 и 11 масштабирования. Преобразователь работает следукяи-т образом. Выходные напряжения СКВТ t, как известно, определяются но формуле V kV inwtsJn0«V;pSfn0 , (l) Va kV inwtcos0 , (2) где V ,w - амплитудное значение и круговая частота напряжения УП ПИТ9ИИЯ СКВТ; коэффициент трансформации СКВТ и угол поворота его ротора, механически связанного с входным валом: /i k . По результатам анализа знака фазы (относительно напряжения Vy) и соотношения амплитуд этих напряжений селектор 2 октанта формирует код Ng три старших разряда выходного п-разрядного результирующего кода N - и подключает выходные обмотки СКВТ I ко входам блока; 3 вычитания непосредственно и через блок 4 масштабирования , еост Чящий из ключей и делйтеЛ(Й4 напряжения. Однако в первом такте преобразования ни один из ключей блока 4 пока не задействован, и поэтому на входы блока 3 вычитания поступает только одно из выходных напряжений екДУ, например V , если угол поворота 9 находится в первом октанте (вся дальнейшая последовательность ontipaций рассматривается применительно к этому октанту, для остальных октайt fB процесс преобразования протекает аналогично - меняется только очередность срабатывания юяочей в блоках 4 и )1 масштабирования), а с его выхода снимается напряжение Vp-,, рйв- Ное, очевидно, V. , так как косинусмая обмотка СКВТ I, как было уже сказано, отключена в первом такте от блока 3 вычитания. Это напряжение пода тся: а) на фазовый дискримяна- ; ТОР 5, который определяет знак его фазы (относительно опорного напряжеНИИ, в качестве которого вьйирается V. ) и синфазности Xija-f и ставит в соответствие логический сигнал 1 на выходе 6, а противофазности, в обем случае, логический сигнал 1 на выходе 9),. ) на преобразователь 12 напряжеинеод через блок М масштабирования, котором по сигналу блока 22 управения ё первом такте замкнут соотетствующий (первый в пот)ядке срабаыдания) ключ. Преобразователь 12

формирует код, отображающий значение поданного на его вход напряжения Vp V, и (в момент времени, соответствующий окончанию цикла преобразования в нем) импульсный сигнал Раз решение переноса, который (при наличии логического сигнала 1, т.е. потенциала высокого уровня, на выходе 6 фазового дискриминатора 5) проходит через элемент И 8 и, во-первых, сбрасывает регистр 14 в нуль, пройдя через элемент ИЛИ 21, во-вторых, разрешает перенос результата Np-,преобразования напряжения Vp., в форме прямого кода в регистр 14 через блок 15 Передачи коди, пройдя на один из его управляющих входов через элемент 16 задержки (который необходим, чтобы сдвинуть момент переноса кода в регистр относительно момента сброса регистра, т.е. сперва сбросить регистр, а потом записать в него код с выхода преобразователя 12), После этого схема устройства готова к следующему такту преобразования.

Во втором такте по сигналу блока 22 управления в блоке 4 масштабирования замкнут первый (в порядке срабатывания) ключ, осуществляющий функцию подключения ко второму входу блока 3 вычитания на первый, как и прежде, подается U) напряжения V,j косинусной Ьбмотки СКВТ 1 через первый делитель напряжения с коэффициентом деления tgdx, . На выходе блока 3 вычитаимя образуется напряжение 1р„ огибающая которого описьгоается уравнением вида .

, -KV,i K;,Vi,sin(9 -в),(3

™- - ,

Это напряжение подается на фазовый дискриминатор 5, который определяет знак его фазы относительно V , и на преобразователь 12 напряжение-код через блок 11 масштабирования, в котором указанный сигнал блока 22 упразднения замыкает второй ключ и пропускает N;,, через первый делитель напряжения с коэф4ящиентом деления К,. Ре зультат Мр1преобразования напряжения

vn,

(в -а-,) (4)

IIIII

при наличии логического сигнала па выходе 6 фазового дискриминатора 5fТ.е. при условии сиифазности напряжеШ1Й iLjи V., в форме прямого кода переносится в регистр 14 (через блок 15 передата кода) так же, как и в пер-

вом такте. После этого схема устройства готова к слёдукицему такту преобразования.

В общем случае в -том такте по сигналу блока 22 управления в блоке 4 масштабирования замкнут (-1)-ый ключ осуществляющий функцию подключения ко второму входу блока 3 вычитания напряжения VQ через соответствующий (1-1)-ый делитель напряжения с коэффициентом деления К . На выходе вычитателя образуется напряжение L, огибакдцая которого описьгаается уравнением вида

. Vp K|-Xsfn(0 -6i-i),(5)

« ir,

Это напряжение подается на фазовый дискршданатор 5, который определяет знак его фазы относительно I , и через блок II масштабирования, в котором указанный сигнал блока 22 управления зa шкaeт |-ый ключ и пропускает VP,- через ()-ый делитель напряжения с коэффициентом деления Kj-j, на преобразователь 12, который преобразует его в код. Результат Np преобразования напряжения

vi- (9 -9 (6)

при наличии логического сигнала на выходе 6 фазового дискриминатора 5 переносится далее в регистр 14 через блок 15 передачи кода в форме прямого кода. На этом f-ый такт преобразования заканчивается.

Процесс формирования напряжений вида (5) продолжается до тех пор, пока одно из них (допустим, напряжение РЛ J i не окажется в противофазе с напряжением V , что фиксируется фазовьм дискриминатором 5, логический сигнал 1 на выходе 9 которого подготавливает логический элеMfHT И 10. Преобразователь 12, как обычно, преобразует Ц)3 в код, и в момент времени, соответствующий окончанию цикла преобразования, выдает сигнал Разрешение переноса, который через открытый элемент И 10 проходит на управлякнцйй вход блока 13 сравнения кодов, включая его в режим сравнения кодов Npj и Мр(код NP,- результат преобразования предыдущего такта - хранится в регистре 14) и (в зависимости от результатов этого сравнения) определяя следующую последовательность операций. 98 Если N,. Npj, то сигнал с первого выхода блока 13, появление которого соответствует выполнению этого условия, во-первых, сбрасьшает регистр 1 в нуль через элемент ИЛИ 21, во-вторых, разрешает перенос результата No преобразования .текущего такта {в фор ме обратного кода) в очищенный регистр через блок 15 передачи кода, пройдя на соответствзпощий управляющий вход последнего через элемент 17 задержки, и, в-третьих, разрешает считьшание кода hL-, записанного э регистр 14, через блок 20 вьщачи кода, пройдя на управлякщий вход последнего через элемент 18 задержки (с выхода элемента 17 аналогичного назначения) и элемент ИЖ 19. Таким образом, сперва регистр 14 очищается, затем в него заносится код Npj, и далее этот код считывается через блок 20. Чтобы разнести перечислен ные операции во времени, использованы элементы 17 и 18 задержки. Если, наоборот, Npj, то сигна со второго выхода блока 13, появлени которого соответствует выполнению этого условия, проходит через логический элемент ИЛИ 19 на управляклций вход блока 20 вьщачи кода, разрешая считывание содержимого регистра 14, т.е. результата Мр- предьщущего такта преобразования. Выполнение операций сравнения кодов и и выбор меньшего из них по результатам сравнения равносильно делению сектора а© , в пределах ко торого в известном устройстве кодируется напряжение V, после выполнения условия противофаэности напряжеНИИ pj и V , пополам и вчцелению пол секторов, в одном из которых за конечный результат преобразования принимается результат Мр:преобразования напряжения в J-OM такте, но тепер уже в пределахйвД, т.е. на пркпега няцем к угловой оси начальном участке синусоиды, который, очевидно, про порционально уменьшается с уменьшением и, значит, с большей степенью приближения аппроксимируется .пинейной зависимостью, при этом Np,j Np и itp результат преобразования напряжения Vp.- в 1-ом предыдущем такте - сбр сывается, а в другом Np{ отображает значение Vp; в пределах (т.е. на начальном участке синусоиды той же 7 длины, что и в предыдущем случае) ,: при Npj Npj считьгоается Np , а Npj используется только с целью сравнения с Np в блоке 13. Считывание (Npp в форме прямого (обратного) кода определяется характером изменения кодируемого напряжения Vp|() в пределах полусектора (с увеличением О значения U,; увеличиваются, а Vpj - уменьшаются). Код сектора Д0 формируется в счетчике 7 путем подсчета логических сигналов (кроме первого) с выхода 6 фазового дискриминатора 5 и р его разрядов составляет соответственно р разрядов выходного п-разрядного результи рующего кода N. Код пгпусектора формируется блоком 13 по результатам сравнения кодов Npj и Np , и один его разряд (не показан) определяет непосредственно состояние соответствующего разряда кода N. Код угла поворота 9 в пределах полусектора формируется преобразователем 12, записывается в регистр 14 и считывается через блок 20. причем г его разрядов образуют соответственно г нладших разрядов кода N. Таким образом, с учетом 3-х разрядов кода октанта п - р + г + 4 (7) Рассмотрим конкретный пример, иллюстрирующий р.аботу предложенного устройства для двух значений угла поворота вала: ЗО и 24°. 0 30 П .е р в ы и т а к т: а) косинусная обмотка СКВТ 1 отк.гаочена от блока 3 вычитания, на который подается только напряжение б) с выхода блока 3 вычитания снимается напряжение Vp V; синфазности напряжений и Vx, ставится в соответствие лохический сигнал I на выходе 6 фазового дискриминатора 5, который п дгртав.гш элемент И 8 для прохождения сигпала. Разрежение переноса с выхода Окончание преобразования преобразователя 12; в) с блока 11 масштабирования снимается напряжение Vp V , которое преобразуется в код тфеобразователем 12, а результат преобразоания { переписывается в регистр 14 ерез блок 15 в форме прямого кода. Второй такт: а) на блок 3 ычитания подаются напряжение V неосредственно и напряжение с выода блока 4 масштабирования, в котором замкнут первый ключ .и задействован первый делитель напряжения с ,коэффициентом деления б) с выхода блока 3 вычитания снимается напряжение Jp вида VV к;у;,з1я(9-). Выберем Д9 11,25, как в извесч ном устройстве, чтобы удобнее было сравнивать полученные результаты, югда :0, И,25° К tg 11,25 0,199 1/cos 11,25° 1,02 Синфазности напряжений Vp,, и V ст вится га соответствие логический сигнал I на выходе 6 фазового дискриминатора 5; в) с выхода блока 11 масштабирования снимается напряжение VpQi Hil/K (0 -Ч25° Это напряжение преобразуется в код преобразователем 12, а результа Npn преобразования переписывается б регистр 14 в форме прямого кода (Np при этом сбрасывается). Т р е т и и т а к т: а) на блок вычитания подаются напряжение V., не посредственно и напряжение с в хода блока 4 масштабирования, в котором задействован второй делитель, напряжения с коэффициентом деления К б)с выхода блока 3 вычитания снимается напряжение вяйа . .V/i- KJ v4sin(P -93), 22,3 KI tg 22,5 0,4142; К 1/cos 22,5 1,082. Синфазности напряжений V ставится в соответствие логический сигнал 1 на выходе 6 фазового дис рюшнатора 5; в)с выхода блока И масштабирования снимается напряжение Лф вида Vi,e- VKa - 22,5) Это напряжение преобразуется в к Преобразователе 12, а результат jtp,f Hpfпреобразования переписывае ся в регистр 14 я форме прямого код ( этом сбрасывается). : Чет в е р т ы и та к т: aj н , блок 3 вычитания подаются напряжени Vf, непосредственно и напряжение с выхода блока 4 масштй&нровання с вкл1рченньм третьим дьлителй напряжения; )с выхода блока 3 вычитания снимается напряжение 1р вида Vp4. V К1у;„51п(в -Oj) где в 33,75°; Kj tg 33,75® 0,668; Kj 1/cos 33,75° 1,20 Противофазности напряжений V и U, ставится в соответствие логический сигнал 1 на выходе 9 фазового дискриминатора 5, который подготавливает элемент И 10 для прохозедення сигнала Разрешение переноса с соответствующе гр выхода преобразователя 12. в)с выхода блока 3 вычитания снимается напряжение VP4 вида 4 VK4 M;ism(0- 33,75) Это напряжение .преобразуется в код преобразователем 12, а результат преобразования Npj N сравнивается (сигнал с выхода элемента И 10 включает блок 13 сравнения кодов) с результатом Mp;j Np преобразования, полученным в предьщущем такте и хранящимся в регистре 14. Так как %4- РЗ ° ° должен быть считан, для этого сигнал с первого выхода блока 13, появление которого соответствует выполнению..указанного условия, во-первых, сбрасывает регистр .14 (т.е. результат Npj, в котором теперь уже нет необходимости), во-вторых, пройдя через элемент 17 задержки на управляющий вход блока 15, разрешает перенос в очищенный регистр 14 результата N преобразования в форме обратного кода и, в-третьих, пройдя через эпем5внт 18 задержки и элемент ИЛИ 19 на управляияций вход блока 20, разрешает считывание И На этом цикл измерения заканчивается. 24°. До образовавдя напряжения Урд на четиертдм такте преобразования и сравнения Np.cNpj блоком 13 последовательность операций для 9 24 аналогична рассмотренной ранее. Так как в данном случае Мр меньше Нрд, Tie. Npj Мр, он должен быть считан, для этого со второго выхода блока 13, появление которого соответствует выполнению указанного условия, проходит через элемент ИЛИ I9 на управляющий вход блока 20 вьщачи кода и разрешает считывание Ц, НРЭнящегося в регистре 14. На этом цикл измерения заканчивается. В известном устройстве для данно и любого другого угла в диапазоне 22,5-33,75 в качестве.конечного был бы использован результат Мр Np4 по следнего четвертого такта преобразования, отображающий значение на пряжения Урд с максимальной нелинейностью (в пределах Л9 П,25, т.е на прилегающем к этому сектору уг ловой оси начальном участке синусоиды) , равной 1%, а в предложенном устройстве-для данного угла {и углов, лежащих в первом полусекторе , от GI 22,5 до д 28,1) исполь зуется в качестве -конечного результ . Np я-предыдущего такта преобразования, отображающий значение напр Vp. с максимальной нёлинейност жения равной 0,( пределах угла Q 30° лежащих во и углов. втором полусекторе от 9д 28,1 до 9. 33,75) - результат Np Мрд текущего такта преобразования, отоб жающий значение напряжения рд с мак мальной нелинейностью того ке поряд что и в первом полусекторе. За счет уменьшения погрешности о нелинейности преобразуемого в код н пряжения /р точность предложенного устройства увеличивается (для рассмотренного конкретного примера - в 1,7 раза) . . Формула изобретения Преобразователь угла поворота вала в. код, содержащий синусно-косинусный вращающийся трансформатор, об мотка возбуждения которого подключен к источнику питания, а синусная и косинусная обмотки соединею. со входами селектора октантов, три выхода которого соединены с выходными клеммами преобразователя, четвертый выход - с первым входом блока вычитания , а пятый выход, соединен через первый блок масштабирования со вторым входом блока вычитания, выход ко торого соединен с первым входом фазо вого дискриминатора и через второй блок масштабирования - со входом преобразователя напряжение-код, синусная обмотка синусно-косинуснргб вращающегося трансформатора соедийена со вторьм входом фазового дискриминатора, первый выход которого соединен со входом счетчика, выходы блока управления соединены с управляюсцими входами первого и второго блоков масщтабирования, о т л и ч аю щ и и с я тем, что, с целью повышения точности преобразователя, в него введены регистр., блок сравнения кодов, блок передачи кода, блок вьщачи кода, элементы задержки, элементы И и элементы ИЛИ, первый выход фазового дискриминатора соединен с первьм входом первого элемента И, второй выход фазового дискриминатора соединен с первым выходом второго элемента И, и вто1юй выход преобразователя напряжение-код соединены со вторыми входами первого и второго элементов И соответственно, информационные выходы преобразователя напряжение-код, соединены с первыми информационными входами блока сравнения и с информационнымивходами передачи кода, выходы которого соединены через регистр со вторыми информационными входами блока сравнения кодов и через блок выдачи кодов с выходными клеммами преобразователя, выход второго элемента И соединен со входом блока сравнения кодов, первый выход которого соединен с первыми входами первого и второго элементов ИЛИ, а второй выход соединен через первый элемент задержки с первым управляющим входом блока передачи кода, выход первого элемента задержки со единен через второй элемент задержки со вторым входом элемента ИЛИ, выход которого соединен с управляющим блока выдачи кода, выход первого элемента .И соединен со вторыи входом второго элемента ШШ, а через третий элемент задержки - со вторым управляющим входом блока передачи кода, выход второго элемента ИЛИ соединен с управякщим входом регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 332488, кл. G 08 С 19/28, i970. 2.Авторское свидетельство СССР 591900, кл. 6 08 С 9/04, 1976, 3.Авторское свидетельство СССР 537370, кл. G 08 С 9/04, 1975 (проотип).

Авторы

Даты

1981-08-30—Публикация

1979-10-19—Подача