(54) УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ Изобретениеотносится к технике связи.и может &ыть использовано при построений аппаратуры передачи данных по каналам связи с ограниченной полосой пропускания по частоте. Известно устройство автоматической подстройки синхронной частоты, содержащее (N+1) фазовых детекторов первые входы которых объединены и являются входом устройства, последовательно включенные селектор-мультиплексор, управляющий элемент, управляемый генератор и N элементов задержки, причем выход управляемого генератора подктаочен к второму входу первого фазового детектора, а выход 1-ого (где i 1,...,N) элемента задержки - ко второму входу I+1-ого фазового детектора Щ. Однако известное устройство имеет невысокую точность подстройки синхронной частоты в условиях, когда плотность распределения фазы в момент ее отсчета имеет большую дисперсию, а сама фаза зависит от инфО1я 1ации, закодированной в предыдущих и последующих синфазных и квадра турных интерполирующих импульсах (СИИ И КИИ). Такая ситуация всегда, например, имеет место в случае исСИНХРОННОЙ ЧАСТОТЫ пользования сигналов с одновременными отсчетами (СОО), в частности, сигналов с эквидистантными отсчетами (СЭО), и сигналов с двумерными отсчетами (СДО). Цель изобретения - повышение точности подстройки синхронной частоты. Для достижения цели в устройство автоматической подстройки синхронной частоты, содержащем (N+1) фазовых .детекторов, первые входы которых объединены и являются входом устройства, последовательно включенные селектор-мультиплексор, управляющий элемент, управляемый генератор и N элементов задержки, причем выход управляемого генератора подключен к второму входу первого фазового детектора, а выход 1-ого (где , ...,N) элемента.задержки - к ,вто|рому входу t + 1-ого фазового детектора, между выходом каждого фазового детектбра и соответствующим входом селектора-мультиплексора включен дополнительный элемент задержки, а между входсм устройства и управляющим входом селектора-мультиплексора включены последовательно аналогоцифровой преобразователь и элемент памяти.

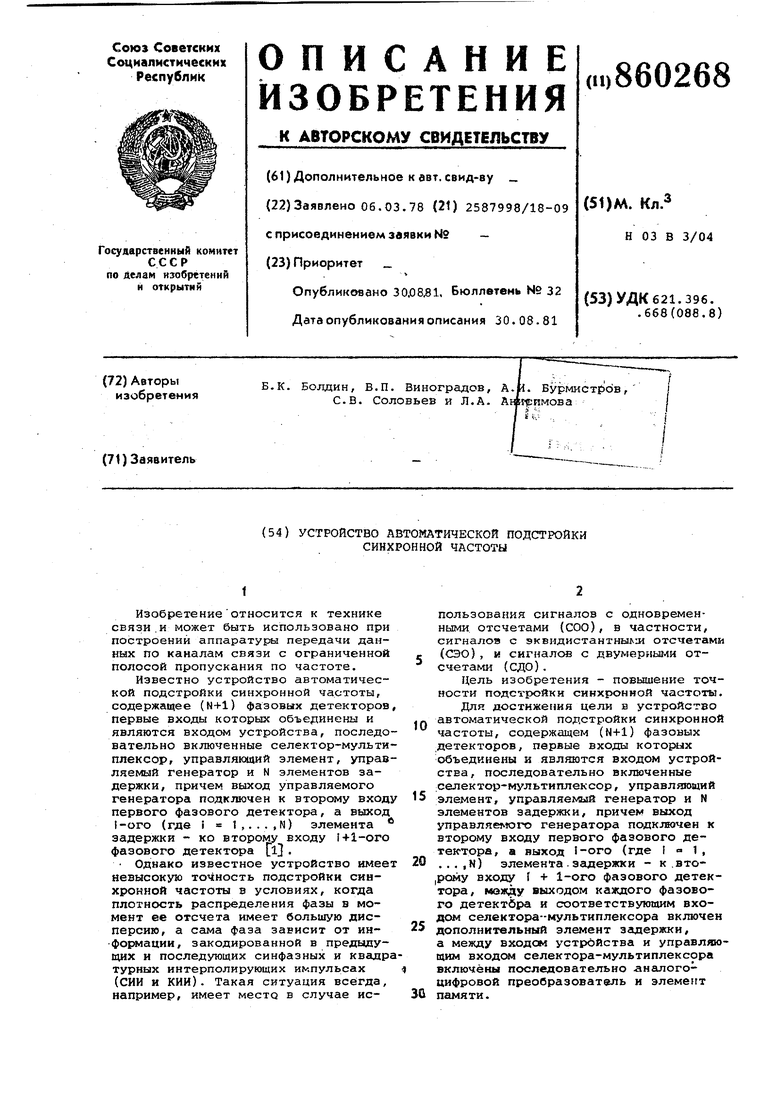

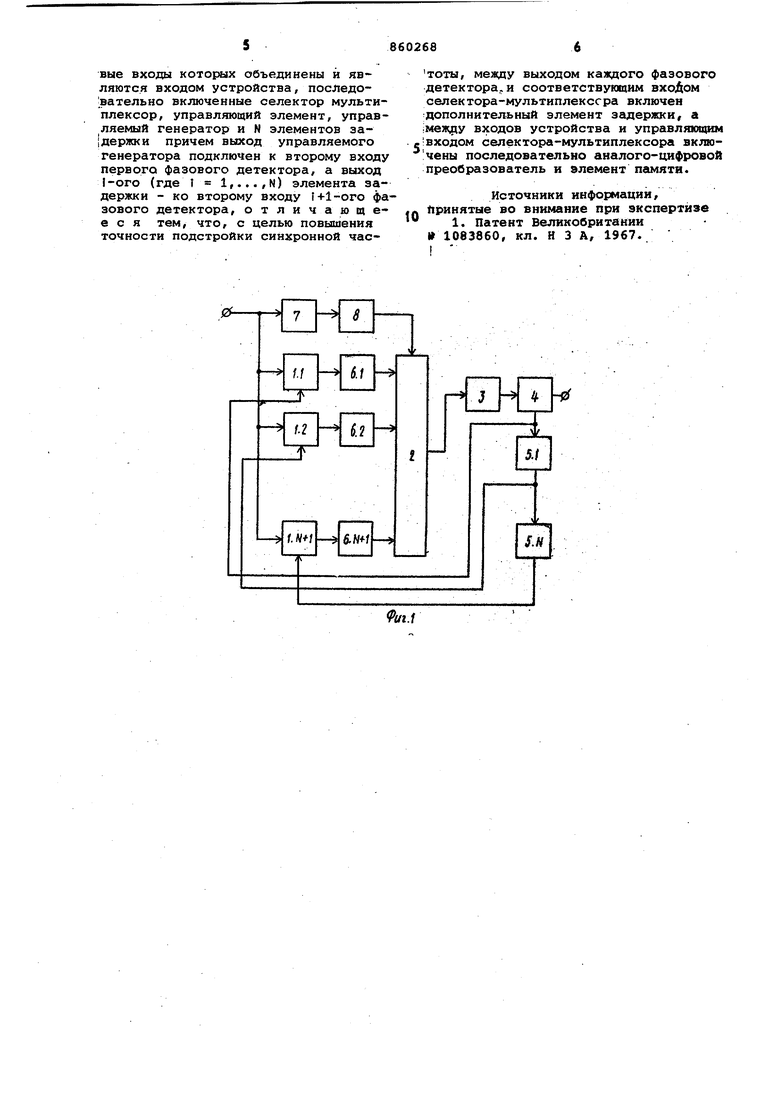

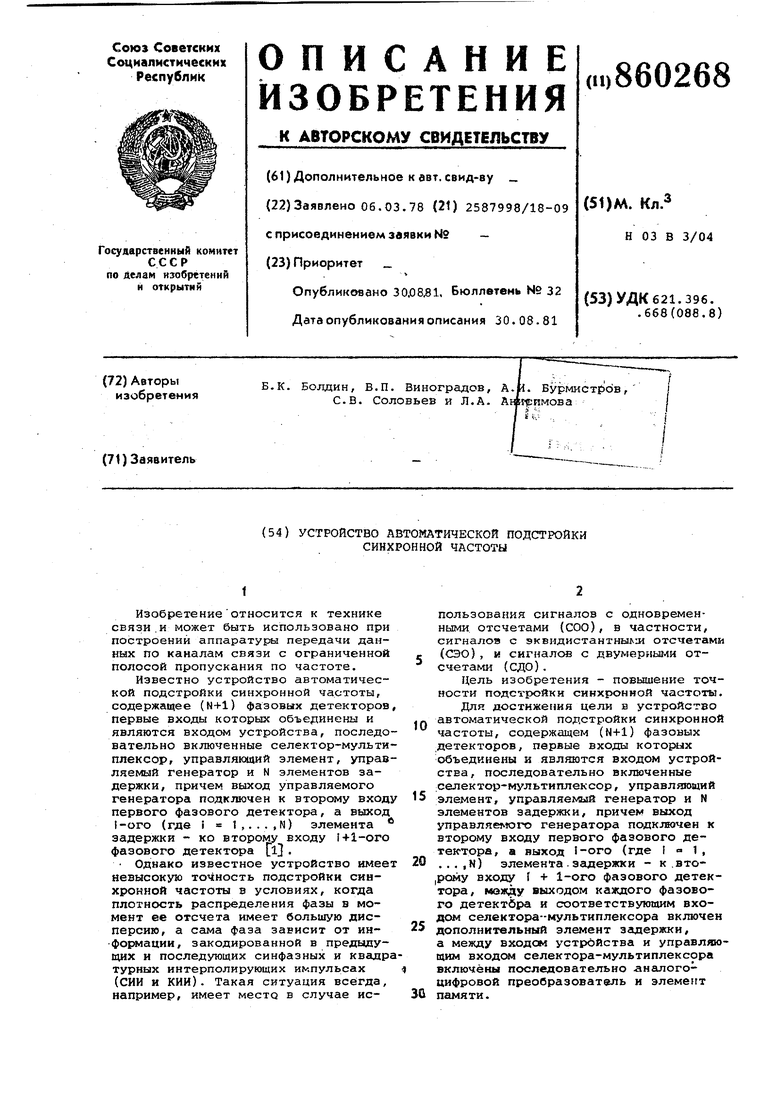

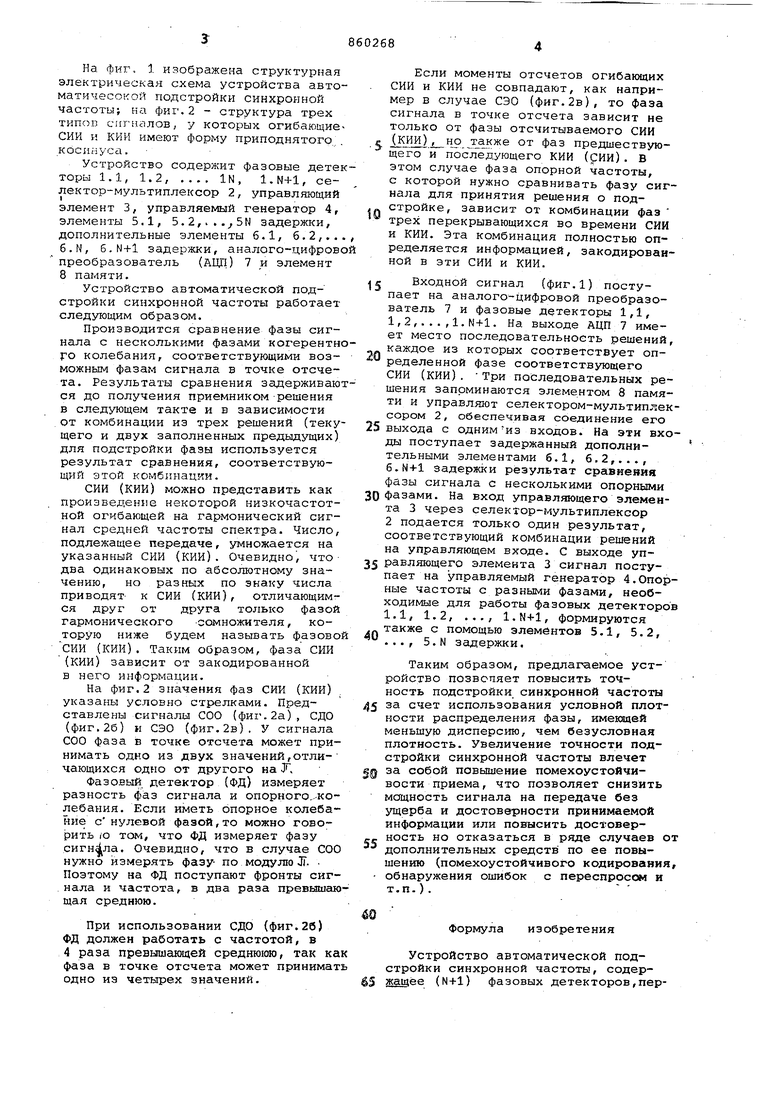

На фиг. 1 изображена структурная электрическая схема устройства автоматичесокой подстройки синхронной частоты; ка фиг.2 - структура трех типов сигналов; у которых огибающиеСИИ и КИИ имеют форму приподнятого.; . косигуса.

Устройство содержит фазовые детекторы 1.1, 1.2, IN, 1.N+1, селектор-мультиплексор 2, управляющий элемент 3, управляемый генератор 4, элементы 5.1, 5.2,..,,5N задержки, дополнительные элементы 6.1, 6.2,... 6.N, 6.N+1 задержки, аналого-цифрово преобразователь (АЦП) 7 и элемент 8 памяти.

Устройство автоматической подстройки синхронной частоты работает следующим образом.

Производится сравнение фазы сигнала с несколькими фазами когерентного колебания, соответствующими возможным фазам сигнала в точке отсчета. Результаты сравнения задерживаются до получения приемником -решения в следующем такте и в зависимости от комбинации из трех решений (текущего и двух заполненных предыдущих) для подстройки фазы используется результат сравнения, соответствующий этой комбинации.

СИИ (кии) можно представить как произведение некоторой низкочастотной огибающей на гармонический сигнал средней частоты спектра. Число, подлежащее передаче, умножается на указанный СИИ (КИИ). Очевидно, чтодва одинаковых по абсолютному значению, но разных по знаку числа приводят к СИИ (кии), отличающимся друг от друга только фазой гармонического -сомножителя, которую ниже будем называть фазово сии (КИИ). Таким образом, фаза СИИ (кии) зависит от закодированной в него информации.

На фиг.2 значения фаз СИИ (КИИ) указаны условно стрелками. Представлены сигналы СОО (фиг.2а), СДО (фиг.2б) и СЭО (фиг.2в). У сигнала СОО фаза в точке отсчета может принимать одно из двух значений,отличающихся одно от другого на Т.

Фазовый детектор (ФД) измеряет разность фаз сигнала и опорного,.-колебания. Если иметь опорное колебание с нулевой фазой,то можно говорить |0 том, что ФД измеряет фазу сигнала. Очевидно, что в случае СОО нужно измерять фазу- по модулю Х . Поэтому на ФД поступают фронты сигнала и частота, в два раза превышающая среднюю.

При использовании СДО (фиг.26) ФД должен работать с частотой, в 4 раза превышающей средню ою, так ка фаза в точке отсчета может принимат одно из четырех значений.

Если моменты отсчетов огибаницих СИИ и КИИ не совпадают, как например в случае СЭО (фиг.2в), то фаза сигнала в точке отсчета зависит не только от фазы отсчитываемого СИИ

с i Jiiil. ° предшествующего и последующего КИИ (рии). В этом случае фаза опорной частоты, с которой нужно сравнивать фазу сигнала для принятия решения о под0 С РОйке, зависит от комбинации фаз трех перекрывающихся во времени СИИ и КИИ. Эта комбинация полностью определяется информацией, закодированной в эти сии и КИИ.

5 Входной сигнал (фиг.1) поступает на аналого-цифровой преобразователь 7 и фазовые детекторы 1,1, 1,2,...,1.N+1. На выходе АЦП 7 имеет место последовательность решений,

каждое из которых соответствует определенной фазе соответствующего СИИ (кии). Три последовательных решения запоминаются элементом 8 памяти и управляют селектором-мультиплексором 2, обеспечивая соединение его

5 выхода с однимиз входов. На эти входы поступает задержанный дополнительными элементами 6.1, 6.2,..., 6.N+1 задержки результат сравнения фазы сигнала с несколькими опорными

0 Фззами. На вход управляющего элемента 3 через селектор-мультиплексор 2 подается только один результат, соответствующий комбинации решений на управляющем входе. С выходе управляющего элемента 3 сигнал поступает на управляемый генератор 4.Опорные частоты с разными фазами, необходимые для работы фазовых детекторов 1.1, 1.2, ..., l.N+l, формируются также с помощью элементов 5,1, 5.2,

..., 5.N задержки.

Таким образом, предлагаемое устройство позволяет повысить точность подстройки синхронной частоты

5 за счет использования условной плотности распределения фазы, имеющей меньшую дисперсию, чем безусловная плотность. Увеличение точности подстройки синхронной частоты влечет

g за собой повышение помехоустойчивости приема, что позволяет снизить мощность сигнала на передаче без ущерба и достоверности принимаемой информации или повысить достоверность но отказаться в ряде случаев от дополнительных средств по ее повышению (помехоустойчивого кодирования, обнаружения ошибок с переспросом и т.п.).

Формула изобретения

Устройство автоматической подстройки синхронной частоты, содержащёе (N+1) фазовых детекторов,первые входы которых объединены и являются входом устройства, последо вательно включенные селектор мультиплексор, управляющий элемент, управ ляемый генератор и N элементов за|держки причем выход управляемого генератора подключен к второму входу первого фазового детектора, а выход 1-ого (где I,...,N) элемента задержки - ко второму входу t+1-ого фазового детектора, отличающееся тем, что, с целью повышения точности подстройки синхронной частоты, между выходом каждого фазового детектора.и соответствующим вхоДом селектора-мультиплексора включен :дополнительный элемент задержки, а Itf&TKjay входов устройства и управляющим .входом селектора-мультиплексора включены последовательно аналого-цифровой преобразователь и элемент памяти.

Источники информации, J.J Принятые во внимание при экспертизе 1. Патент Великобритании I 1083860, кл. Н 3 А, 1967.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ГЕНЕРАТОРА ИМПУЛЬСОВ | 2004 |

|

RU2259630C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| СИНТЕЗАТОР ЧАСТОТЫ | 2002 |

|

RU2237972C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| Синхрогенератор | 1983 |

|

SU1190540A1 |

| Устройство для приема сигналов с комбинированной фазочастотной манипуляцией | 1985 |

|

SU1252967A1 |

| СИНТЕЗАТОР СВЕРХВЫСОКИХ ЧАСТОТ | 1992 |

|

RU2041564C1 |

| Система радиосвязи | 1986 |

|

SU1385305A1 |

. Q -t X -

- Л- Тчу-чх-г-T-7 . у t.y

-.TX т x X j XlTxXr

:: -x x xxc:xj c: c

--X-

(pui. 2

Авторы

Даты

1981-08-30—Публикация

1978-03-06—Подача