Изобретение относится к электросвязи и может быть использовано для приема сигналов с комбинированной фазочастотной манипуляцией.

Цель изобретения - повышение по- мехоустойчивости.

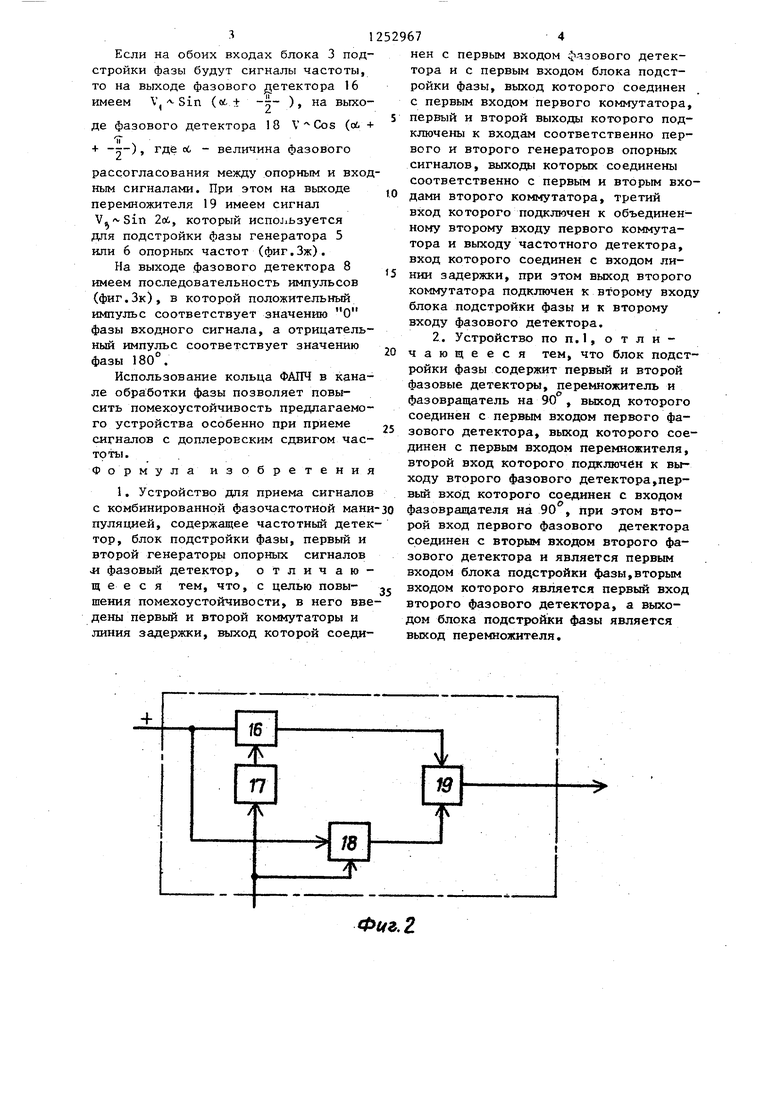

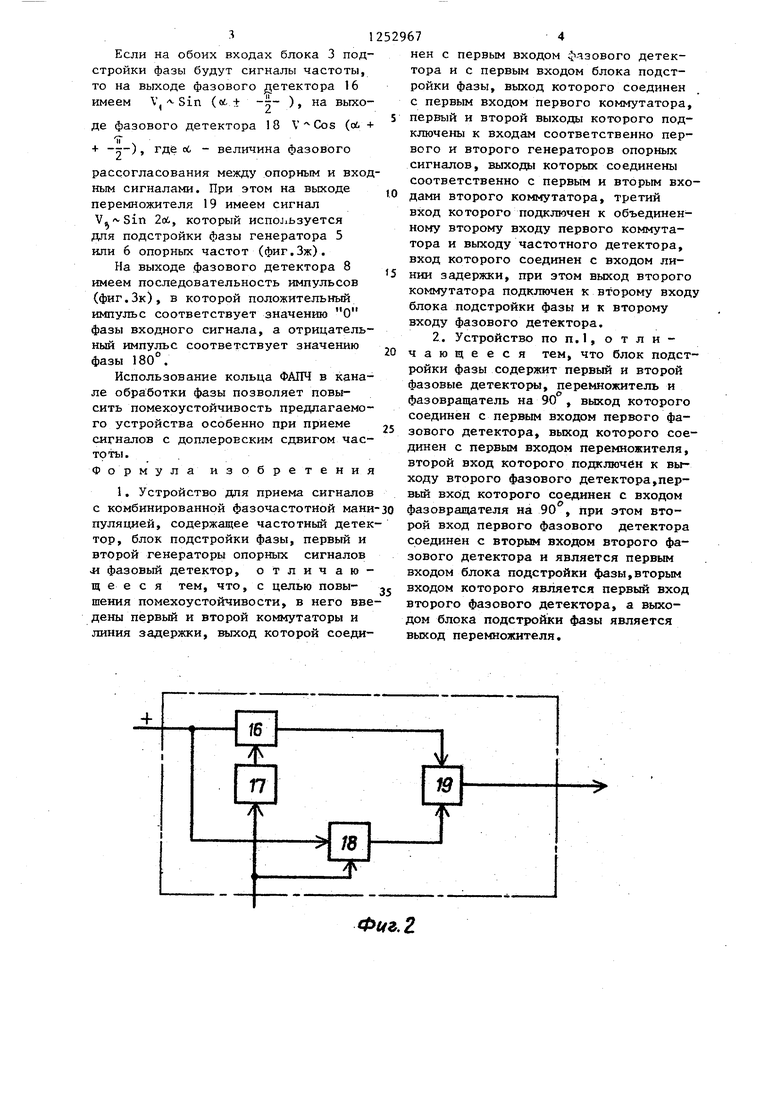

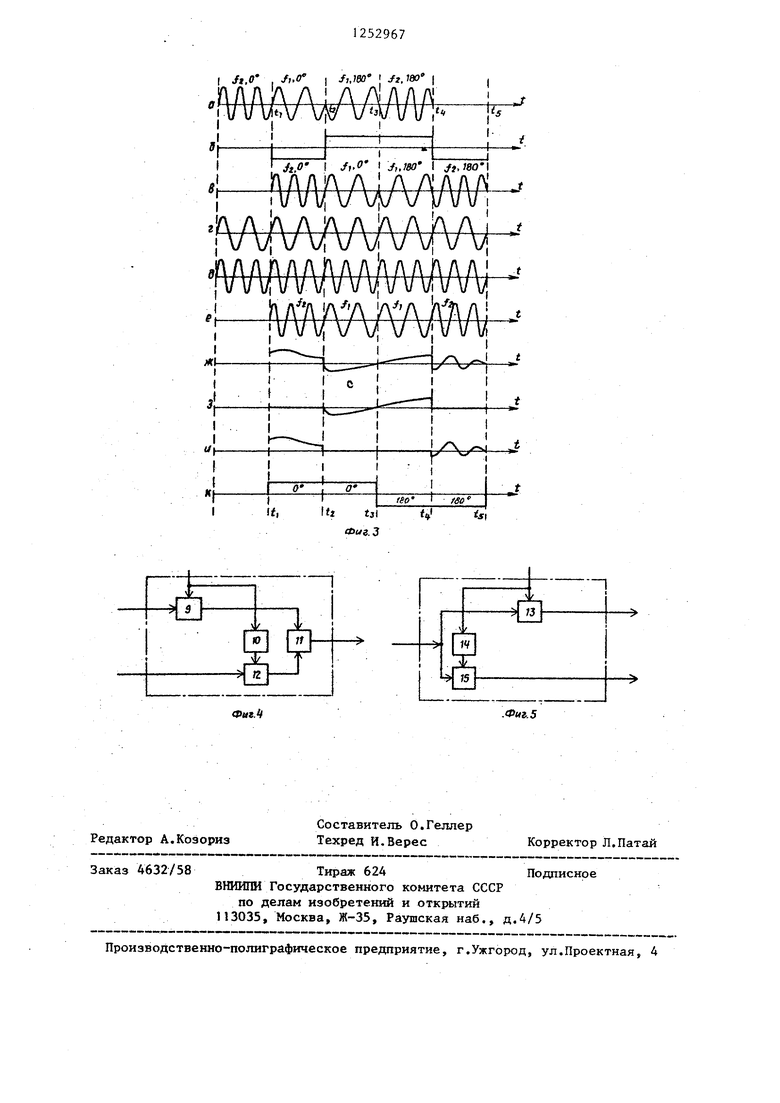

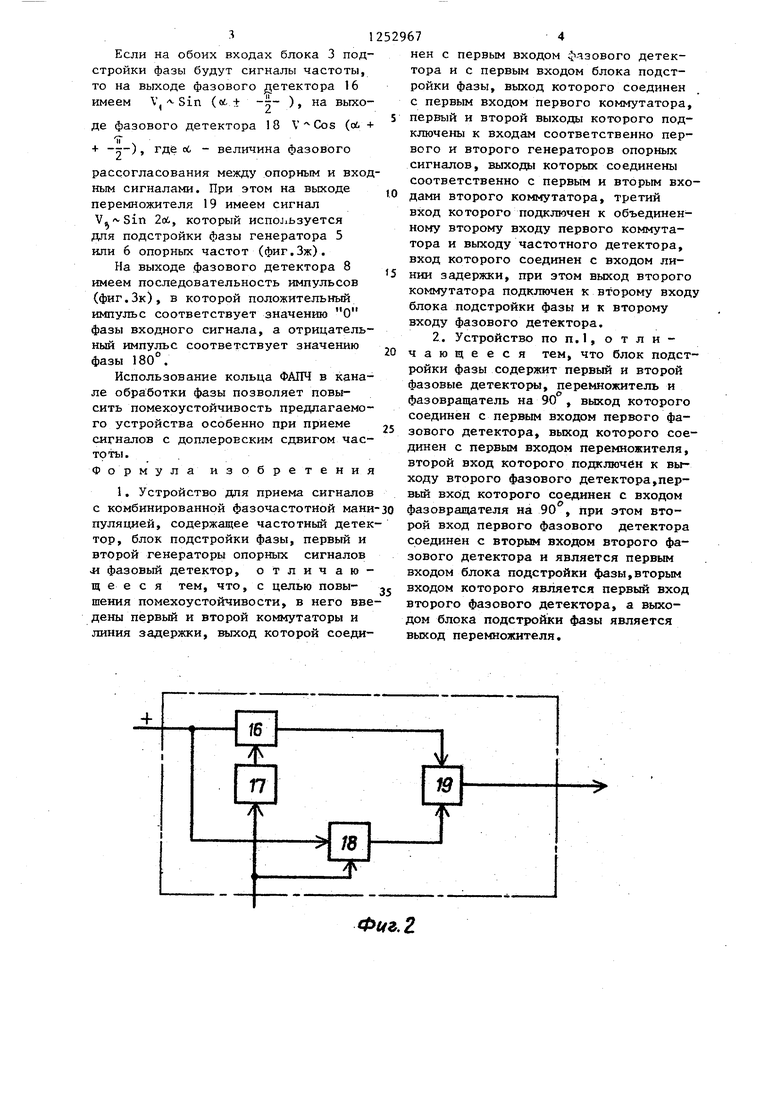

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема блока подстрой- ки фазы; на фиг. 3 - временные диаграммы; на фиг. 4 - структурная электрическая схема второго коммутатора; на фиг. 5 - структурная электрическая схема первого коммутатора.

Устройство для приема сигналов с комбинированной фазочастотной манипуляцией содержит частотный детектор 1, линик 2 задержкиi блок 3 подстройки фазы, первый коммутатор 4, первый 5 и второй 6 генераторы опорных сигналов, второй коммутатор 7 и фазовый детектор 8.

Второй коммутатор 7 содержит первый элемент И 9, элемент НЕ 10, элемент ИЛИ 11, второй элемент И 12.Первый коммутатор А содержит первый элемент И 13, элемент НЕ 14, второй элемент И 15. Блок 3 подстройки фазы содержит первый фазовый детектор 16, фазовращатель 17 на 90, второй фазовый детектор 18, перемножитель 19.

Устройство работает следующим образом.

Пусть на вход устройства поступа ет сигнал с фазочастотной манипуляцией (фиг.За), При этом в моменты

t, tp частотным детектором 1 принимается решение о частоте входного сигнала. На выходе частотного детектора 1 будет последовательность импульсов (фиг.Зб), в которой отрицательный импульс соответствует значению частоты f - , а положительный - значению частоты f, . Эта последовательность импульсов поступает на управляющие входы коммутаторов 4 и7. На выходе линии 2 задержки имеем сигнал (фиг.Зв), задержанный относительно входного сигнала на время обработки частоты. Генераторы 5 и 6 опорных сигналов вырабатывают опорные сигналы частот (4й€Г.Зг,д). Назначение второго коммутатора 7 состоит в том, чтобы на пеЬвом опорном входе фазового детектора 8 и первом входе блока 3 подстройки фазы был опорный сигнал (фиг.Зе), частота которого

совпадает с частотой сигнала, посту- пакицего на первый сигнальный вход фазового детектора 8 и первый вход блока 3 подстройки фазы.

Коммутатор 7 работает следующим образом.

При поступлении на третий управляющий вход коммутатора 7 и, следовательно, на управляющий вход элемента И 9 положительного импульса (соответствующий частоте f. ) сиг

нальный вход элемента И 9 открывается и на выход коммутатора 7 проходит через элемент ИЛИ 11 опорньш сигнал

частоты f. В этот момент на выходе элемента И 12 сигнал отсутствует. На его выходе сигнал появляется не только тогда, когда на управляющем входе коммутатора 7 будет отрицательный импульс (соответствующий частоте f 2 ).

На вькоде блока 3 подстройки фазы будет сигнал, соответствукшщй рассогласованию между фазами входного к опорного сигналов, при этом в период времени t,-t и будет сигнал рассогласования между опорным и сигналами частоты f , в периоды , сигнал рассогласования между опорным и входным сигналами частотьг. Для того,чтобы генераторы 5 и 6 опорных сигналов управлялись своим управляющим сигналом, используется коммутатор 4.

При поступлении на управляющий вход коммутатора 4 положительного юотульса с выхода частотного детектора 1 элемент И 13 открывается, элемент И 15 закрьшается, а управляющий сигнал проходит на управляющий выход первого коммутатора 4 (г.Зз), Тем самым осуществляется подстройка первого генератора 5 опорных сигналов.

При поступлении на вход коммутатора 4 отрицательного импульса зшрав- ляющий сигнал проходит на вход второго генератора 6 опорных сигналов (фиг.Зи). Тем самым каждый геиератор 5 и 6 опорных сигналов подстраивается только тогда, когда на входах блока 3 подстройки фазы имеется сигнал частоты, совпадающей с частотой данного генератора 5 или 6

опорных сигналов. В блоке 3 подстройки фазы осуществляется снятие фазовой манипуляции и выработка сигнала рассогласования.

Если на обоих входах блока 3 подстройки фазы будут сигналы частоты, то на выходе фазового детектора 16 имеем V,-v Sin (об + -|- ), на выходе фазового детектора 18 (об +

+ ), где об - величина фазового

рассогласования между опорным и входным сигналами. При этом на выходе перемножителя 19 имеем сигнал V. 2А, который испо:1ьзуется для подстройки фазы генератора 5 или 6 опорных частот (фиг.Зж).

На выходе фазового детектора 8 имеем последовательность импульсов (фиг.Зк), в которой положительный импульс соответствует значению О фазы входного сигнала, а отрицательный импульс соответствует значению фазы 180 .

Использование кольца ФАПЧ в канале обработки фазы позволяет повысить помехоустойчивость предлагаемого устройства особенно при приеме сигналов с доплеровским сдвигом частоты. Ф о р мула изобретения

1, Устройство дпя приема сигналов с комбинированной фазочастотной мани пуляцией, содержащее частотный детектор, блок подстройки фазы, первый и второй генераторы опорных сигналов -и фазовый детектор, отличающееся тем, что, с целью повы- шения помехоустойчивости, в него введены первый и второй коммутаторы и линия задержки, выход которой соеди16

Ж

Г7 Ж

нен с первым входом фазового детектора и с первым входом блока подстройки фазы, выход которого соединен с первым входом первого коммутатора, первый и второй выходы которого подключены к входам соответственно первого и второго генераторов опорных сигналов, выходы которых соединены соответственно с первым и вторым входами второго коммутатора, третий вход которого подключен к объединенному второму входу первого коммутатора и выходу частотного детектора, вход которого соединен с входом линии задержки, при этом выход второго коммутатора подключен к второму вход блока подстройки фазы и к второму входу фазового детектора.

2. Устройство по п.1, отличающееся тем, что блок подстройки фазы содержит первый и второй фазовые детекторы, перемножитель и фазовращатель на 90 , выход которого соединен с первым входом первого фазового детектора, выход которого соединен с первым входом перемножителя, второй вход которого подключен к выходу второго фазового детектора,первый вход которого соединен с входом фазовращателя на 90 , при этом второй вход первого фазового детектора соединен с вторым входом второго фазового детектора и является первым входом блока подстройки фазы,вторым входом которого является первый вход второго фазового детектора, а выходом блока подстройки фазы является выход перемножителя.

Ю Ж

Фиг. 2

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство содержит частотный детектор 1, блок 2 подстройки фазы (БПФ), генераторы 5 и 6 опорных сигналов, фазовый детектор (ФД) 8. Цель достигается введением двух коммутаторов (К) 4 и 7 и линии задержки. К 4 содержит два элемента И, элемент НЕ. К 7 содержит два элемента И, элемент НЕ и элемент ИЛИ. По п.2 БПФ 3 содержит два фазовых детектора, фазовращатель на 90° и перемножитель. Назначение К 7 состоит в том, чтобы на 1-м опорном входе ФД 8 и 1-м входе БПФ 3 был опорный сигнал, насто- та которого совпадает с частотой сигнала, поступающего на 1-й сигнальный вход ФД 8 и 1-й вход БПФ 3, К 4 предназначен для того, чтобы генераторы 5 и 6 управлялись своим управ- лякицим сигналом. В БПФ 3 осуществляются снятие фазовой, манипуляции и вьфаботка сигнала рассогласования. Использование кольца фазовой АПЧ в канале обработки фазы повышает помехоустойчивость устройства особенно при приеме сигналов с доплеровским (СДВИГОМ частоты, 1 8,п. ф-лы, 5 ил. с 5В (Л I Фиг.1

| Устройство для приема сигналов сКОМбиНиРОВАННОй чАСТОТНОй и ОТНОСиТЕльНО- фАзОВОй МАНипуляциЕй | 1979 |

|

SU809643A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-08-23—Публикация

1985-03-25—Подача