Изобретение относится к радиотехнике и может быть использовано в радиотехнических системах в качестве генератора высокостабильной сетки частот.

Целью изобретения является повышение спектральной чистоты и увеличение количества выходных частот.

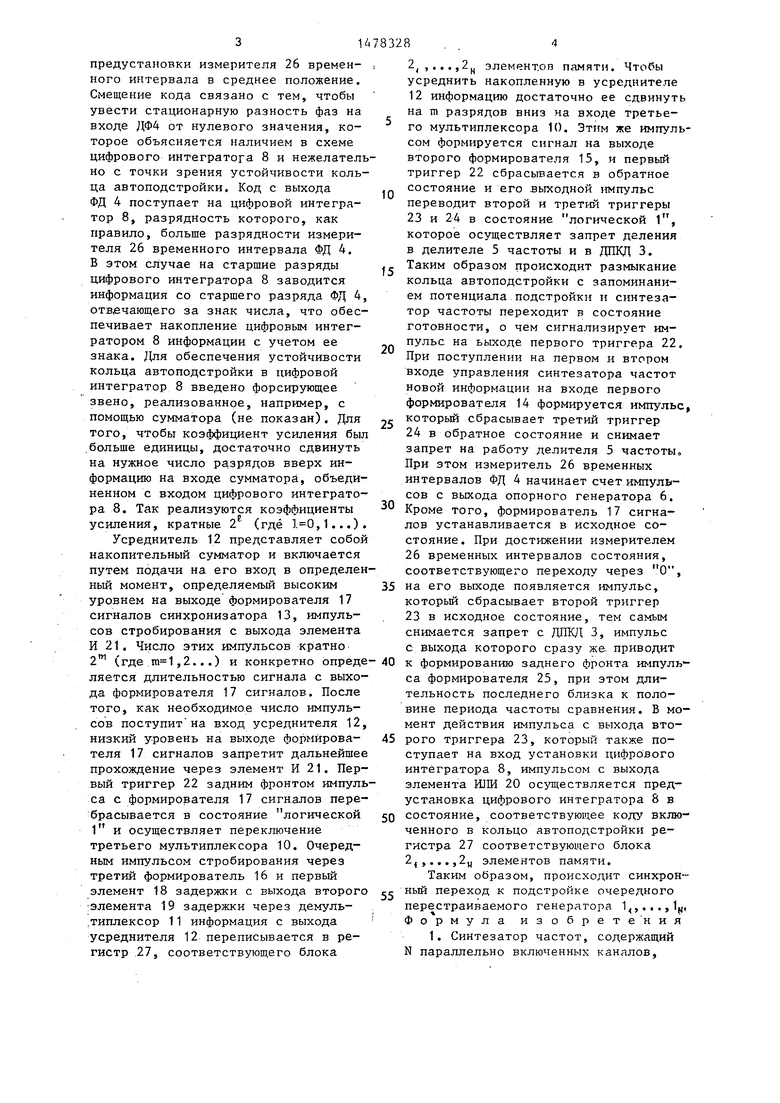

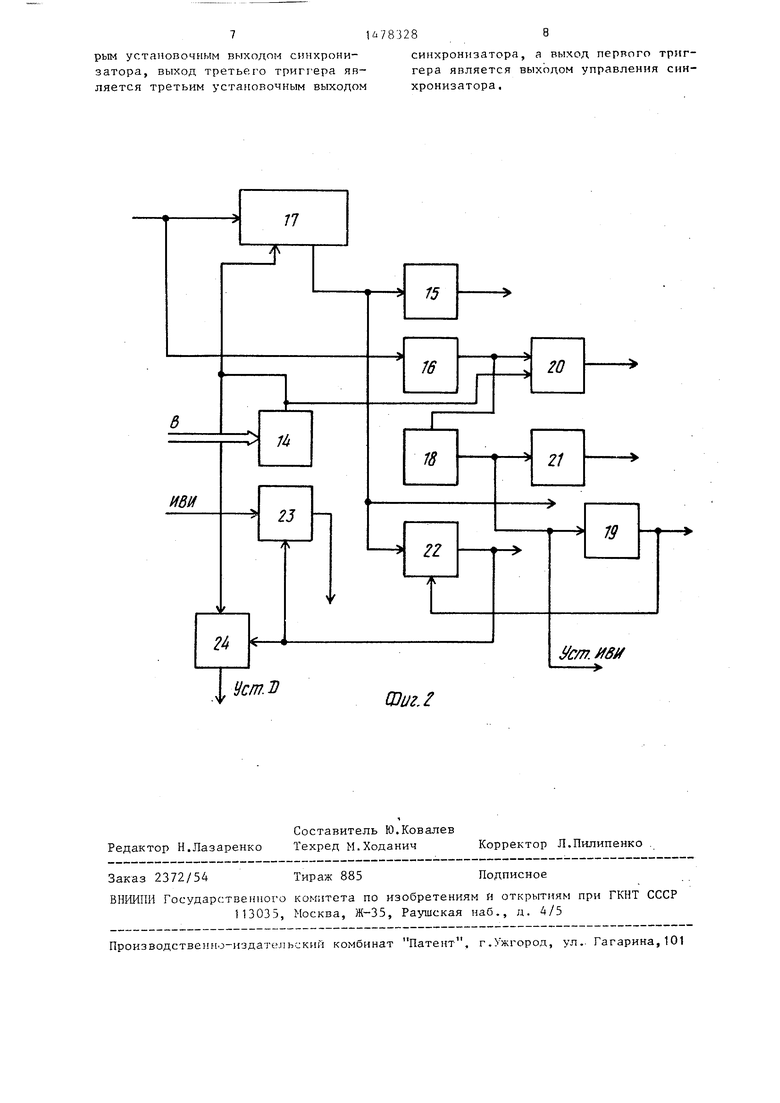

На фиг. 1 представлена электрическая структурная схема синтезатора частот, на фиг. 2 - структурная схема синхронизатора.

Синтезатор частоты содержит N перестраиваемых генераторов 1,,,... 1W первый, второй, ..., N-й блоки 2j,...,2N элементов памяти, делитель 3 частоты с переменным коэффициентом деления (ДПКД), фазовый детектор (ФД) 4, делитель 5 частоты, опорный генератор 6, первый мультиплексор 7, цифровой интегратор 8, второй мультиплексор 9, третий мультиплексор 10, демультиплексор 11, усреднитель 12, синхронизатор 13. Синхронизатор 13 при этом содержит первый и третий формирователи 14-16 импульсов, формирователь 17 сигналов управления, первый и второй элементы 18 и 19 за10 соответствующего блока элементов 2„,...,2Н памяти. Усреднитель 12 выполняет операцию усреднения кода ошибки на выходе цифрового интегра- vopa 8, и усредненный код через третий мультиплексор 10 в момент размыкания кольца автоподстройки переписывается в соответствующий реQ гистр 10. Второй мультиплексор 9 перед подключением очередного перестраиваемого генератора 1,...,1М обеспечивает предустановку цифрового интегратора 8. Синхронизатор 13

осуществляет полную синхронизацию работы узлов синтезатора частот, а с помощью опорного генератора 6 и делителя 5 частоты формируются необходимые опорные и тактовые после0 довательности импульсных сигналов.

Частоты отключенных от кольца автоперестройки перестраиваемых генераторов 1 ,..., 1 N поддерживают постоянными за счет напряжения, записан5 ного в соответствующий блок 2,...,2N элементов памяти, при этом фиксируется среднее значение сигнала подстройки, что обеспечивает минимальный частотный сдвиг и соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2081510C1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2085032C1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

Изобретение относится к радиотехнике и м.б. использовано в радиотехнических системах в качестве г-ра высокостабильной сетки частот. Цель изобретения - повышение спектральной чистоты и увеличение кол-ва выходных частот. Поставленная цель достигается введением делителя 5 частоты, цифрового интегратора 8, двух мультиплексоров 9, 10, усреднителя 12 и синхронизатора 13. Усреднитель 12 выполняет операцию усреднения кода ошибки на выходе интегратора 8 и усредненный код через мультиплексор 9 перед подключением очередного г-ра 1,..., 1N обеспечивает предустановку интегратора 8. Синхронизатор 13 осуществляет полную синхронизацию работы узлов синтезатора. Для обеспечения устойчивости кольца автоподстройки в интегратор 8 введено форсирующее звено, реализованное, например, с помощью сумматора. В синтезаторе обеспечивается постоянство стационарной разности фаз для различных г-ров, что, в свою очередь, исключает паразитные переходные процессы и связанное с ними увеличение флуктуаций частоты выходного сигнала. 1 з.п. ф-лы, 2 ил.

держки, элемент ИЛИ 20, элемент И 21, 30 минимальный паразитный фазовый уход

первый триггер 22, второй триггер 23, третий триггер 24. Фазовый детектор 4 состоит из формирователя 25 импульсов и измерителя 26 временного интервала, а каждый из N блоков элементов 2...,2W памяти содержит регистр 27 памяти и цифроаналоговый преобразователь (ЦАП) 28.

Синтезатор частот работает следующим образом.

Один из N перестраиваемых генераторов 1 4 , . .., 1 N , первый мультиплексор, ДИКДЗ, ФД4, цифровой интегратор 8 и соответствующий блок 2,,...,2N элементов памяти образуют замкнутое кольцо фазовой автоподстройки, при этом регистр 27 и ЦАП 28, входящие в состав каждого из N блоков элементов 21,..,,2М памяти выполняют функции преобразования цифрового сигнала фазового рассогласования с выхода третьего мультиплексора 10 в аналоговый сигнал управления перестраиваемым генератором 1, ,...,1N. Демультиплексор 11 осуществляет подключение требуемого перестраиваемого генератора 1.,,..., 1 „ к кольцу автоподстройки путем подачи импульсов стробирования на вход регистра

5

0

5

0

5

за время размыкания. В синтезаторе частот также обеспечивается постоянство стационарной разности фаз для различных генераторов, что в свою очередь исключает паразитные переходные процессы и связанные с ними увеличение флуктуации частоты выходного сигнала.

ФД 4 выполнен в виде цифрового фазового детектора. Сигнал с выхода ДПКД 3 поступает на один из входов формирователя 25, который формирует импульсы, длительность которых определяется моментами прихода импульсных сигналов с выхода делителя 5 частоты и ДПКДЗ и соответствует разности фаз этих сигналов. Сформированные таким образом импульсы поступают на вход измерителя 26 временного интервала, где преобразуются в цифровой код, при этом на выходе измерителя временных интервалов может быть как положительное число в прямом коде, так и отрицательное в дополнительном. Знак определяется относительно среднего значения, соответствующего длительности импульса формирователя 25. равной половине периода частоты сравнения, путем

предустановки измерителя 26 временного интервала в среднее положение. Смещение кода связано с тем, чтобы увести стационарную разность фаз на входе ДФ4 от нулевого значения, которое объясняется наличием в схеме цифрового интегратора 8 и нежелательно с точки зрения устойчивости кольца автоподстройки. Код с выхода ФД 4 поступает на цифровой интегратор 8, разрядность которого, как правило, больше разрядности измерителя 26 временного интервала ФД 4. В этом случае на старшие разряды цифрового интегратора 8 заводится информация со старшего разряда ФД 4, отвечающего за знак числа, что обеспечивает накопление цифровым интегратором 8 информации с учетом ее знака. Для обеспечения устойчивости кольца автоподстройки в цифровой интегратор 8 введено форсирующее звено, реализованное, например, с помощью сумматора (не показан). Для того, чтобы коэффициент усиления был больше единицы, достаточно сдвинуть на нужное число разрядов вверх информацию на входе сумматора, объединенном с входом цифрового интегратора 8. Так реализуются коэффициенты усиления, кратные 2 (где ,1...). Усреднитель 12 представляет собой накопительный сумматор и включается путем подачи на его вход в определенный момент, определяемый высоким уровнем на выходе формирователя 17 сигналов синхронизатора 13, импульсов стробирования с выхода элемента И 21. Число этих импульсов кратно 2т (где ,2...) и конкретно определяется длительностью сигнала с выхода формирователя 17 сигналов. После того, как необходимое число импульсов поступит на вход усреднителя 12, низкий уровень на выходе формирователя 17 сигналов запретит дальнейшее прохождение через элемент И 21. Первый триггер 22 задним фронтом импульса с формирователя 17 сигналов перебрасывается в состояние логической 1 и осуществляет переключение третьего мультиплексора 10. Очередным импульсом стробирования через третий формирователь 16 и первый элемент 18 задержки с выхода второго элемента 19 задержки через демуль- типлексор 11 информация с выхода усреднителя 12 переписывается в регистр 27, соответствующего блока

5

0

5

0

5

0

5

0

5

2{ ,...,2N элементов памяти. Чтобы усреднить накопленную в усреднителе 12 информацию достаточно ее сдвинуть на m разрядов вниз ча входе третьего мультиплексора 10. Этим же импульсом формируется сигнал на выходе второго формирователя 15, и первый триггер 22 сбрасывается в обратное состояние и его выходной импульс переводит второй и третий триггеры

23и 24 в состояние логической 1, которое осуществляет запрет деления в делителе 5 частоты и в ДПКД 3. Таким образом происходит размыкание кольца автоподстройки с запоминанием потенциала подстройки и синтезатор частоты переходит в состояние готовности, о чем сигнализирует импульс на выходе первого триггера 22. При поступлении на первом и втором входе управления синтезатора частот новой информации на входе первого формирователя 14 формируется импульс, который сбрасывает третий триггер

24в обратное состояние и снимает запрет на работу делителя 5 частоты При этом измеритель 26 временных интервалов ФД 4 начинает счет импульсов с выхода опорного генератора 6. Кроме того, формирователь 17 сигналов устанавливается в исходное состояние. При достижении измерителем 26 временных интервалов состояния, соответствующего переходу через О, на его выходе появляется импульс, который сбрасывает второй триггер

23 в исходное состояние, тем самым снимается запрет с ДПКД 3, импульс с выхода которого сразу же приводит к формированию заднего фронта импульса формирователя 25, при этом длительность последнего близка к половине периода частоты сравнения. В момент действия импульса с выхода второго триггера 23, который также поступает на вход установки цифрового интегратора 8, импульсом с выхода элемента ИЛИ 20 осуществляется предустановка цифрового интегратора 8 в состояние, соответствующее коду включенного в кольцо автоподстройки регистра 27 соответствующего блока 2,,...,2Н элементов памяти.

Таким образом, происходит синхронный переход к подстройке очередного перестраиваемого генератора 14,...1р Формула изобретения

каждый из которых содержит последовательно соединенные блок элементов памяти и перестраиваемый генератор, последовательно соединенные первый мультиплексор, делитель частоты с переменным коэффициентом деления и фазовый детектор, а также опорный генератор и демультиплексор, при этом выход перестраиваемого генератора каждого из N каналов подключен к соответствующим сигнальным входам первого мультиплексора, вход управления которого объединен с управляющим входом демультиплексора и является первым управляющим входом синтезатора частот, а вход предустановки делителя частоты с переменным коэффициентом деления является вторым управляющим входом синтезатора частот, отличающийся тем, что, с целью повышения спектральной чистоты и увеличения количества выходных частот, введены синхронизатор, делитель частоты и последовательно соединенные второй мультиплексор, цифровой интегратор, усреднитель и третий мультиплексор, при этом вход и выход делителя частоты подключены соответственно к выходу опорного генератора и к второму входу фазового детектора, ин- формационный вход которого соединен с информационным входом цифрового интегратора, выход которого подключен к второму входу третьего мультиплексора, управляющий вход цифрового генератора соединен с выходом управления синхронизатора, вход управлени синхронизатора подсоединен к входу управления демультиплексора, первый и второй входы синхронизатора подключены соответственно к первому и второму выходам фазового детектора, установочный вход которого соединен с первым установочным выходом синхронизатора, установочный вход делителя частоты с переменным коэффициентом деления объединен с входом установки цифрового интегратора и подключен к второму установочному выходу синхронизатора, третий установочный выход которого подключен к установочному входу делителя частоты, выход опорного генератора соединен с тактовым входом фазового детектора, первый, второй и третий выходы стробирования синхронизатора соответственно подключены к входу стробирования цифрового интегратора.

я

4783286

к входу стробирования усреднителя, к второму информационному входу де- мульгиплексора, каждый из N выходов которого подключен к входу стробирования блока элементов памяти соответствующего из N каналов, выход обнуления синхронизатора соединен с входом обнуления усреднителя, информационные входы блока элементов памяти каждого из N каналов объединены и подключены к выходу третьего мультиплексора, цифровой выход блока элементов памяти каждого из N каналов соединен с соответствующим информационным входом второго мультиплексора.

15

0

0

5

чающийся тем, что синхронизатор содержит последовательно соединенные первьй формирователь импуль- Осов, формирователь сигналов управления и второй формирователь импульсов, последовательно соединенные

д третий формирователь импульсов, первый элемент задержки, второй элемент задержки, первый триггер и второй триггер, а также третий триггер, элемент ИЛИ и элемент И, первый вход которого объединен с вторым входом первого триггера и подключен к выходу формирователя сигналов управления, информационный вход которого объединен с входом третьего формирователя импульсов и является первым входом синхронизатора, первый и второй входы элемента ИЛИ подключены соответственно к выходу первого формирователя импульсов и выходу третьего формирователя импульсов, выход элемента ИЛИ является первым выходом стробирования синхронизатора, второй вход элемента И подключен к выходу первого элемента задержки, выход элемента И и выход второго элемента задержки являются соответственно вторым и третьим выходами стробирования синхронизатора, выход первого элемента задержки является первым установочным выходом синхронизатора, выход второго формирователя импульсов является выходом обнуления синхронизатора, первьй и второй входы третьего триггера соединены соответственно с выходом первого триггера и вы5 .ходом первого формирователя импульсов,вход которого является входом управления синхронизатора,второй вход и выход второго триггера являются соответственно вторым входом и вто0

5

0

рым установочным выходом синхронизатора, выход третьего триггера является третьим установочным выходом

1 783288

синхронизатора, а выход первого триггера является выходом управления синхронизатора.

Фиг.

| Цифровой синтезатор частот | 1980 |

|

SU1042188A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1986-09-16—Подача