(54) УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для спектрального анализа | 1978 |

|

SU767774A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для спектрального анализа | 1981 |

|

SU1013972A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

Изобретение относится к .цифровой вычислительной технике и может быть использовано при создании специализированных вычислительных машин для спектрального анализа процессов и сигналов, имитаторов случайных процессов с заданными управляемыми спект Рсшьными характеристиками, вычислительно-моделирующих комплексов для испытаний изделий на вибрационные, ударные, электрические, и другие воздействия, навигационных и радиолокационных систем слежения и обнаружения Известно устройство для спектрального анализа, которое позволяет получить спектр или спектр мощности про цессов и сигналов в одной из базисных систем функций. Оно обеспечивает вычисления оценок спектральных характеристик в классической системе тригонометрических функций одним из на иболее быстродействукхцих способов быстрым преобразованием Фурье ИЗ Известны другие устройства, котоуы& позволяют получить оценки спектра или спектра мощности в системе базисных функций Уолша и в основу их работы положен способ преобразования Уолша. Существенными признаками устройства ii являются применение блока задания систекы базисных функций в виде функционального генератора или долговременной памяти, осуществляющий формирование в заданные моменты времени выборочные значения безисных функций в частности, тригонометрических или функций Уолша, арифметического блока, включающего в себя блок умножения и сумматор, блока управления, 1регламентирУн)щего взаимодействие всех структурных узлов устройства. Недостаток известного устройства связан с невозможностью получения непосредственно по реализации процесса спектра мощности Уолша. Наиболее близким по технической сущности к предлагаемому является анализатор, содержащий блок вычисления корреляционной функции, сумматор, два переключателя, блок памяти , блок вычисления спектра мощности Фурье, счетчик и триггер. Устройство обеспечивает вычисление спектра мощ ности Фурье процесса и его корреляционной функции 2. Недостатками таких устройств для спектрального анализа, присущим в полной мере к известному является принципиальная невозможность получения спектра мощности Уолша непосредственно из спектра мощности Фурье, т.е. ограничение функциональных возможностей, что не позволяет решить ряд задач в условиях, когда исходный (анализируемый) процесс недоступен для анализа, но его характеристики известны априори и заданы в виде спектра мощности Фурье, а также невозможность вычисления отдельных, заданных компонент спектра мсндности : Уолша. Цель изобретения - расширение функ циональных возможностей за счет получения спектра мощности Уолша по известному спектру мощности Фурье. Поставленная цель достигается тем что в устройство для. спектрального анаипиза, содержащее счетчик, первый вход которого является первым входом устройства, второй вход счетчика объединен с первым входом сумматора, первый выход счетчика подключен ко входу первого триггера, блок вычисле ния спектра мощности Фурье, вход которого является вторым входом устрой ства, а выход соединен с первым входом первого блока памяти, второй вхо которого является третьим входом уст ройства, введены дешифратор, формиро ватель адреса и блок синхронизации, два блока памяти, два блока формирования дополнительного кода, блок эле ментов И, второй триггер, блок элементов ИЛИ, переключатель и блок умножения, входы которого подключены соответственно к выходу первого блок памяти и к выходу блока элементов ИЛИ, входы которого подключены соответственно к выходам второго и треть го блоков памяти, входы которых подключены соответственно к первому и второму выходам переключателя, входы которого соединены соответственно с выходом второго триггера и с первым выходом Первого и второго блоков формирования дополнительного кода, вторые входы которых соединены соответственно .с и вторым входами блока элементов И, входы первого бло ка формирования дополнительного кода подключены соответственно к выходу счетчика и к выходу первого триггера входы второго блока формирования дополнительного кода соединены соответ ственно с выходом формирователя адре са, и с выходом первого триггера, тр тий вход первого блока памяти подклю й чей к выходу формирователя адреса, вход второго триггера соединен с вы ходом блока элементов И, выход блока умножения соединен со вторым входом сумматора. На чертеже представлена структур-ная схема устройства. Устройство содержит счетчик 1, де шифратор 2, формирователь 3 адреса, блок 4 синхронизации, первый 5 и второй б триггеры, первый 7 и второй 8 блоки формирования дополнительного кода, блок 9 элементов И, переключатель 10, блок 11 вычисления спектра мощности Фурье, первый 12, второй 13И третий 14 блоки памяти, блок 15 элементов ИЛИ, блок 16 умножения, сумматор 17. Первые входы устройства и счетчика 1 соединены между собой, второй вход последнего подключен к выходу блока 4 синхронизации и второму isxoду сумматора 17, первый выход подключен ко входу дешифратора 2 и второму входу первого блока 7 формирования дополнительного кода, а второй выход соединен со входом первого триггера 5 , вход которого подключен к первым входам первого 7 и второго 8 блоков Формирования дополнительного кода, первые выходы которых соединены с первым и вторым входами блока элементов И 9, а вторые выходы подключены к первому и третьему выходам переключателя 10 соответственно, первый и второй выходы последнего подключены коВходам второго 13 и третьего 14 блоков памяти соответственно, соединенными выходамисоответственно с первым и вторым входами блока 15 элементов ИЛИ; выход которого подключен к первому входу блока 16 умножения, который вторым входом подключен к выходу первого бЛока 12 памяти, а выходом подключен к первому входу сумматора 17, включенного последовательно с выходом устройства, .дешифратор 2, формирователь 3 адреса и блок 4 синхронизации соединены последовательно, причем вход последнего подключен ко вторым входам второго блока 8 формирования дополнительного кода и первого блока 12 памяти, вход блока 11 вычисления спектра мощности Фурье соединен со вторым входом устройства, а выход подключен кпервому входу первого блока 12 памяти, соединенного третьим входом с третьим входом устройств.а, конъюнктор 9 и второй триггер 6 соединены последовательно, причем выход последнего подключен ко второму входу переключателя 10. Счетчик 1 предназначен для формирования последовательностей номеров г вычисляемых- коэффициентов спектра мощности Уолша. Начальное состояние счетчика, т.е. первый номер г, с которого необходимо начать вычисления, записывается с первого входа устройства, а изменение состояния счетчика на единицу выполняется по импульсу, пбступакрщему на его второй вход. Разрядность счетчика m определяется максимальн:1 м количеством пересчитываемых спектральных компонент (т-1) младших разрядов счетчика подается на первый его выход, а старший разряд - на второй выход, в процессе функционирования устройства состояние счетчика 1 определяет номер цикла. Начальный номер цикла определя-чтся начальным состоянием счетчика Дешифратор 2 осуществляет управле йие работой формирователя 3 адреса и функционирует в соответствии с выражениемY R fef)ffi l2---i) геЬ,,- -) где - выходной (т-1) - разрядны двоичный код/ (2 г), R (2г-1) (т-1) - старших разрядов кодов Грея соответственно от четных и нечетных номеров г коэффициентов спектра мощности Уолша. Формирователь 3 адреса предназначен для формирования адресов для пер вого 12, второго 13 и третьего 14 блоков памяти путем формирования пос ледовательности кодов при фиксирован ном коде на входе, т.е. в процессе функционирования устройства входному преобразованному коду номера цикл ставится в соответствие ряд номеров тактов, формируелих на выходе. Номера тактов связаны функциональной зависимостью, определяемой законом работы, преобразователя 3 кода. Блок 4 синхронизации обеспечивает работу счетчика 1, задание очеред ного номера цикла и выдачу информаци из сумматора 17 на выход устройства по концу цикла. Первый 5 и второй б триггеры пред назначены для управления работой пер вого 7 и второго 8 блоков формирования дополнительного кода и переключа теля 10 соответственно. Первый триггер 5 соединен своим установочным вх дом со старшим г разрядом счетчика i второй триггер 6 подключен установоч ным входом через конъюнктор 9 к первым младшим разрядам кодов k и г. . Первый 7 и второй 8 блоки формиро вания дополнительного кода предназна чены для преобразования в соответствии с управляющим сигналом на первом входе поступающих на вторые входы кодов в адреса для второго 13 или третьего 14 блоков памяти/ старшие разряды сформированных кодов подаются на входы переклю1чателя 10, а первые разряды подключены ко входам конъюнктора 9. Получение дополнитель ного кода числа первым 7 и вторым 8 блоками формирования дополнительного кода может быть выполнено по любому из известных методов .ч Блок 9 элементов И выполняет операцию логического умножения над первыми (младшими) разрядами кодов, фор мируелвлми первым 7 и вторым 8 блоками формирования дополнительного кода Переключатель 10 обеспечивает коммутацию и группировку поступающих на первый и второй входы кодов в соответствии с управляющим сигналом на третьем входе в целях формирования адреса для второго 13 или третьего 14 блока памяти. Группировка осуществляется в соответствии с заданным законом коммутации. Блок 11 вычисления спектра мощноети Фурье предназначен для получения козффициентов спектра мощности процесса, поступсшхцего на его вход со второго входа устройства, ;io любому из известных способов (прямой, метод преобразования, быстрые алгоритмы, через корреляционные функции и т.д.); Первый блок 12 памяти предназначен для приема с выхода блока 11 вычисления спектра мощности Фурье или с третьего входа устройства и хранения коэффициентов спектра мощности Фурье в. естественном порядке, т.е. первый коэффициент - в первой ячейке памяти, второй - во второй ячейке и т.д. Второй 13 и третий 14 блоки памяти предназначены для хранения матрицы ядра преобразования в соответствии с принятой процедурой упаковки (адресации). В каждом из блоков памяти хранится часть общей матрицы ядра преобразования. Эти части матрицы упаков.аны (специально организованы) с целью устранения избыточной информадии. Блок элементов ИЛИ 15 выполняет передачу на выход считанных со второго 13 или третьего 14 блоков памяти кодов. В операционную часть устройства входят блок 16 умножейия, выполняющий перемножение поступающих на.первый и второй его входы кодов, сумматор 17 (накапливаквдего типа), обеспечивающий передачу на выход результатов операщий (в конце цикла работы устройства) по низкому уровню напряжения на- втором его входе. Формирователь 3 адреса и переключатель 10 имеют особенности схемных решений.и функционирования. Формирователь 3 содержит (т-1) схему преобразования, Ка1ждая из которых преобразует входной (m-l) - разрядный код в последовательность кодов по соотношению Yi 24t2e.-i),1 1,2 ... где Y4 - функционально-связанная и определяемая параметром j f последовательность кодов, j - номер разряда, в котором записана единица во входном двоичном коде, определяющий номер схемы формирователя адреса, j в 1,2,... т-1. В табл. 1 поясняется работа формирователя адреса всех возможных комбинаций входных кодов. Каждое число последовательности является номером такта работы устройства длина послеовательности определяет длительность икла. Признаком конца цикла являвтся нулевой код, формируемый в конце каждой последовательности. Таблица 1 Г-----1- Вход схемы .0001 1,3,5,...,(п-1),0 100. , .0010 2,6,10,...,(п-2),0 200., .0100 4,12,20, ...., {п-4), 300.. „im-2 10. . .0 Таким обра:зом, формирователь адре са кода формирует заданную последова тельность кодов; соответствующую дан .ному кодовому набору на входе. Нс1Иболее простым схемным решением формирователя 3 является реализация его в виде комбинационного логического блока, синтезированного по любому из известных методов синтеза ко нечных автоматов. Переключатель 10 выполняет группировку двух кодов, поступакядих на первый и третий его входы, в один (2т-3) разрядный код и работает в двух режимах в зависимости от управляющего сигнала на втором его входе. Первый режим определяется высоким логическим уровнем напряжения на втором входе, при этом выполняется группировка кодов, поступающих на первыйи третий входы в соответствии :; выражением 1) Km Km-1 -. . Ini-l- V-a , (i) где ....K - двоичный код числа К (номера такта) на третьем входе; г ,.... г, - двоичный код числа (номера цикла) на первом входе (2т-3) - разрядный код адреса D передается при этом на первый выход -переключа теля 10. Второй режим переключателя 10 определяется низким логическим уровнем напряжения на втором входе и обеспечивает группировку входных кодов в виде Ь Кш K,m-1-.. W где (2т-3) - разрядный код адреса 0 передается на второй вы ход. Конструктивно переключатель 10 может представлять собой логическую комбинационную схему. В основу функционирования предлагаемого устройства положен ряд матет матических соотноиений связи спектро мощности Фурье (СМФ) и Уолша (СМУ), а также некоторые свойства матрицы ядра преобразований. Известно, что спектры мощности Фурье и Уолша связаны соотношением . ) 5: Рр1к)/Лкг( 5) где /Ар/ - матрица ядра преобразова ния. Известный метод вычисления эЛементов матрицы ядра преобразования обладает существенным недостатком: матрица не имеет симметричных блоков, что требует вычисления или хранения в памяти всех (п-1) X (п-1) элементов. В предлагаемом изобретении получены соотношения для вычисления элементов матрицы ядра преобразования, при этом матрица получается инверсно-симметричной относительно центрального вертикального столбца, а получаемые результаты численно совпадают с известными. Элемент экг матрицы Ацг вычисляется по формуле п f2 S ii lLii l l. (251«9.i(25-l)l§(9H25bK2 -)} где g/(p) i-ый разряд кода Грея, образованный от числа А кг. Тогда квадратную матрицу АКГ (п-1)-(п-1) элементов можно записать в виде Q 0. о an О... 00-1(-1) О 000 сцб i(n-i) о С1(н-1иС a(n-i)iOQ(n-i)50.-.0 Q(n-iKii--i) Матрицу ядра преобразования характеризуют следующие свойства согласно (6). Матрица является разреженной (слабозаполненной), т.е. количество нулевых элементов превышает величину (п-1). Матрица является инверсно-симметричной относительно столбца с номеров п/2, т.е. (И-к)(и-1-) -Например , (KH--i); и 111-1)1и-з Разработанный для устройства метод упаковки матрицы А кг заключается в разбиении ее на две матрдаы: первая из них AKV- -размерности п/2 х п/4 составлена из элементов матрицы А КС следующим образом. Чпл а, .. .а-,(и/г--( Оъ- 0)5 QjS ) (п-л)1 a{n-i)3 аси--1 5.-cnn-i)tf,%-i) Вторая матрица А размерности п/4 х д п/4 имеет структуру огг О 016 О 1,0 О С1б2 а ClggQiib Ct6,io-. а(и-г)1 a(n-4W а1и-7)(/г) Упорядочим матрицы f и . п тем введения новой инде1 сации -aoWaM) Оцо aHi,.,ai(A,--i 0(-1 )о 15-Ь-а(а-1)1.1 C(oi OOI-- Q() On ct-it.-QiC-) a()i q(j,-i)i.-qQ-iK 1 ,l ... n/4 ,l ... n/2 ,l..., n/4/ ,2,..., n/4 и определим связь индексов ij и р, с индексами k,r. Несложно заметить что t ()/2l-1-, J (r+lV21- .К.ГеНЕЧЕТНЫЕ .)/4l- 1(1-2 КРАТНО 4 к/4к-кр к/4 к PAT но «ч e 7lг-мгтно Например, при (, , эл мент ,i3 матрнцы А„г- в упак ванном виде соответствует элементу aij а 6,9 матрицы A-ii . Матрицы Aii и Apt записываются во второй 13 и тр тий 14 блоки памяти построчно с нул вой и первой ячеек памяти соответственно табл. 2 и 3). Характерной особенностью (7) и (8) является простота связи индекс в случае, если k и г представить в двоичном коде. Так для (7) достато но исключить первый (младший) разр двоичного представления k или г, т.е.. 1 Km w-1,., Кг 5 Гт ги-1-1 ... гг Действительно, преобразование (7) к . j-r d- Г--1 1 г а 2 г г позволяет заю1ючить, что поскольку при нечетных k и г в младших разрядах их двоичного представления-все записаны единицы, то операции вычи тания единицы и деления на два выполняются путем отбрасывания младш го разряда (сдвига вправо на один р ряд) . С учетом инверсно-симметричной структуры матрицы А кг окончательно имеем. к т-1 ... г .Q. ) rtt) Гил-1 ... Гг Аналогично (5) для двоичного преяст ления р и I имеет вид vn Кт-1 ... ) Гт Гт-1 .,. Это вытекает из того, что соотношение (8) при k четном реализуется пу тем сдвига кода k вправо на два раз ряда. Соотнесения (9) и (10) отража ют принцип упаковки исходной матриц и систему адресации упакованных мат риц . Предлагаемое устройство обеспечивает вычисления в трех основных режимах. Первый режим работы предназначен для вычисления спектра мощности Фурье процесса, поступающего на второй вход устройства, при этом функци- онирует только блок 11 вычисления спектра мощности Фурье, так и с выхода блока 12 памяти. Второй режим вычислений предназначен для получения спектра мощности Уолша процесса, поступающего на второй вход устройства, при этом задействованы все блоки устройства. Третий режим работы позволяет вычислить спектр мощности Уолша в том случае, когда анализируемый процесс недоступен для анализа или проведения ангилиза достаточно сложно, но о процессе известна информация в виде спектра мсщности Фурье. Последний подается на третий вход устройства, при этом блок 11 вычисления спектра мощности Фурье из процесса вычислений исключается. Первый режим по организации работы тривиален, поэтому функционирование устройства рассматривается для двух последних режимов, отличающихся лишь характером исходных (анализируемых) данных и при списании не разделяющихся. Функционирование устройства начинается с задания начального номера г компоненты спектра мощности Уо.лша в счетчик 1. Анализируемый процесс x(v) подается на.второй вход устройства, преобразуется блоком 11 вычисления спектра мощности Фурье в упорядоченную последовательность коэффициентов, которые записываются по последовательным адресам первого блока 12 памяти (в третьем режиме коэффициенты спектра мощности Фурье записываются непосредственно с третьего входа устрой.ства в первый блок 12 памяти). Старший разряд двоичного кода . г числа подается со второго выхода счетчика 1 на установочный вход первого триггера 5, а остальные разряды кода с первого выхода счетчика 1 преобразуются далифратором 2в соответствии с (1), чем обеспечивается выбор j-ой схемы формирователя 3 адреса. Первый код номера k, формируемый j-ой схемой подается с выхода формирователя 3 адреса на второй вход первого блока 12 памяти и организуется считывание с адреса k коэффициента спектра мощности Фурье с последующей передачей его на второй вход блока 16 умножения. Одновременно код I: подается на вход второго блока 8 формирования дополнительного кода. Последний образует дополнительный код от числа ,- Km-- ... К -i , если первый триггер 5 находится в единичном состоянии, т.е. , или пропускает код числа k на выходы без измерений, если .

Аналогично работает первый блок 7 формирования дополнительного кода с той лишь разйицей, что формируемый первым триггером 5 оигнал является не только управляющим для этого .блока, но и информационным. Таким образом, на вторые выходы первого 7 и второго 8 блоков формирования дополнительного кода выдается (m-l) старших разрядов прямого и дополнительного кодов чисел г и k соответственно в зависимости от состояния первого триггера 5, т.е. значения разряда числа г. Выполненная операция адекватна процедуре восстановления инверсно-симметричной структуры матрицы Л|с.г: если , чему соответствует гт 1, то формируются индексы (п-г) и In-k), а противном случае индексы г и k остаются без изменения.

Далее выполняется анализ кодов k и г на четность. С этой целью на первые выходы первого 7 и второго 8 блоков формирования дополнительного кода коммутируются первые разряды формируемых кодов, над которыми выполняется операция логического умножения блоком элементов И 9. Результат операции записывается во второй триггер .6, единичное состояние которого определяет режим работы переключателя 10. Таким образом, анализ на четность идексов k и г обеспечивает обращение к одной из двух матриц А либо Аре I представлякнцих матрицу АКГ 3 упакованном виде, и хранящихся во втором 13 и третьем 14 блоках памяти

Формирование адреса элемента либо Ар{рсуществляется следующим образом.

Высокий логический уровень напряжния на втором входе переключателя 10 обеспечивает формирование на первом его-выходе (2т-3) - разрядного кода адреса в виде (3). Низкий логический уровень напряжения на втором входе переключателя 10 приводит к появлению на в.тором его входе (2т-3) разрядного кода вида (4). В табл.2 и 3 представлены адресации матриц и Аре, во втором 13 и третьем 14 блоках памяти соответственно, для п , .

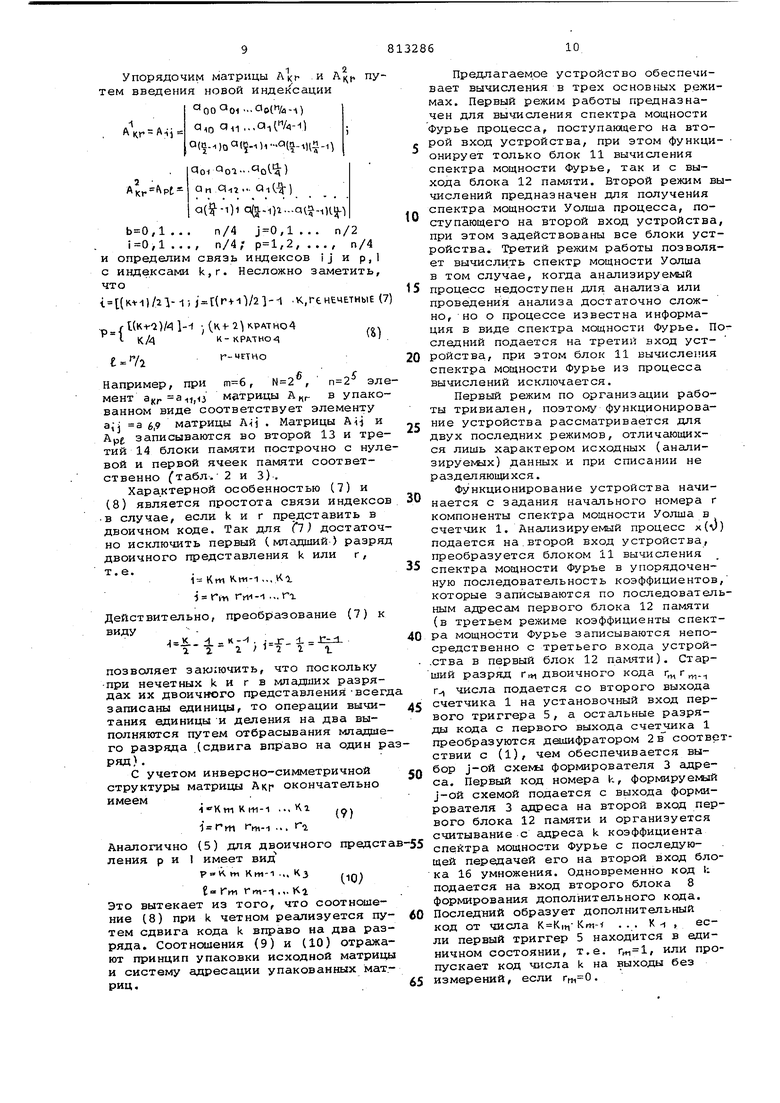

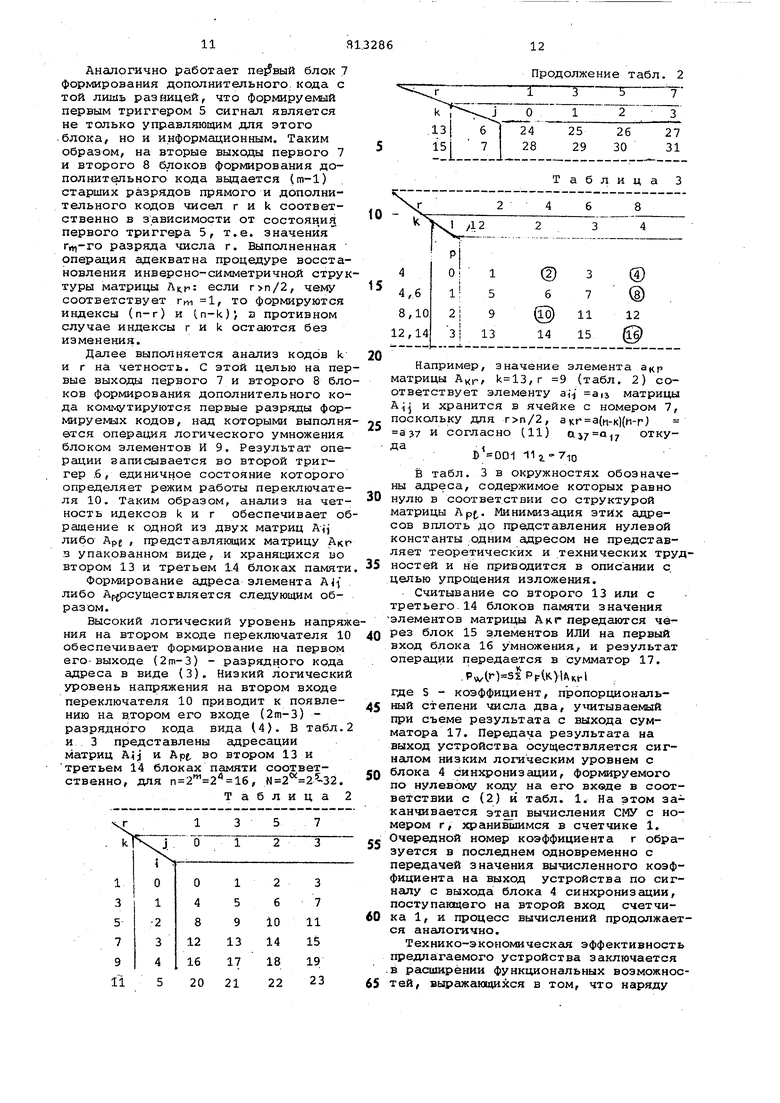

Таблица 2

Продолжение табл. 2

Таблица

Например, значение элемента акр матрицы Aj,, ,r 9 (табл. 2) соответствует элементу 30 матрицы и хранится в ячейке с номером 7, поскапьку для , (ц-к)(и-г} а 37 и согласно (11) отку да

D 001 11 г 710

в табл. 3 в окружностях обозначены адреса, содержимое которых равно нулю в соответствии со структурой матрицы Ар{,. Минимизация этих адресов вплоть до представления нулевой константы одним адресом не представляет теоретических и технических трудностей и не при-водится в описании с. целью упрощения изложения.

Считывание со второго 13 или с третьего.14 блоков памяти значения -элементов матрицы Акг передаются чёQ рез блок 15 элементов ИЛИ на первый вход блока 16 умножения, и результат операции передается в сумматор 17.

,Pvv/l )S PFlK-) где S - коэффициент, пропорционапь5 ный степени числа два, у штываемый при съеме результата с выхода сумматора 17. Передача результата на выход устройства осуществляется сигналом низким логическим уровнем с

Q блока 4 синхронизации, формируемого по нулевому коду на его входе в соответствии с (2) и табл. 1. На этом заканчивается этал вычисления СМУ с номером г, хранившимся в счетчике 1, Очередной номер коэффициента г образуется в последнем одновременно с передачей значения вычисленного коэффициента на выход устройства по сигналу с выхода блока 4 синхронизации, поступаюцего на второй вход счетчи0 ка 1, и процесс вычислений продолжается аналозгично.

Технико-экономическс1Я эффективность предлагаемого устройства заключается .в расширении функциональных возможнос5 тей, выражающихся в том, что наряду с возможностью получения СМФ устройство обеспечивает вычисление СМУ как непосредственно по процессу, так и по известной характеристике о нем в виде СМФ, существует 1возможность вычисления отдельных, заданных и существенных при решении конкретной за дачи коэффициентов СМУ, в упрощении получения СМУ за счет возможности вы числения его по известному СМФ. В сокращении вычислений СМУ по из вестному СМФ за счет хранения матриц ядра преобразования з памяти, т.е. элементы матрицы не вычисляются/ упа ковки матрицы ядра преобразования, чем достигается сокращение объема памяти и количества циклов считывания информации , вычисления отдельных заданных и существенных при решении конкретной задачи коэффициентов СМУ. Формула изобретения Устройство для спектрального анализа, содержащее счетчик, первый -вхо которого является первым входом устройства, первый выход счетчика подключен ко входу первого триггера, блок вычисления спектра мощности Фурье, вход которого является вторым входом .устройства, а выход соединен с первым входом первого блока памяти второй вход которого является третьим входом устройства, отличаю щееся тем, что, с целью расшире ния функциональных возможностей за счет получения спектра метцности Уолша, в устройство введены дешифратор, формирователь, адреса и блок синхрони зации, два блока памяти, два блока формирования дополнительного кода. блок элементов И, второй триггер, блок элементов ИЛИ, переключатель it блок умножения, входы которого подключены соответственно к выходу первого блока памяти и к выходу блока элементов ИЛИ, входы которого подключены соответственно к первому и второму выходам переключателя, входы которого соединены соответственно с выходом второго триггера, и с первым выходом первого и второго- блоков формирования дополнительного кода, вторые выходы которых соединены соответственно с первым и вторым входами блока элементов И, входы первого блока формирования дополнительного кода подключены соответственно к выходу счетчика и к выходу первого триггера, входы второго блока формирования дополнительного кода соединены соответственно с выходом формирователя адреса и с выходом первого триггера, третий вход первого блока памяти подключен к выходу формирователя адреса, вход второго триггера соединен с выходом блока элементов И, выход блока умножения соединен со вторым входом сумматора, первый вход которого соединен с выходом блока синхронизации, подключенным ко второму входу счетчика, выход дииифратора соединен со входом формирователя адреса, выход которого подключен ко входу блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 468246, кл. G 06 F 15/34, 1975. 2.Авторское свидетельство СССР № 532100, кл. G 06 F 15/34, 1976 (прототип)

Авторы

Даты

1981-03-15—Публикация

1978-06-19—Подача