(54) УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для спектральногоАНАлизА | 1978 |

|

SU813286A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Устройство для спектрального анализа | 1981 |

|

SU1013972A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU842829A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

.

Изобретение относится к области цифровой вычислительной техники и может быть использовано при создании. специализированных вычислительных устройств для спектрального анализа процессов и сигналов, вычислительно-моделирующих комплексов для испытаний изделий на внешние воздействия, навигационных и радиолокационных систем cлeжieния и обнаружения, а также в системах распознавания и идентификации образов.

Известные устройства по принципу представления сигналов и процессов в спевдгральной области можно разделить на две группы: устройства, принцип работы которых основан на разложении сигналов в системе функций Уолша 1 и устройства, работающие в системе тригонометрических функций 2.

Однако существенным недостатком первых устройств является нетшшчность формируемой спектральной характеристики, t.e. она отличается от той же характеристики в системе тригонометрических функций. Это затруд, а зачастую и исключает использование таких устройств для решения некоторых задач.

Таким образом; наиболее актуальной задачей практического спектрального анализа является повыщение быстродействия получения спектральных характеристик сигналов. в системе тригонометрических функций.

Наиболее близким по технической сущности к изобретению (прототипом) является устройство 12, содержащее блок вычисления корреляционной функции, сумматор, два переключателя, блок памяти, блок вычисления спектра

10 мощности Фурье, счетчик, триггер и соответствующие связи. Данное устройство обеспечивает вь1числение спектра мощности Фурье через корреляционную функцшо.

Основным недостатком его является низкое

15 быстродействие, обусловленное прежде всего принципом работы, лоложенньт в его основу. Устройство принципиально не позволяет реа- лизовать схему вь1числений спектра мощности Фурье через спектр мощности Уолша.

20

Устранение этого недостатка требует значительных затрат аппаратных средств, что повышает стоимость,оборудования, габаритов, энергозатрат, даже с применением современной элементной базы. Есть ряд задач, для решения которых не приемлемы известные устройства и требуются специальные меры по распараллеливанию процесса вычислений.

Второй недостаток заключается в том, что устройство не позволяет решить ряд задач в условиях, когда исходный (анализируемый) процесс недоступен для анализа, но его характеристики известны априори и заданы в виде спектра мощности в одной из базисных систем функций.

Примером таких объектов могут быть летательные аппарать, сейсмические объекты, и т.д., для которых .целесообразно не записывать анализируемый процесс с последующей передачей по каналам сйязи на пункты обработки, а обрабатывать его по мере поступления. Для объектов, работающих в реальном масштабе времени такая обработка может быть эффективно проведена в системе функций Уолша С другой стороны, известна тенденция синтеза устройств, обработки информации в системе функций Уолша, настройка, управление которых затруднительны в связи с необходимостью получения спектральных характеристик Уолша, при этом априори известны те же характеристики в системе тригонометрических функций. Решение задачи настройки таких устройств . по Известным спектральным характеристикам в системе тригонометрических функций существенно расширило бы область применения и эффективность их использования.

Третий недостаток обусловлен тем, что известные устройства, реализованные по наиболее эффективным методам быстрых преобразований, не обеспечивают вычисление отдельных, заданных и существенных при решении конкретной задачи компонент (коэффициентов) спектра мощности Фурье или Уолша, что привдит к необходимости заранее на этапе проектирования вносить аппаратурную избыточность.

Целью изобретения является расширение класса решаемых задач и повышение быстродействия. Для достижения поставленной цели в устройство, содержащее счетчик, первый блок памяти, коммутатор, первьш триггер, сумматор, при этом выход счетчика соединен с первым входом первого блока памяти, второй вход которого является первым входом устройства, первый вход коммутатора является вторым входом устройства, а выход сумматора является выходом устройства, введены регистр, дешифратор, два блока формирования дополнительного кода, второй и третий блоки памяти, второй триггер, блок умножения, элемент И, элемент ИЛИ, первый вход которого соединен с выходом второго блока паШтй, вход которого подключен к первому выходу коммутатора, второй вход которого

соединен с первым выходом первого блока формирования дополнительного кода, второй Выход которого соединен с первым входом элемента И, выход которого соединен с третьим входом коммутатора, второй выход которого . подключен ко входу третьего блока памяти, выход котброго соединен со вторым входом элемента ИЛИ, выход которого подключен к первому входу блока умножения, выход которого подключен ко входу сумматора, первый выхЬд регистра подключен ко входу дешифратора и первому входу второго блока формирования дополнительного кода, первый выход которого соединен со вторым входом элемента И, второй выход регистра соединен со входом первого триггера, выход которого подключен к первому входу первого блока формиро)вания дополнительного кода и второму входу второго блока формирования дополнительного кода, второй выход которого соедине с четвертым входом коммутатора, выход децшфратора соединен со входом счетчика, выход которого соединен со вторым входом первого блока формирования дополнительного кода, а вход регистра является третьим входом устройства, при этом выход первого блока памяти соединен со вторым входом блока умножения.

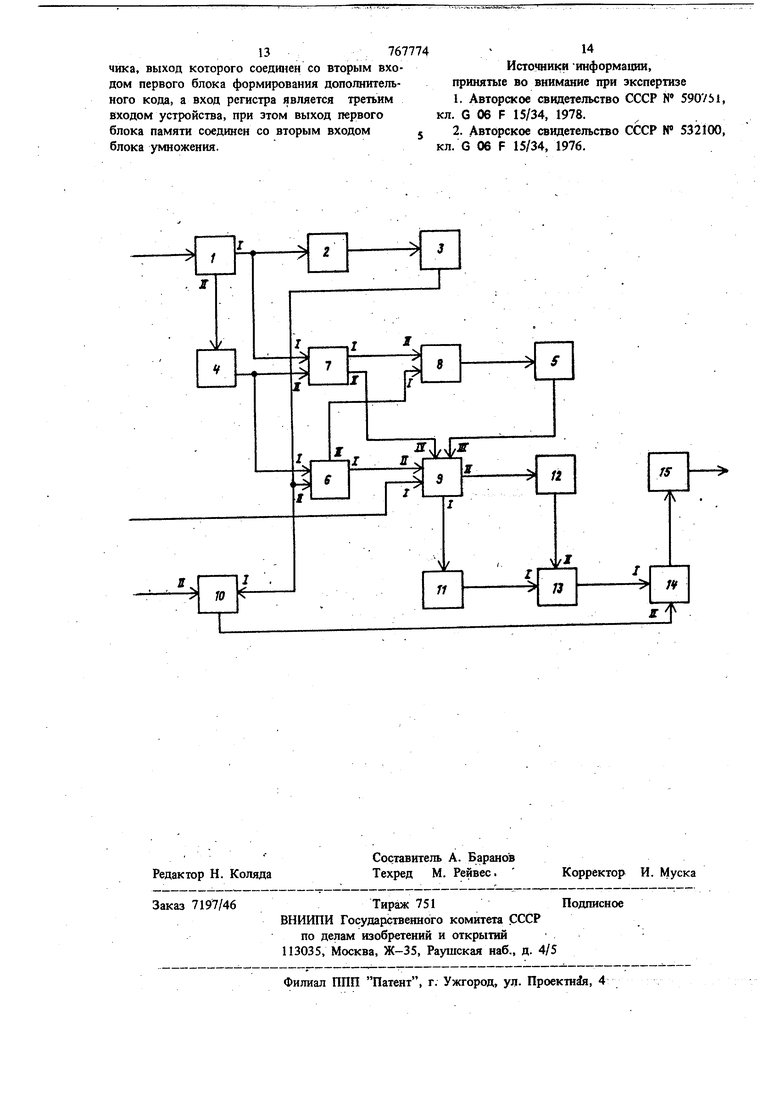

На чертеже представлена структурная схема устройства.

Устройство содержит регистр 1, дешифратор 2, счетчик 3, первый 4 и второй 5 триггеры, первый 6 и второй 7 блоки формирования . дополнительного кода, элементы И 8, коммутатЬр 9, первый 10, второй 11 и третий 12 блоки памяти, элемент 13 ИЛИ, блок 14 умножения, сумматор 15.

Рассмотрим основные функции, выполняемые каждым из структурных элементов устройства.

Регистр 1 предназначен для приема и хранения двоичного кода С|у к-л--- номера С вычисляемого коэффициента спектра мощности (при а --Y ,,а.--, N1-2.--1 - номер коэффициента спектра мощности Уолша, при а-1,,...Н|й-1 - номер коэффициента спектра мощности Фурье). . Разрядность регистра 1 опрёделйется максимальным номером пересчитываемых коэффициентов и равна vnt ogrt тое N количество отсчетов анализируемого процесса. Младшие разряды регистра 1 образуют первый его выход, а старший )7i -ый разряд CIjTi передается на второй выход. В процессе функционирования устройства номер вычисляемой спектральной, компоненты является также и номером цикла работы устройства.

Дешифратор 2 осуществляет управление работой счетчика 3 с управляемым интервалом пересчета путем преобразования .входного кода. номера спектральной компоненты по соотношению,, ----R -V 2a ®R - ,Н где vj if -1 - выходной (. v - -1) - разрядный двоичный код; R HuOi),.CA-lV - (. Ум - 1 ) - старших разрядов кода Грея соответственно от четных и нечетных номеров коэф фициентов спектра мощности (нри Си Г коэффициенты спектра мощности Уолша и при СХ К - коэффициенты спектра мошности Фурье). ° Счетчик 3 предназначен для формирования . адресов для первого 10, второго 11 и третьего 12 блоков памяти. Работа счетчика 3 организована с изменяемым интервалом счета, величина которого задается кодом на его входе. Состояние счетчика cldy. и у ... с| является также номером Такта работы устройства. Первый 4 и второй 5 триггеры предназначены для управления работой первого 6, второго 7 блоков формирования дополнительного кода и- коммутатора 9 соответственно. Первый триггер 4 соединен своим установочным входом со старшим разрядом С( уу, регистра 1; второй триггер 5 подключен установочным входом через элемент И 8 к первым (младшим разрядам кодов с выходов первого 6 и второго 7 блоков формирования дополнительного кода. Первый 6 и второй 7 блоки формирования дополнительного кода предназначены для преобразования в соответствии с управлягошими сигналами на первых входах поступаюших на вторые входы кодов в адреса для второго 11 и третьего 12 блоков памяти; старшие разряды сформированных кодов подаются на пер. вый и второй входы коммутатора 9, а первые разряды подключены ко входам элемента И 8. ;Получение дополнительного кода числа первым ;6 и 7 блоками формирования дополнительного кода может быть организовано по любому из известных методов. Элемент И 8 вьщолняет операцию логического умножения над первыми (младшими) разрядами кЬдов, формируемыми первым б и вторым 7 блоками формирования дополниTeJj iHoro кода. Коммутатор 9 выполняет коммутацию и группировку поступающих на первый и второй входы кодов в соответствии с управляющими сигналами на третьем и четвертом входах и обеспечивает тем самым формирование адресов для второго .1Ри третьего 12 блоков памяти. Первый блрк 10 памяти предназначен для приема со второго входа устройства и хранения коэффициентов спектра мощности Фурье или Уолша ( в зависимости от режима работы устройства). Коэффициенты располагаются . в памяти в естественном порядке, т.е. первьш коэффициент - в первой ячейке, второй во второй ячейке и т.д. Второй 11 и третий 12 блоки памяти предназначены для хранения матрицы ядра преобразования в, соответствии с принятой процедурой упаковки (адресации). В каждом из блоков памяти хранится часть матрицы ядра преобразования. Эти части матрицы упакованы (специально организованы с целью устранения холостых тактов и циклов работы устройства). Элемент ИЛИ 13 осуществляет передачу на выход информационного потока с первого или второго своегб входа. Блок 14 умножения выполняет перемножение поступающих на первый и второй входы чисел. Сумматор 15 выполнен в виде CTpyKTypbt накапливающего типа и обеспечивает алгебраическое сложение поступающих на вход операндов в течение всего цикла работы устройства. Перед началом каждого цикла сумматор 15 принимает нулевое состояние. Разрядность счетчика 3 равна Vrt -1 , т.е. совпадает с разрядностью формируемого дешифратором 2 кода. Количество различных кодов на выходе дешифратора 2 равно Уу.1.- Причем все коды отличаются друг от друга только номером разряда, в котором записана единица. Каждый такой код определяет интервал пересчета счетчика 3. Связь возможных состояний счетчика 3 и управляющего кода на входе вьхражае ся соотношением:2 -42eHXe42,.-:,(2J) где А - функционально связанная и определяемая параметром j последовательность состояний счетчика 3; j -т номер разряда двоичного управляющего кода, в котором записана единица je d,u ....«т- . Таким образом, каждому номе||у цикла работы устройства (а на выходе дешифратора 2 формируется фактически код номера цикла в преобразованном виде) соответствует пе- ременное количество тактов, номера которых задает счетчик 3. Так, например, если на вход счетчика 3 подается код О ... 01, то интервал пересчета-равен двум и номера тактов определяются нечетной последовательностью чисел до М)1 -1. Последний номер, равный нулю, является признаком окончания цикла. Такая структура счетчика 3 с управляемым интервалом пересчета допускает формализацию и синтез при помощи известных методов и дополнительного пояснения не требует. Коммутатор 9 выполняет группировку двух кодов, постзшающих. на первый и второй его входы, в один -- раз{5ядный двоичный КОД адреса, передаваемый затем на первый или второй выходы. Коммутатор 9 работает в четырех режимах Первый режим определяется низким логическим уровнем напряжения на четвертом вХр де и высоким уровнем напряжения на треть входе; В этом режиме выполняется группиров ка кодов, поступающих на первый и второй входы, в соответствии с выражением пС«)-Г, , Л . .v. где 1йум-1 - 32 1цЭ прямой или дополнитель ный код старших УУ -2 - разрядов двоичного представления прямого или дополнительного кода числа (номера такта) на втором входе; ау„....3 wi-2 - разряд; ный прямой или дополнительный код на перв входе, образованный от двоичного прямого или дополнительного кода числа 01 (номера цикла) путем исключения старшего СИуу, и младшего d-i разрядов;;. D - двоичный (2)-4) - разрядный код адреса, передаваемый на первый выхед. Например, для О 1, с1 - 1, 3, 5, 7; , 4, 8, 12. Второй режим определяется низким логичес ким уровнем напряжения на четвертом и . третьем входах. В зтом режиме выполняется группировка; кодов, поступающих на первыйи второй входы в cooтвeJCтвии с выражением .-...... „ Щ( разрядный двоичный код адреса, передаваемый на второй выход, а остальные обозначения адекватны выражению (3). Например, для , d - 2, 4, 6; ; , 5, 5. Третий режим коммутатора 9 обебпеШй)аётСя высокими логическими уровнями напряжений на третьем и четвертом входах, при этом струк тура передаваемого на первый выход (2)т1-4) разрядного кода X)i имеет вид 1- Зти уп-а- 2 Например, для, Q-l, О « 1, 3, 5, 7; - О, 1, 2, 3. Ив четвертом режиме, задаваемом высоким логическим уровнем на четвертом входе и низким уровнем на третьем входе, коммутатор 9 обеспечивает формирование (2 m -4) - азрядного кода адреса D Са) на втором свом выходе в соответствии с выражением 4-{«.v..a-«.L .--°5 j апример, для , , 4, б, 8; , 2, Конструктивно коммутатор 9 представляет собой логическую комбинационную схему, которая может быть синтезирована .согласно формулам (3)-(6) по известным методам. Устройство функционирует в двух режимах: первый режим обеспечивает вычисление спектра мощности Уonnia цо известному спектру мощности Фурье (высокой логический уровень напряжения на третьем входе), а второй - позволяет получить спектр мощности Фурье по известному спектру мощности Уолша (низкий логический уровень нахфяжения на третьем входе). Рассмотрим работу устройства в первом режиме, для чего на третий его вход подается уровень логической едини1ц 1. Предваритель но во второй блок 11 записываются элементы матрицы вида Hia и:91,-- i-ои,---,и|4, в третий блок 12 памяти записывается мат-: ица о h 14а,, .- i(rt-+-) иИ-чМ (4-Л2---(.и14-1 |4P--0,i,...,h|4-f/e-0,f,:;.., Матрицы Aij и Apg располагаются во втоом 11 и третьем 12 блока памяти построчно, ачиная с нулевой и первой ячеек памяти оответственно. Элементы матрицы А СЧрС. матрицы At)g .равны 1 L:.-, -и IE 5iv co5||,) o 1,.C2o®.,v-, )-f,2,..,,N|2Hj е (,2,...,N12-15 где О ) -I- -ый разряд кода Грея, а связь индексов IC и f с- индексами 1,j и р,С определяется в виде 1-- ) ,у,е иемет-, (10) 3 Cr-vtlfi -Ч.(.kviV кратно 4, , -Кратно 4, (И) ., V« 5,. W 2 Например, при элемент 19,1 г соответствует элементу алгс|(, ятпмш т А - матрицы А Далее, в регистр I заносится с первого вхо да устройства номер 1г вычисляемой компоненты спектра мощности Уолша, а со второго входа устройства в первый блок 10 памяти . записываются N/2-1 компонент спектра мощности Фурье. Старщий разряд VVY, двоичного кода wi п)-/1-xi числа V подается со второго вь1хода регистра 1 на установочный вход первого триггера 4, а остальные разряды кода V с первого выхода регистра 1 преоб разуются дешифратором 2 в соответствии с формулой (l) ;R 42-V- ®Vl(irvl),4eM к обеспечивается задание интервала пересчета счетчика 3 и его запуск. Состояние счетчика 3 ( с его выхода передается на второй вход первого блока 10 памяти и определяет адрес. ячейки памяти, с которой считывается коэф фициент спектра мощности Фурье с последующей передачей его на второй вход блока 14 умножения. Одновременно код U передается на второй вход второго блока 7 формировани дополнительного кода. Последний образует дополнительный код от числа V...- К, если первый триггер 4 находится в единичном состоянии, т.е. - 1, или передает на вь1ходы код /k без изменений, если первый триггер 4 находится в нулевом состоянии (Гуп 0). Аналогично работает и первый блок 5 формирования дополнительного koдa, но сиг нал на первом его входе от первого триггера является не только управляющим, но и инфор мационным. Таким образом, на вторые выходы первого б и второго 7 блоков формирования дополнительного кода передается wi-1 старщих разрядов прямого или дополнительного кодов чисел ) и V. соответственно. Далее выполняется анализ кодов k и 1Г на четность. С этой целью на первые выходь первого 6 и второго 7 блоков формирования дополнительного кода выведены первые разряды формируемых кодов, над которыми вы4.10 полняется операция логического умножения элементом И 8. Результат операции записывается во второй триггер 5, состояние которого определяет режим работы коммутатора 9. В основу данных операций положены свойства соотношений (10) и (11). заключающиеся в следующем. Связь индексов i,;} и К,Г в (10) для их двоичного представления выражается в виде w-1--- 2. а индексы р,б и 1,У согласно (II) находятся P- wy w-r-в зависимости;.. . . а 1 ормирование адреса элемента )j либо dpt осуществляется следующим образом. Высокий логический уровень напряжения на третьем входе Коммутатора 9 обеспечивает формирование на первом его выходе (2 Ум -4) разрядного кода адреса в виде выражения (3). V-byn-r- alv gkn- ulltt . Низкий логический уровень напряжения на третьем его входе приводит KJ группировке ( К у„ -4) - разрядного кода на втором выходе в виде выражения 4: f i w M- Un9lrv«-- U Например, значение элемента Ьс матрицы AVJ, V 13, у 9, соответствует элементу ci А с о, матрицы А и хранится в ячейке с номером 7 второго блока 11 памяти, так как Гуу, для двоичного представления у-. равно единице, определяя тем самым режим работы коммутатора 9 в виде вьфажения (3) и режим формирования дополнительного кода первым 6 и вторым 7 блоками формирования дополнительного кода. Следовательно .on-t on-V0 2-. ; . ,on--t on-oW2 Тогда на первом выходе коммутатора 9 бразуется адрес (3), из дополнительного кода ,, г 7 Разрядность полученного адреса равна четырем, . оскольку W - 4 к 2. 4 (vv -Eog, Считаге1ые со второго 11 и с третьего 12 блоков памяти значения матрицы А либо о передаются через элемент 13 ИЛИ на ервый вход блока 14 умножения, и результат перащта далее посылается в сумматор 15 наап1шваюшег,о типа, выход которого описывактся соотношением v.v) IlPpW|Ay |, где S - коэффициент, пропорциональный степени числа два, учитываемый при съеме результата с выхода сумматора 16. Второй режим работы устройства обеспечивается подачей низкого логического уровня напряжения на третий вход. Функционирование устройства в этом режиме отличается только характером группировки кодов коммутатора 9 Так, для принятых обозначений, в регистр 1 записывается номер V вычисляемой компоненты спектра мощности Фурье, .имеющий одновременно смысл иомера цикла работы уст ройства, в первый блок 10 памяти записываются N/2-1 компонент спектра мощности Уолша, а характер исходных данных, вводимы во второй 11 и третий 12 блоки памяти, остается аналогичным первому режиму, т.е. определяется матрицами (7) и (8), элементы которых вычисляются согласно (II) при соотношениях индексов (10) и (11), старшие разрядов кода К V yyi-i-.-Xv( с выхода регис ра 1 передаются на вход дешифратора 2 и преобразуются согласно (1) к виду ,,wM ..(w.iV(©RH-A 2.l, определяя тем самым интервал пересчета счет чика .3 и его запуск. Состояние у счетчика 3 обеспечивает адресацию первого блока 10 . памяти, а в момент изменения его состояния происходит считывание коэффициента спектра МОЩНОСТИ Уолща из ячейки Y первого блока 10 памяти и передача его на второй вход блока 14 умножения. Условие преобразования кодов ,...1(я иУ---Гуу,,.-.Уд первымб и вторым 7 блоками формирования дополнительного кода соответственно аналогичны первому режиму работы устройства. Форми рование адресов для второго И и треть о 12 блоков памяти осуществляется коммутатором 9 в.соответствии с выражениями (5) и (6): ъ tvtv-i%-Q. ,M--, соответственно в зависимости от управляющего сигнала на третьем его входе. Таким образом, принципиальное отличие второго режима работы устройства от первого заключается в организации такой группировки кодов k и V коммутатором 9 при помопш упр ляющего сигнала на четвертом его входе, которая обеспечивает формирование последовательности функционально связанных адресов вида 0,l,..v, И /4-1 для второго блока 11 памяти и вида 1,2,... и/4 для третьего блока 12 памяти. Выхо.ч сумматора 15 при этом описывается формулой , где )Д)- транспортированная матрица |Ai f-|Оба режима работы устройства описаны для случая вычисления одной, заданной в регистре 1 своим номером Н или спектральной компоненты. Для вычисления другой компоненты в регистр I с первого входа устройства записывается соответствующий номер и вычисления повторяются аналогично. Формула изобретения Устройство для спектрального анализа, содержащее счетчик, первый блок памяти, коммутатор, первый триггер, сумматор, при этом вь1ход счетчика соединен с первым входом первЪго блока памяти, второй вход которого является первым входом устройства, первый вход коммутатора является вторым входом устройства, а выход сумматора является выходом устройства, отл ичающееся тем, что, с целью увеличения быстродействия и расширения класса решаемых зада-ч в негр введены регистр, дешифратор, два блока формирования дополнительного кода, второй и третий блоки памяти, второй триггер, блокумножения, элемент И, элемент ИЛИ, первый вход которого соединен с выходом второго блока Памяти, вход которого подключен к первому выходу коммутатора, второй вход которого соединен с первым выходом первого блока формирования дополнительного кода, второй выход которого соединен с первым входом элемента И, выход которого соединен с третьим входом коммутатора, второй выход которого подключен ко входу tpeTbero блока памяти, выход которого соединен со вторым входом элемента ИЛИ, выход которого подключен к первому входу блока умножения, выход которого подключен ко входу сумматора, первый выход регистра подк.пючен ко входу дешифратора и первому входу второго блока формирования дополнительного кода, первый вход которого соединен со вторым входом элемента И, второй выходрегистра соединен со входом первого триггера, выход которого подключен к первому входу первого блока формирования дополнительного кода и второму входу второго блока формирования до полнительного кода, второй выход которого соединен с четвертым входом коммутатора, вь1Ход дешифратора соединен с6 входом СЧР13767774

чика, выход которого соединен со вторым входом первого блока формирования дополнительного кода, а вход регистра является третьим входом устройства, при этом выход первого блока памяти соединен со вторым входом блока умножения.

14

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-09-30—Публикация

1978-07-31—Подача