(54) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления помех | 1988 |

|

SU1628193A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1992 |

|

RU2096920C1 |

| Устройство для синхронизации импульсов | 1979 |

|

SU871322A1 |

| Селектор сигналов | 1989 |

|

SU1732451A1 |

| Устройство для приема дискретной информации | 1991 |

|

SU1783632A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1709549A1 |

| Реле времени | 1988 |

|

SU1531196A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство преобразования последовательности прямоугольных импульсов напряжения | 1989 |

|

SU1721809A1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

изобретение относится к импульсной технике, в частности к формирователям импульсов с подавлением кратковременных помех, и может быть использовано в вычислительной технике и автоматике.

Известно устройство для подавления помех, содержащее два триггера, синхронизирующий вход первого . триггера подключен к шине тактового сигнала, нулевой вход - к шине логической а единичный выход соединен с единичным и синхронизирующим входами второго триггера, нулевой вход которого подключен к шине логического О, а нулевой выход соединен с единичным входом первого триггера, раздельные установочные в О входы обоих триггеров подключены к входной шине, одиночный выход второго триггера является выходом устройства 1.

Однако это устройство подавляет только положительные импульсы помех, длительность которых не превышает периода тактового сигнала. Ввиду асинхронности входного и тактового сигналов относительная по решность измерения этим устройством импульса помехи ±100%.

Наиболее близким по технической сущности к изобретению является устройство для подавления положительных и отрицательных импульсов помех,.имеющих определенную длительность. Это устройство содержит п- разрядный регистр сдвига, пороговый элемент, .ин-; вертор, четыре элемента И-НЕ и два синхронных D-триггера. Входная шина

10 через пороговый элемент соединена со входом п-разрядного регистра сдвига, состоящего из п триггеров, единичные и нулевые выходы триггеров первого и п-ого разрядов регистра сдвига

15 соединены со входами первого и второго элементов И-НЕ соответственно, выходы которых соедннены с информационными D-входами первого и второго О-триггеров соответственно, еди- .

20 ничные выходы которых соединены с первыми входами третьего и четверто о элементов И-НЕ соответственно, вторые входы которых соединены с вьк ходами четвертого и третьего элементов И-НЕ соответственно, шина тактового сигнала соединена с синхронизирующими входами триггеров п-разрядного регистра сдвига и через инвертор с синхронизирующими входами О-триг30 repOB jt2j..

Недостаток устройства заключается в том, что устройством не подавляются помехи, у которых значение автокорреляционной функции для интервала корреляции - (п-1) периодов тактовой частоты не равно нулю, что ограничивает его функциональные возможности в подавлении помех. .

Целью изобретения является обеспечение подавления помех заданной длительности независимо от их взаимного временногорасположения,

, Поставленная цель достигается тем, что в устройство для подавления помех, содержащее регистр сдвига синхронизирующий вход которого подключен к шине тактового сигнала,- пороговый элемент, вход которого подключен к входной шине, а выход - к информационному входу регистра сдви- га, введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к выходу порогового элемента, а второй вход - к инверсног гу выходу последнего разряда регистра сдвига, причем входам параллельной записи регистра сдвига объединены и подключены к выходу его последнего разру.да, а стробвход - к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.,

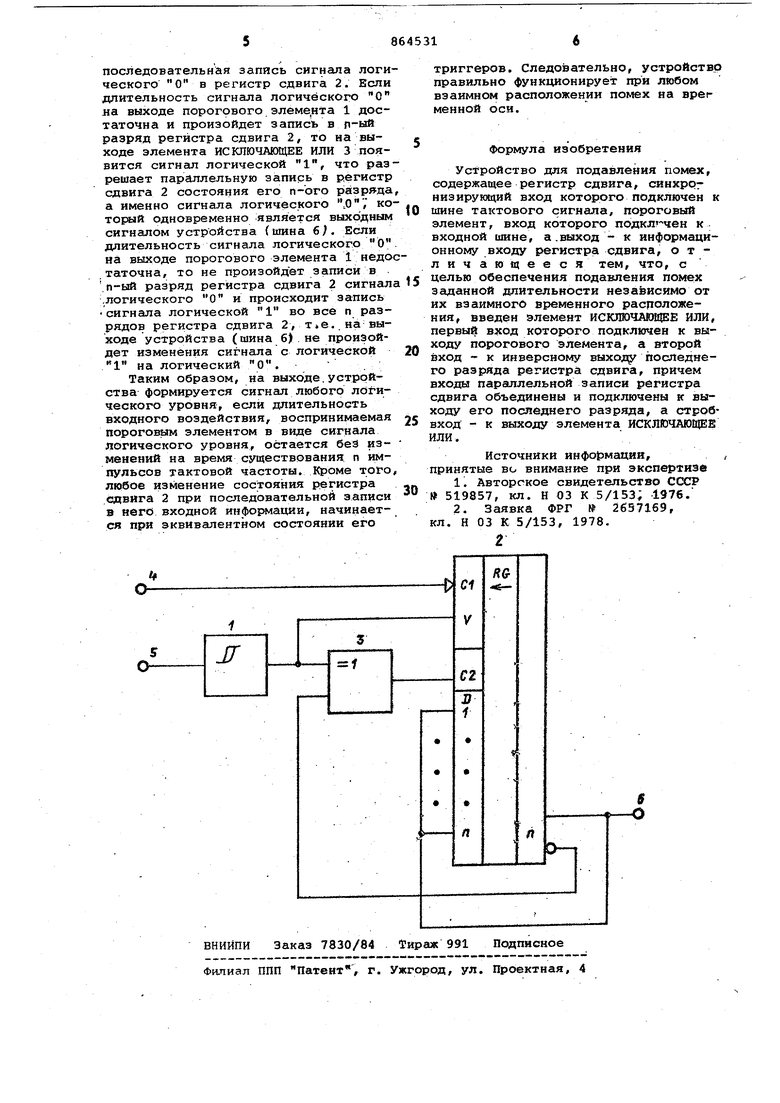

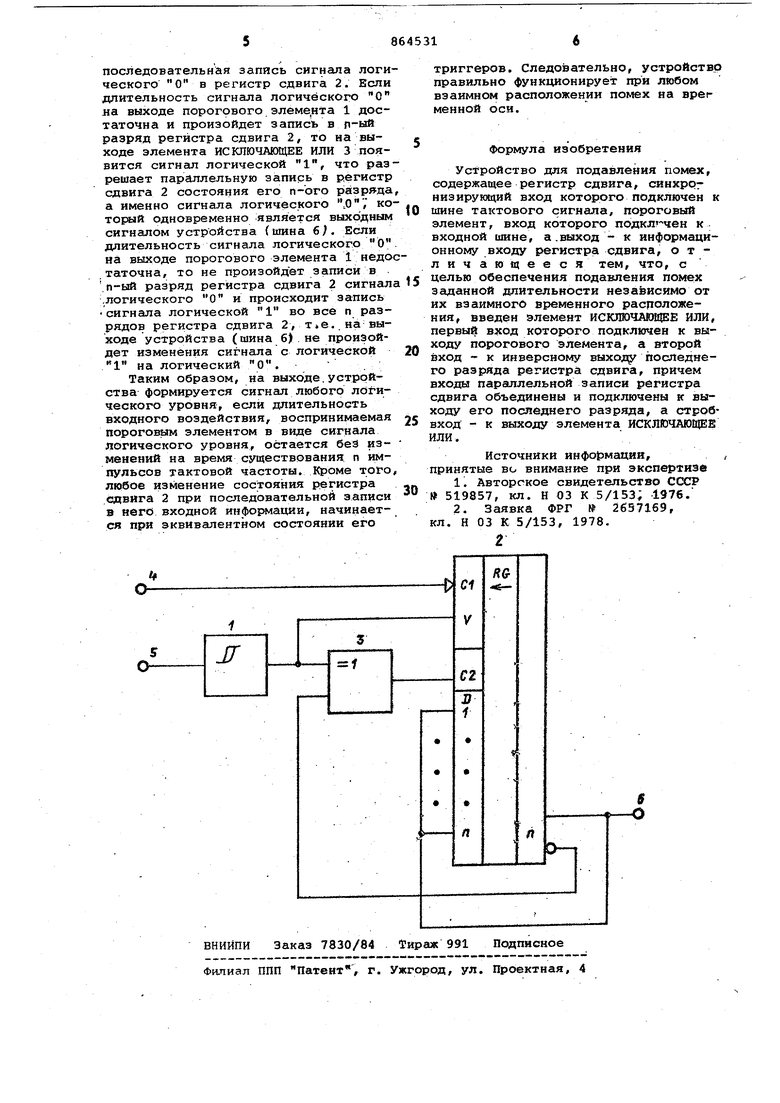

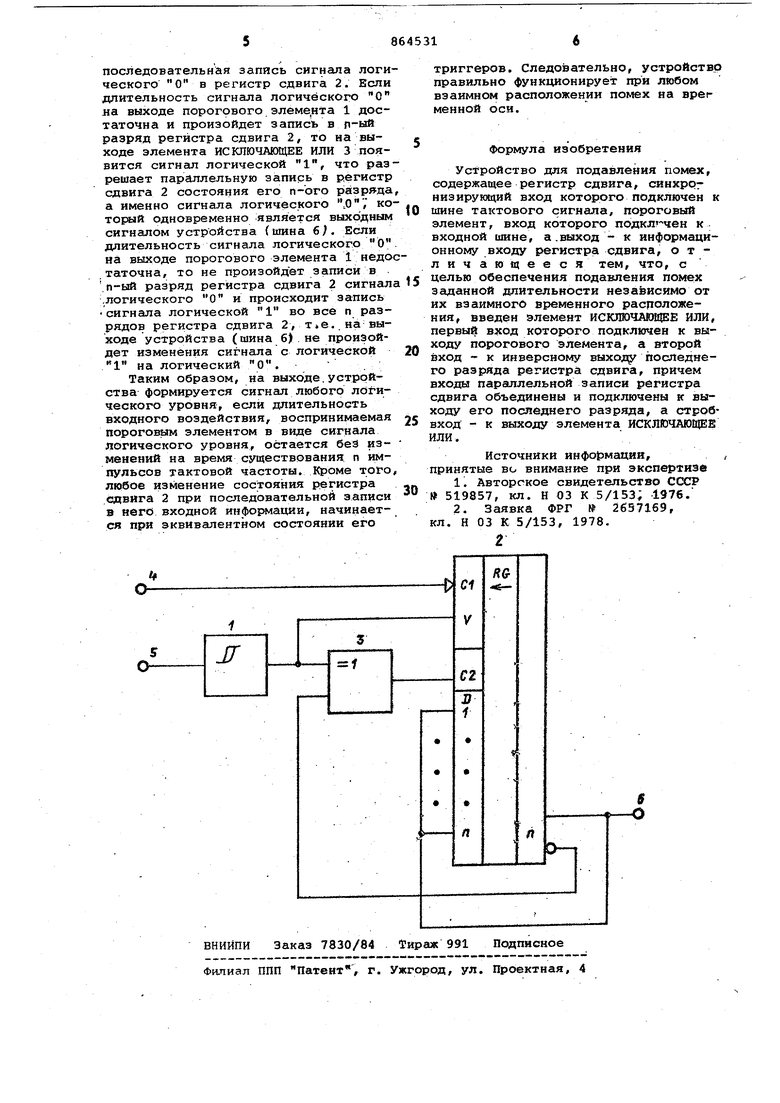

На чертеже представлена функциональная схема устройства для подавления помех.

Устройство содержит пороговый элемент 1, регистр сдвига 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, шину 4 тактовых импульсов, входную 5 и выходную б шины, причем вход порогового элемента 1 соединен с входной шиной 5, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3. подключен к выходу порогового эле мента 1 и к информационному входу регистра сдвига 2, информационные входы параллельной запкск информации ивыход п-ого разряда которого объединены и подключены к выходной шине 6, а инверсный выход - ко BTOpOf y входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, выход которого подключен к строб-входу параллельной записи информации регистра сдвига 2, синхронизирующий вход которого подключен к шине 4 тактовых импульсов.

Пусть в исходном состоянии на входной шине 5 устройства присутствует сигнал, который воспринимается пороговым элементом 1 в виде сигнала логического О. Этот сигнал поступает на информационный вход регистра сдвига 2 и на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3. Если на выходе П-ого разряда регистра сдвига 2 имеется сигнал логический О, т.е. сигнал логический 1 на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, то на выходе последнего -присутствует сигна логическая 1, который поступает на строб-вход регистра сдвига2 и записывает сигнал логический О во все

п разрядов регистра сдвига 2 параллельно. Если теперь произойдет изменение входного сигнала (шина 5} таки образом, что на выходе порогового элемента 1 появится сигнал логическая 1, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 пропадет сигнал логичецкая Ч,т.е. прекратится параллельна запись в регистр сдвига 2 состояния его п-ого разряда. С каждым импульсо такта (шина 4) происходит последовательная запись сигнала логической в регистр сдвига 2. Если длительность сигнала логическая 1, на выходе порогового элемента 1 достаточна и произойдет запись в п-ый разряд регистра сдвига 2, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 появится сигнал логическая 1, -что разрешает параллельную запись в регистр сдвига 2 состояния его п-ого разряда а именно сигнала логическая 1, который одновременно является выходным сигналом устройства (шина 6), Если длительность сигнала логическая 1 на выходе пороговогЪ элемента 1 «недостаточна,то не произойдет запись в VI-ый разряд регистра сдвига 2 сигнала логической 1 и происходит за,пись сигнала логического О вв все

h разрядов регистра сдвига 2,т.е. на выходе устройства не произойдет изменение сигнала с логического О на логическую 1 (шина 6).

Таким образом, на выходе устройства формируется выходной сигнал логическая 1, если длительность входного воздействия, воспринимаемая пороговым элементом в виде сигнала логическая 1, остается без. изме- . нений на п импульсов тактовой частоты.

Пусть теперь в исходном состоянии на входной шине 5 устройства присутствует сигнал, который воспринимается пороговым элементом 1 в виде сигнала логической 1. Этот сигнал поступает на информационный вход регистра сдвига 2 и на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3. Если на выходе п-ого разряда регистра сдвига 2 имеется сигн-ал логическая , т.е. сигнал . логический О на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, то на выходе последнего присутствует сигнал логическая 1, который Поступает .на строб-вход регистра сдвига 2 и запибывает сигнал логическая 1 во все п разрядов регистра сдвига 2 параллельно. Если теперь произойдет изменение входного сигнала ( шина 5) таким образом, что на выходе порогового элеэлемента 1 появится сигнал логический О, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 пропадет сигнал логическая 1, т.е. прекратится параллельная запись в регистр сдвига 2 состояния его п-ого разряда. С каждым импульсом такта ( шина 4 ) происходит последовательная запись сигнала логи ческого О в регистр сдвига 2. Воли длительность сигнала логического О на выходе порогрвого элеме,нта 1 достаточна и произойдет запись в п-ый разряд регистра сдвига 2, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 появится сигнал логической 1, что раз решает параллельную запись в регистр сдвига 2 состояния его п-ого тразряца а именно сигнала логического ,, ко TOf«tt одновременно является выходным сигналом устройства (шина 6), Если длительность сигнала логического О на выходе порогового элемента 1 недо .таточна, то не произойдет записи в . п-ый разряд регистра сдвига 2 сигнал .логического О и происходит запись сигнала логической 1 во все п разрядов регистра сдвига 2, ..на-выходе устройства (шина 6) не произойдет изменения сигнала с логической 1 на логический О. Таким образом, на выходе,устройства формируется сигнал любого логического уровня, если длительность входного воздействия, воспринимаемая порогоиим элементом в виде сигнала логического уровня, остается без изменений на время существования п импульсов тактовой частоты. Кроме TOfo, любое изменение состояния регистра едвнга 2 при последовательной записи э него входной информации, начинается при эквивалентном состоянии его триггеров. Следовательно, устройство правильно функционирует при любом взаимном расположении помех на врег менной оси. Формула изобретения Устройство для подавления помех, содержащее регистр сдвига, синхронизирующий вход которого подключен к шине тактового сигнала, пороговый элемент, вход которого подключен к входной шине, а.выход - к информационному входу регистра сдвига, отличающееся тем, что, с целью Обеспечения подавления заданной длительности независимо от их взаимного временного расположения, введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первы вход которого подключен к выходу порогового элемента, а второй вход - к инверсному выходу;- последнего разряда регистра сдвига, причем входы параллельной записи регистра сдвига объединены и подключены к выходу его последнего разряда, а стробвход - к выходу элемента ИСКЛЮЧАЮЩЕЕ ЛИ.. ч Источники инфо|)мация, , ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 519857, кл. Н 03 К 5/153; 1976. 2.Заявка ФРГ № 2657169, л. Н 03 К 5/153, 1978.

Авторы

Даты

1981-09-15—Публикация

1979-11-13—Подача