VI

ю

00

о ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

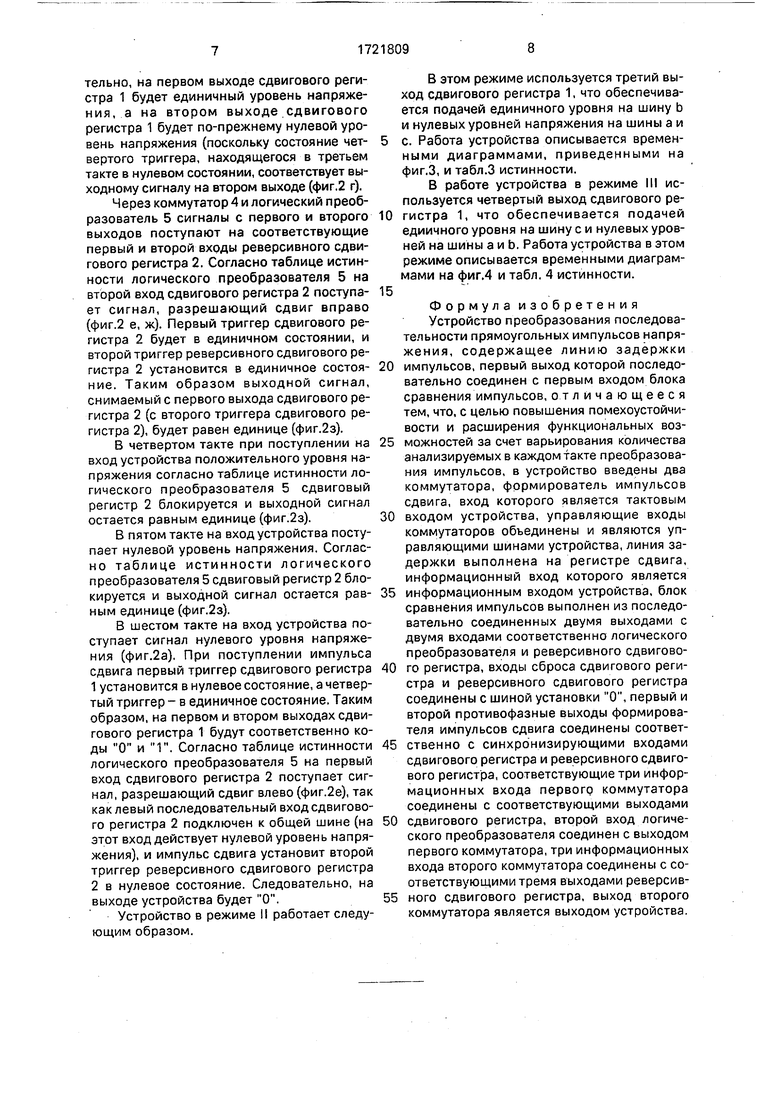

Изобретение относится к импульсной технике и может быть использовано для подавления помех в цифровых трактах после аналого-цифрового преобразования. Цель изобретения - повышение помехоустойчивости преобразования и расширение функциональных возможностей устройства за счет варьирования количества анализируемых в каждом такте преобразования импульсов. Поставленная цель достигается тем, что в устройство введены формирователь импульсов сдвига 3 и два коммутатора 4. Линия задержки выполнена на регистре 1 сдвига. Блок сравнения импульсов выполнен из последовательно соединенных двумя выходами с двумя входами соответственно логического преобразователя 5 и реверсивного сдвигового регистра 2, что позволяет улучшить качество измеряемой или передаваемой информации. 4 ил., 4 табл. Вылод -г Ё

Уст.О а Ь с

Шина управле/н gj

Изобретение относится к импульсной технике и может быть использовано для подавления помех в цифровых трактах после аналого-цифрового преобразования.

Цель изобретения - повышение помехоустойчивости преобразования и расширение функциональных возможностей за счет варьирования количества анализируемых в каждом такте преобразования импульсов.

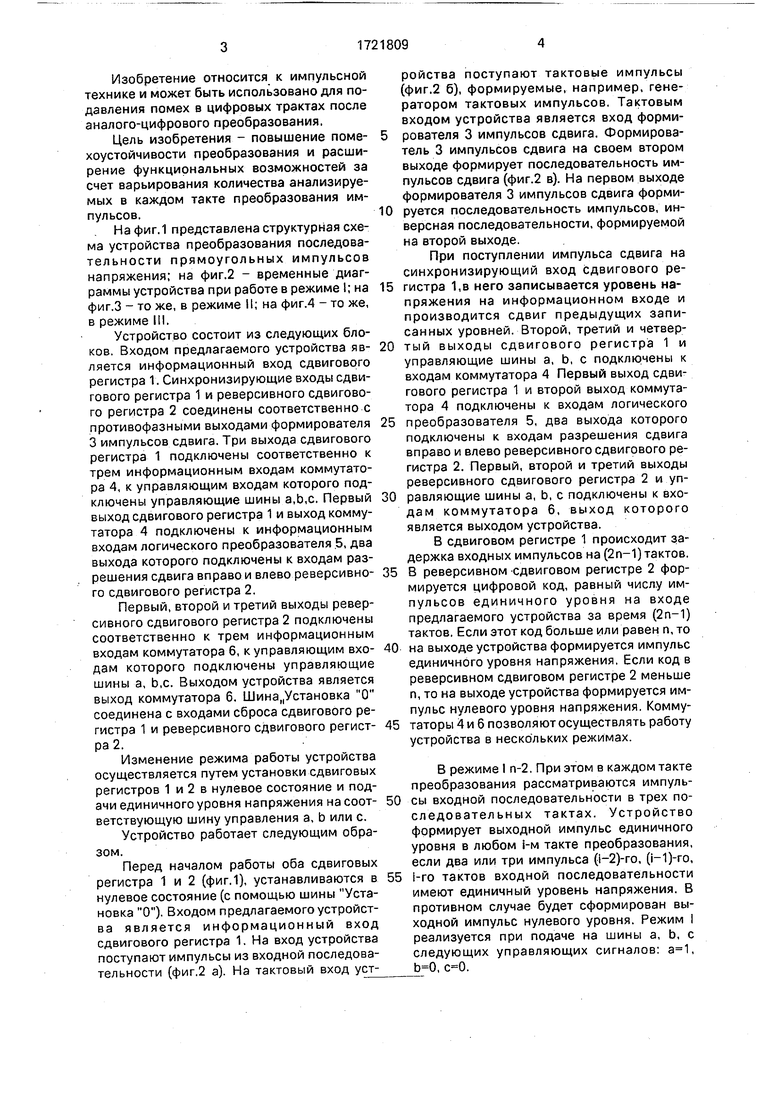

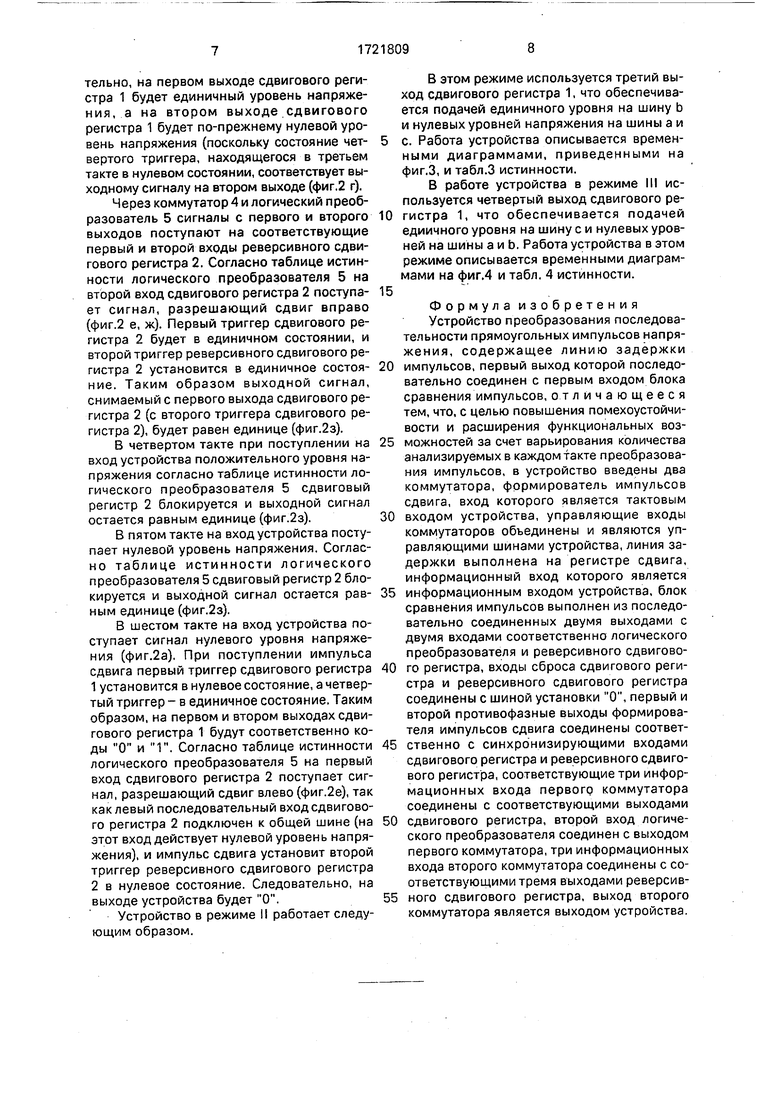

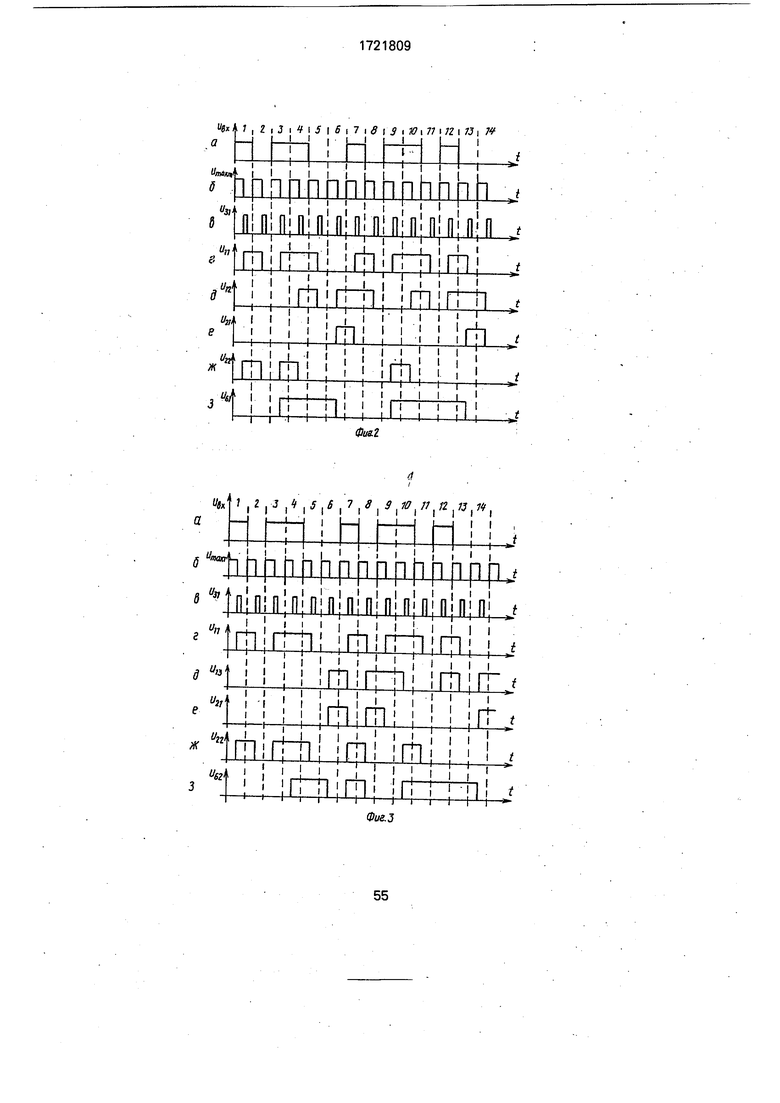

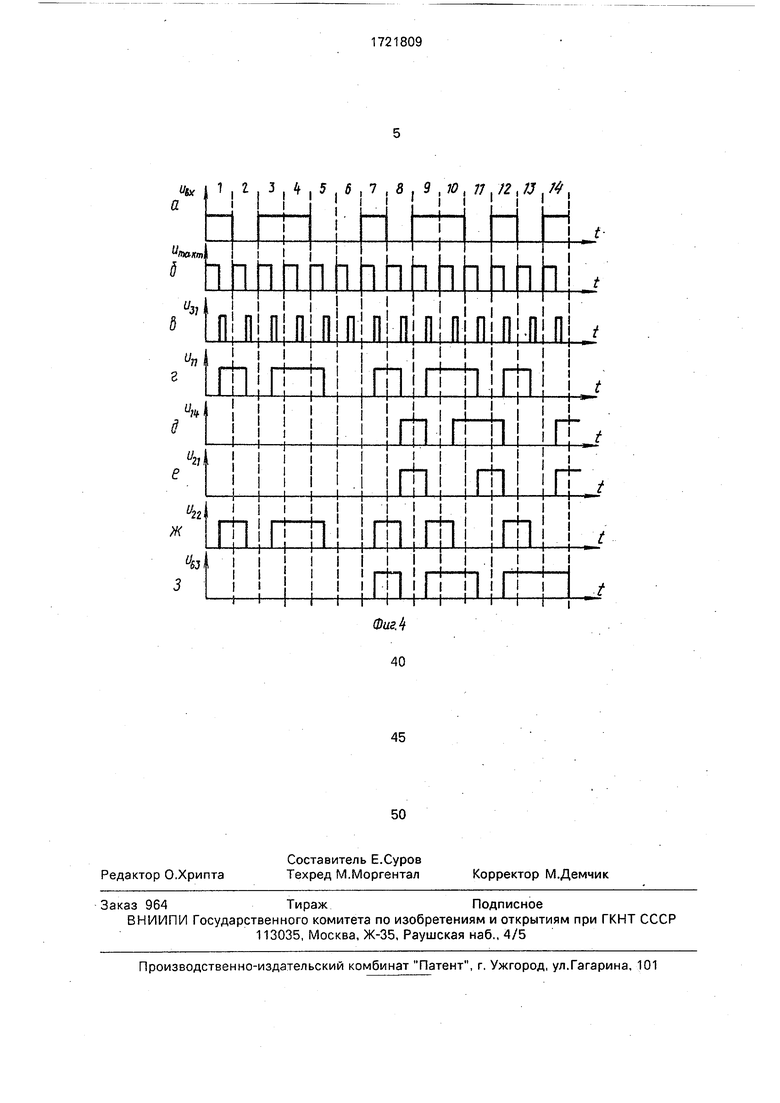

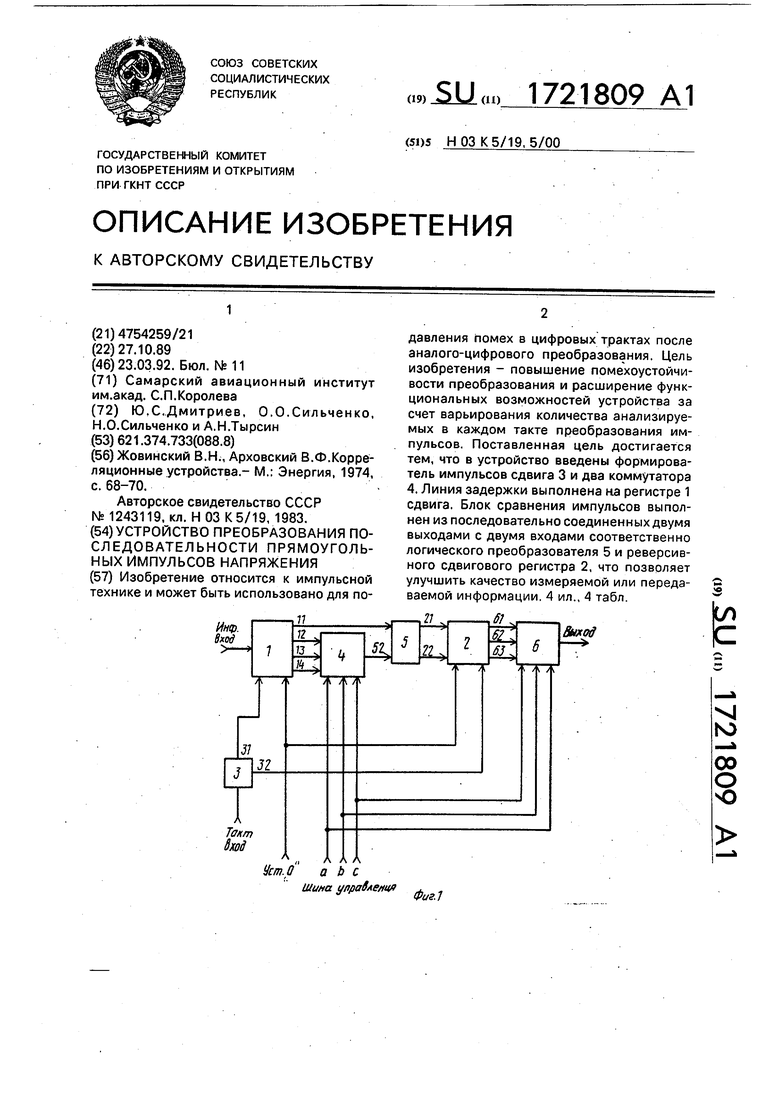

Нафиг.1 представлена структурная схема устройства преобразования последовательности прямоугольных импульсов напряжения; на фиг.2 - временные диаграммы устройства при работе в режиме I; на фиг.З - то же, в режиме II; на фиг.4 - то же, в режиме 111.

Устройство состоит из следующих блоков. Входом предлагаемого устройства является информационный вход сдвигового регистра 1, Синхронизирующие входы сдвигового регистра 1 и реверсивного сдвигового регистра 2 соединены соответственно с противофазными выходами формирователя 3 импульсов сдвига. Три выхода сдвигового регистра 1 подключены соответственно к трем информационным входам коммутатора 4, к управляющим входам которого подключены управляющие шины а,Ь,с. Первый выход сдвигового регистра 1 и выход коммутатора 4 подключены к информационным входам логического преобразователя .5, два выхода которого подключены к входам разрешения сдвига вправо и влево реверсивного сдвигового регистра 2.

Первый, второй и третий выходы реверсивного сдвигового регистра 2 подключены соответственно к трем информационным входам коммутатора 6, к управляющим входам которого подключены управляющие шины а, Ь,с. Выходом устройства является выход коммутатора 6. ШинамУстановка О соединена с входами сброса сдвигового регистра 1 и реверсивного сдвигового регистра 2.

Изменение режима работы устройства осуществляется путем установки сдвиговых регистров 1 и 2 в нулевое состояние и подачи единичного уровня напряжения на соответствующую шину управления a, b или с.

Устройство работает следующим образом.

Перед началом работы оба сдвиговых регистра 1 и 2 (фиг.1), устанавливаются в нулевое состояние (с помощью шины Установка О). Входом предлагаемого устройства является информационный вход сдвигового регистра 1. На вход устройства поступают импульсы из входной последовательности (фиг,2 а). На тактовый вход устройства поступают тактовые импульсы (фиг.2 б), формируемые, например, генератором тактовых импульсов. Тактовым входом устройства является вход формирователя 3 импульсов сдвига. Формирователь 3 импульсов сдвига на своем втором выходе формирует последовательность импульсов сдвига (фиг.2 в). На первом выходе формирователя 3 импульсов сдвига формируется последовательность импульсов, инверсная последовательности, формируемой на второй выходе.

При поступлении импульса сдвига на синхронизирующий вход сдвигового регистра 1,в него записывается уровень напряжения на информационном входе и производится сдвиг предыдущих записанных уровней. Второй, третий и четвертый выходы сдвигового регистра 1 и управляющие шины а, Ь, с подключены к входам коммутатора 4 Первый выход сдвигового регистра 1 и второй выход коммутатора 4 подключены к входам логического

преобразователя 5, два выхода которого подключены к входам разрешения сдвига вправо и влево реверсивного сдвигового регистра 2. Первый, второй и третий выходы реверсивного сдвигового регистра 2 и управляющие шины а, Ь, с подключены к входам коммутатора 6, выход которого является выходом устройства.

В сдвиговом регистре 1 происходит задержка входных импульсов на (2п-1) тактов.

В реверсивном сдвиговом регистре 2 формируется цифровой код, равный числу импульсов единичного уровня на входе предлагаемого устройства за время (2п-1) тактов. Если этот код больше или равен п, то

на выходе устройства формируется импульс единичного уровня напряжения. Если код в реверсивном сдвиговом регистре 2 меньше п, то на выходе устройства формируется импульс нулевого уровня напряжения. Коммутаторы 4 и 6 позволяют осуществлять работу устройства в нескольких режимах.

В режиме I п-2. При этом в каждом такте преобразования рассматриваются импульсы входной последовательности в трех последовательных тактах. Устройство формирует выходной импульс единичного уровня в любом i-м такте преобразования, если два или три импульса (i-2)-ro, (i-1)-ro,

i-ro тактов входной последовательности имеют единичный уровень напряжения. В противном случае будет сформирован выходной импульс нулевого уровня. Режим I реализуется при подаче на шины а, Ь, с следующих управляющих сигналов: , , .

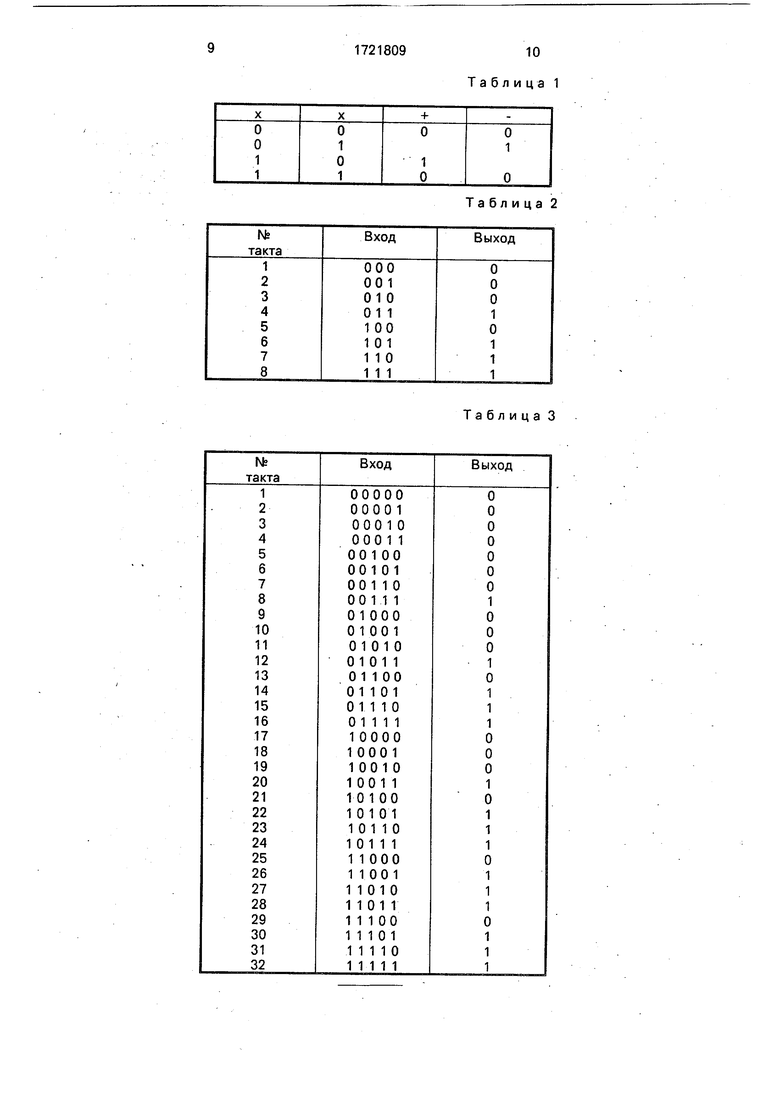

В режиме II . При этом в каждом такте преобразования рассматриваются импульсы входной последовательности в пяти последовательных тактах. Устройство формирует выходной импульс единичного уровня в любом i-м преобразовании (такте преобразования), если три, четыре или пять импульсов (l-4)-ro, (i-3)-ro, (Ы)-го, го тов входной последовательности имеют единичный уровень напряжения. В противном случае будет сформирован выходной импульс нулевого уровня. Режим II реализуется при подаче на шины а, Ь, с следующих управляющих сигналов: , , .

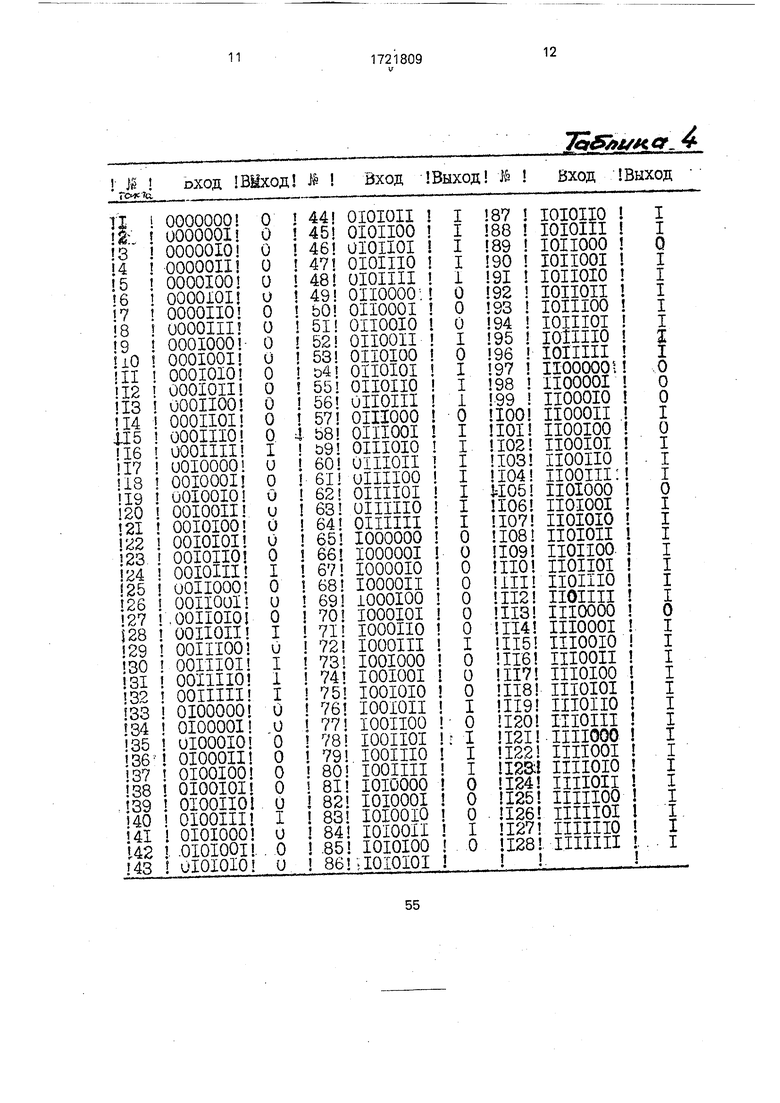

В режиме III . При этом в каждом такте преобразования рассматриваются импульсы входной последовательности в семи последовательных тактах. Устройство формирует выходной импульс единичного уровня в любом i-м такте преобразования, если четыре, пять, шесть или семь импульсов (i-6)-ro, ()-ro, (i-4)-ro, (i-3)-ro, (i-2)-ro, (i-1)-ro, i-го тактов входной последовательности имеют единичный уровень. В противном случае будет сформирован выходной импульс нулевого уровня. Режим III реализуется при подаче на шины а,Ь,с следующих управляющих сигналов: , , .

Работу логического преобразователя характеризует следующая таблица истинности.

Устройство в режиме I работает следующим образом.

В этом режиме используется второй выход сдвигового регистра 1, что обеспечивается подачей единичного уровня на шину а и нулевых уровней на шины b и с. Работа предлагаемого устройства в этом режиме описывается временными диаграммами, приведенными на фиг.2, и табл. 2 истинности.

Перед началом работы устройства происходит автоматическое обнуление сдвигового регистра и реверсивного сдвигового регистра подачей потенциала нуль на шину Установка О.

Рассмотрим пример входного сигнала (на фиг.2а).

В первом такте на информационный вход сдвигового регистра 1, являющегося входом устройства, поступает импульс единичной амплитуды напряжения (фиг.2а). При поступлении импульса сдвига на синхронизирующий вход сдвигового регистра 1 с первого выхода формирователя 3 импульсов сдвига, инверсных импульсам сдвига второго выхода формирователя 3 импульсов сдвига (фиг.2в), первый триггер сдвигового регистра 1 устанавливается в единичное состояние. Следовательно, на первом выходе

сдвигового регистра 1 будет единичный уровень напряжения (фиг. 2г). Остальные триггеры сдвигового регистра в первом такте

находятся в нулевом состоянии.

Через коммутатор 4 и логический преобразователь 5 сигналы единичного и нулевого уровней напряжения с первого и второго выходов соответственно поступают на пер0 вый и второй входы реверсивного сдвигового регистра 2. Согласно таблице истинности логического преобразователя 5 на второй вход сдвигового регистра 2 поступает сигнал, разрешающий сдвиг вправо, так как

5 первый последовательный вход сдвигового регистра 2 подключен к положительной шине питания (на этот вход действует единичный уровень напряжения (фиг.2 е, ж), и импульс сдвига в младший разряд сдвигового

0 регистра впишет единичный уровень напряжения, т.е. первый триггер реверсивного сдвигового регистра 2 установится в единичное состояние. В режиме I входной сигнал снимется с первого выхода сдвигового

5 регистра 2. Следовательно, в первом такте выходной сигнал устройства будет равен О, поскольку все триггеры сдвигового регистра 2, кроме первого, находятся в нулевом состоянии.

0Во втором такте на вход устройства поступает нул.евой уровень напряжения (фиг.2а). При поступлении импульса сдвига на синхронизирующий вход сдвигового регистра 1 первый триггер сдвигового регист5 ра 1 установится в нулевое состояние, а. второй триггер - в единичное состояние. Следовательно, на первом выходе сдвигового регистра 1 будет нулевой уровень напряжения (фиг.2г). Через коммутатор 4 и

0 логический преобразователь 5 нулевое напряжение с первого и второго выходов поступает на соответствующие входы реверсивного сдвигового регистра 2. Согласно таблице истинности логиче5 ского преобразователя 5 на первый и второй входы реверсивного сдвигового регистра подаются сигналы нулевых уровней напряжения (фиг.2 е, ж), блокирующие реверсивный сдвиговый регистр 2. Таким

0 образом в сдвиговом регистре, а следовательно, и на его выходах никаких изменений не произойдет и выходной сигнал устройства останется равным нулю (фиг.2 к).

В третьем такте на вход устройства по5 ступает импульс единичной амплитуды напряжения (фиг.2 а). При поступлении импульса сдвига первый триггер сдвигового регистра 1 установится в единичное состояние, второй триггер сдвигового регистра установится в нулевое состояние, а третий триггер - в единичное состояние. Следовательно, на первом выходе сдвигового регистра 1 будет единичный уровень напряжения, а на втором выходе сдвигового регистра 1 будет по-прежнему нулевой уровень напряжения (поскольку состояние четвертого триггера, находящегося в третьем такте в нулевом состоянии, соответствует выходному сигналу на втором выходе (фиг.2 г).

Через коммутатор 4 и логический преобразователь 5 сигналы с первого и второго выходов поступают на соответствующие первый и второй входы реверсивного сдвигового регистра 2. Согласно таблице истинности логического преобразователя 5 на второй вход сдвигового регистра 2 поступает сигнал, разрешающий сдвиг вправо (фиг.2 е, ж). Первый триггер сдвигового регистра 2 будет в единичном состоянии, и второй триггер реверсивного сдвигового регистра 2 установится в единичное состояние. Таким образом выходной сигнал, снимаемый с первого выхода сдвигового регистра 2 (с второго триггера сдвигового регистра 2), будет равен единице (фиг.2з).

В четвертом такте при поступлении на вход устройства положительного уровня напряжения согласно таблице истинности логического преобразователя 5 сдвиговый регистр 2 блокируется и выходной сигнал остается равным единице (фиг.2з).

В пятом такте на вход устройства поступает нулевой уровень напряжения. Согласно таблице истинности логического преобразователя 5 сдвиговый регистр 2 блокируется и выходной сигнал остается равным единице (фиг.2з).

В шестом такте на вход устройства поступает сигнал нулевого уровня напряжения (фиг.2а). При поступлении импульса сдвига первый триггер сдвигового регистра

1установится в нулевое состояние, а четвертый триггер - в единичное состояние. Таким образом, на первом и втором выходах сдвигового регистра 1 будут соответственно коды О и 1. Согласно таблице истинности логического преобразователя 5 на первый вход сдвигового регистра 2 поступает сигнал, разрешающий сдвиг влево (фиг.2е), так как левый последовательный вход сдвигового регистра 2 подключен к общей шине (на этот вход действует нулевой уровень напряжения), и импульс сдвига установит второй триггер реверсивного сдвигового регистра

2в нулевое состояние. Следовательно, на выходе устройства будет О.

Устройство в режиме II работает следующим образом.

В этом режиме используется третий выход сдвигового регистра 1, что обеспечивается подачей единичного уровня на шину b и нулевых уровней напряжения на шины а и

с. Работа устройства описывается временными диаграммами, приведенными на фиг.З, и табл.3 истинности.

В работе устройства в режиме III используется четвертый выход сдвигового регистра 1, что обеспечивается подачей едиичного уровня на шину с и нулевых уровней на шины а и Ь. Работа устройства в этом режиме описывается временными диаграммами на фиг.4 и табл. 4 истинности.

Формула изобретения Устройство преобразования последовательности прямоугольных импульсов напряжения, содержащее линию задержки

импульсов, первый выход которой последовательно соединен с первым входом блока сравнения импульсов, от личающееся тем, что, с целью повышения помехоустойчивости и расширения функциональных возможностей за счет варьирования количества анализируемых в каждом такте преобразования импульсов, в устройство введены два коммутатора, формирователь импульсов сдвига, вход которого является тактовым

входом устройства, управляющие входы коммутаторов объединены и являются управляющими шинами устройства, линия задержки выполнена на регистре сдвига, информационный вход которого является

информационным входом устройства, блок сравнения импульсов выполнен из последовательно соединенных двумя выходами с двумя входами соответственно логического преобразователя и реверсивного сдвигового регистра, входы сброса сдвигового регистра и реверсивного сдвигового регистра соединены с шиной установки О, первый и второй противофазные выходы формирователя импульсов сдвига соединены соответственно с синхронизирующими входами сдвигового регистра и реверсивного сдвигового регистра, соответствующие три информационных входа первогр коммутатора соединены с соответствующими выходами

сдвигового регистра, второй вход логического преобразователя соединен с выходом первого коммутатора, три информационных входа второго коммутатора соединены с соответствующими тремя выходами реверсивного сдвигового регистра, выход второго коммутатора является выходом устройства.

Таблица 3

| Жовинский В.Н., Арховский В.Ф.Корреляционные устройства.- М.: Энергия, 1974, с | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Способ преобразования последовательности прямоугольных импульсов напряжения и устройство для его осуществления | 1983 |

|

SU1243119A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-03-23—Публикация

1989-10-27—Подача