сг

с

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Вторичные часы | 1986 |

|

SU1525671A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

Использование вычислительная и измерительная техника а также в приемной аппаратуре связи Цель изобретения обеспечение возможности селекции фазо- импульсных последовательностей при одновременном обеспечении возможности преобразования входной последовательности в параллельный код. Сущность изобретения: селектор сигналов содержит пороговые элементы 1 и 2, информационную шину 3, шины 4 и 5 пороговых напряжений, формирователи 6 и 7 импульсов, триггеры 8 и 9, элемент И 10, выходную шину 11. Цель достигается за счет введения триггера 12, блока 13 анализа наличия импульсов, регистра 14 сдвига, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15. выходных шин 16 и 17, элемента И - ИЛИ 18 и образования новых функциональных связей 4 ил

vj

СА) Ю Јь

сл

фигЛ

Изобретение относится к импульсной технике w может быть использовано в вычислительной и измерительной технике, а также в приемной аппаратуре связи.

Известно устройство, содержащее два пороговых элемента, формирователь и ключ.

Недостатком данного устройства является то, что оно не осуществляет селекцию фззоимпульсных последовательностей при одновременном обеспечении преобразования входной последовательности в параллельный код.

Известно также устройство, содержащее формирователь импульсов, интегратор, два пороговых элемента, D-триггер, ключ, блок управления, входную и две выходные шины.

Данное устройство обеспечивает селекцию входной импульсной последовательности по частоте следования и не выделяет фазоимпульсные последовательности с последующим преобразованием их в параллельный код.

Наиболее близким к предлагаемому устройству является амплитудно-временной анализатор, содержащий два пороговых элемента, элемент НЕ. два формирователя импульсов, два триггера, генератор пилообразного напряжения, времязадающий блок, элемент ИЛИ-НЕ. элемент И с соответствующими связями.

Известное устройство не обеспечивает селекцию фазоимпульсных последовательностей при одновременном преобразовании входной последовательности в параллельный код.

Цель изобретения - обеспечение возможности селекции фазоимпульсных последовательностей при одновременном обеспечении возможности преобразования входной последовательности в параллельный код.

Поставленная цель достигается тем, что в селектор сигналов, содержащий первый и второй пороговые элементы, первые входы которых соединены с информационным входом, вторые входы - соответственно с первым и вторым входами пороговых напряжений, а выход первого порогового элемента - с входом первого формирователя импульсов, второй Формирователь импульсов, первый триггер, второй триггер, выход которого соединен с первым входом элемента И, выход последнего соединен с первой выходной шиной, введены третий триггер, блок анализа наличия импульсов, регистр сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вторая и третья выходные шины и элемент И-ИЛИ. первые входы первой и

второй групп входов которого соединены с выходами соответственно первого и второго формирователей импульсов, вторые входы первой и второй групп входов - с

выходами соответственно второго и первого пороговых элементов, а выход - с С-вхо- дом второго триггера, S-входом третьего триггера, входом блока анализа наличия импульсов и тактовым входом регистра сдвига,

0 с первого по N-й выходы которого соединены с второй выходной шиной, вход управления - с выходом второго триггера, вход последовательной информации и первый информационный вход- с выходом элемен5 та ИСКЛЮЧАЮЩЕЕ ИЛИ, второй информационный вход - с общей шиной и с четвертого по (М-М)-й информационными входами регистра сдвига, третий информационный вход-с шиной потенциалалогиче0 ской 1, (N+1)-u выход - с D-входом второго триггера З-вход которого соединен с R-вхо- дом третьего триггера, выходом блока анализа наличия импульсов и С-входом первого триггера, D-вход которого соединен с выхо5 дом второго порогового элемента, входом второго формирователя импульсов и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого триггера, причем выход

0 третьего триггера соединен с вторым входом элемента И и третьей выходной шиной. Введение элемента И-ИЛИ, блока анализа наличия импульсов обеспечивает совместно с известными блоками выделение

5 фазоимпульсных последовательностей, частота следования которых может находиться в широких пределах.

Введение логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и связи между ним и

0 известными блоками обеспечивают автоматический анализ полярности посылки, инвертирование с целью правильного преобразования в параллельный код.

Введение регистра сдвига и его связи

5 между блоками обеспечивают преобразование последовательности входных сигналов в параллельный код и формирование служебных сигналов, характеризующих, например, заполнение регистра информацией.

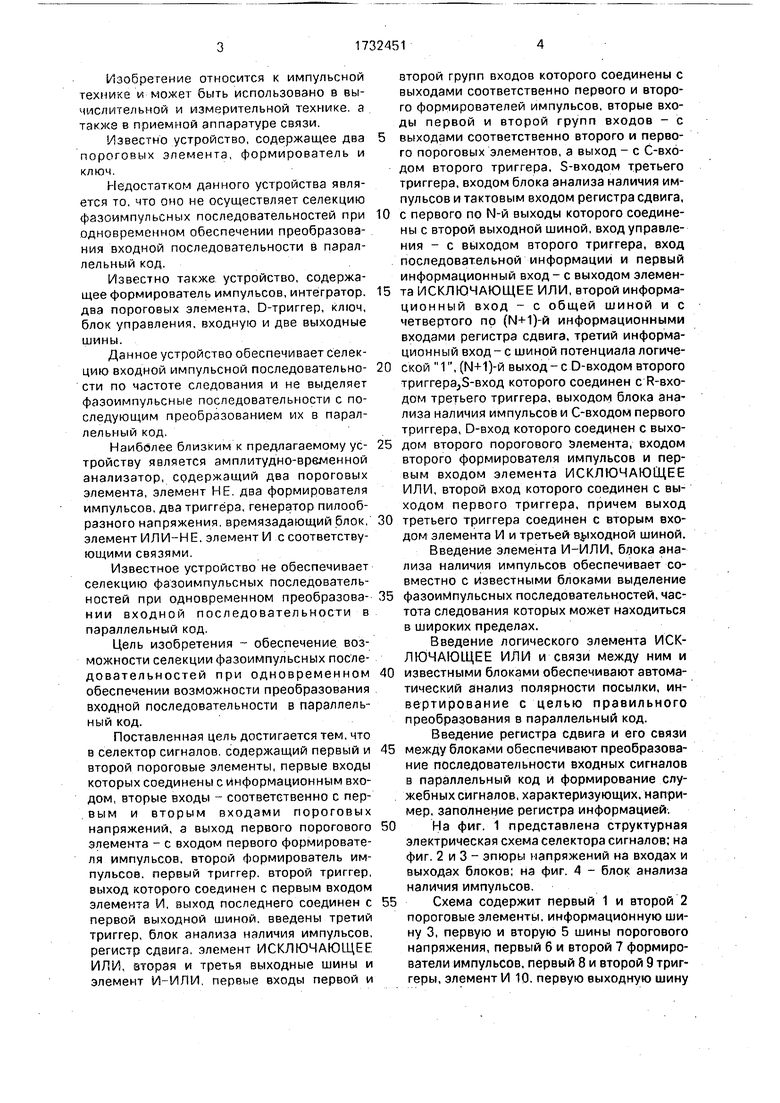

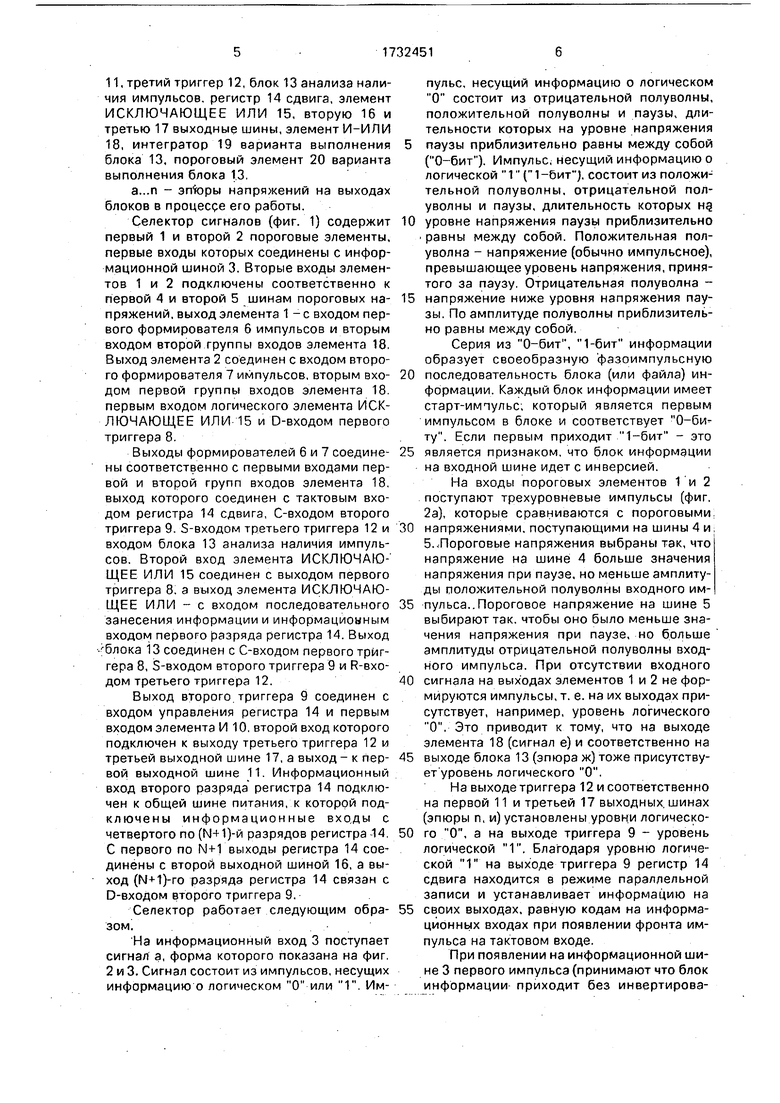

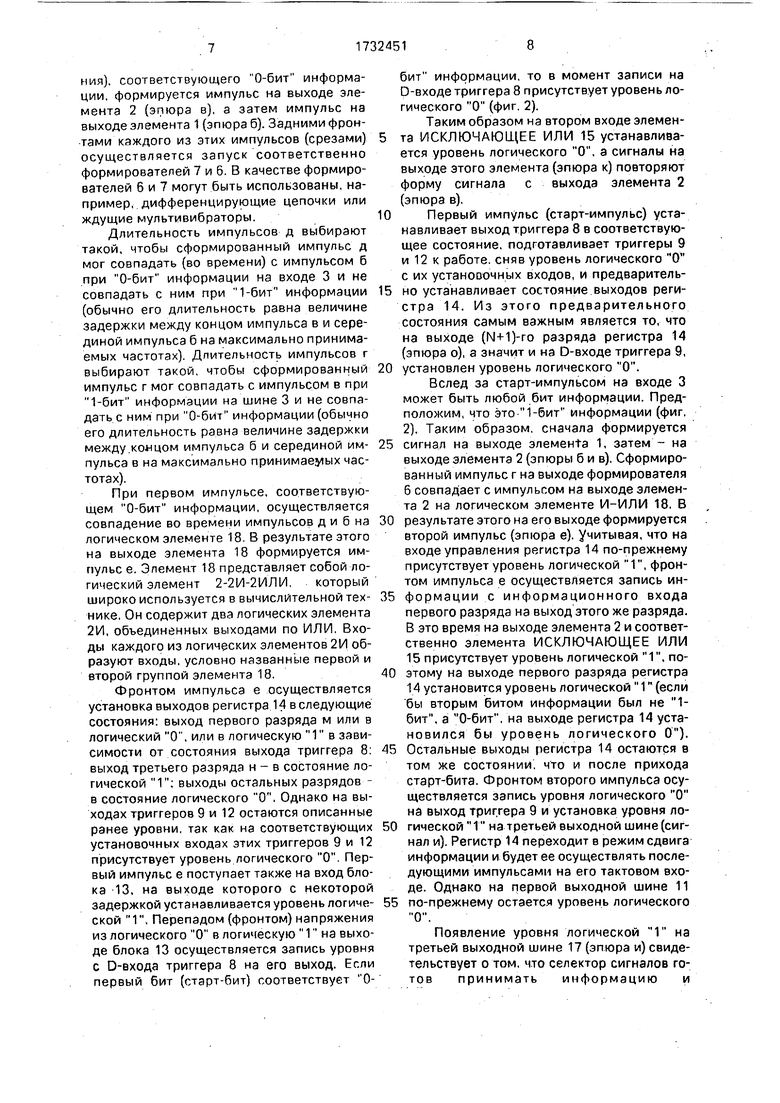

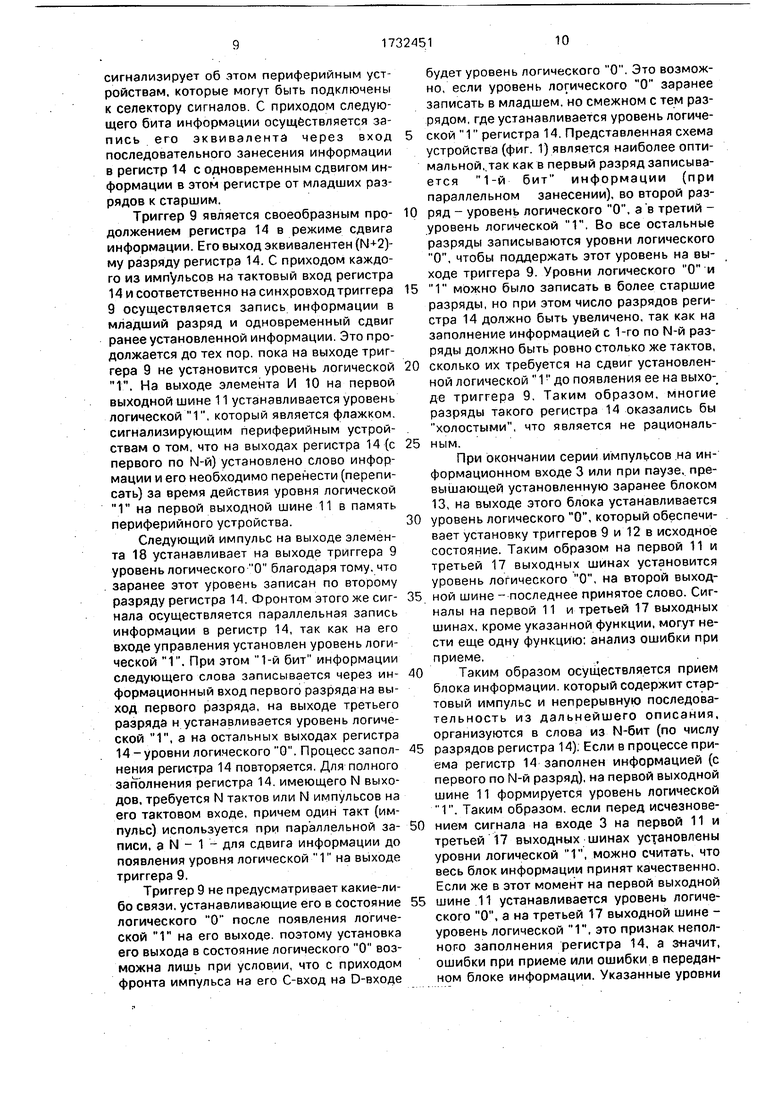

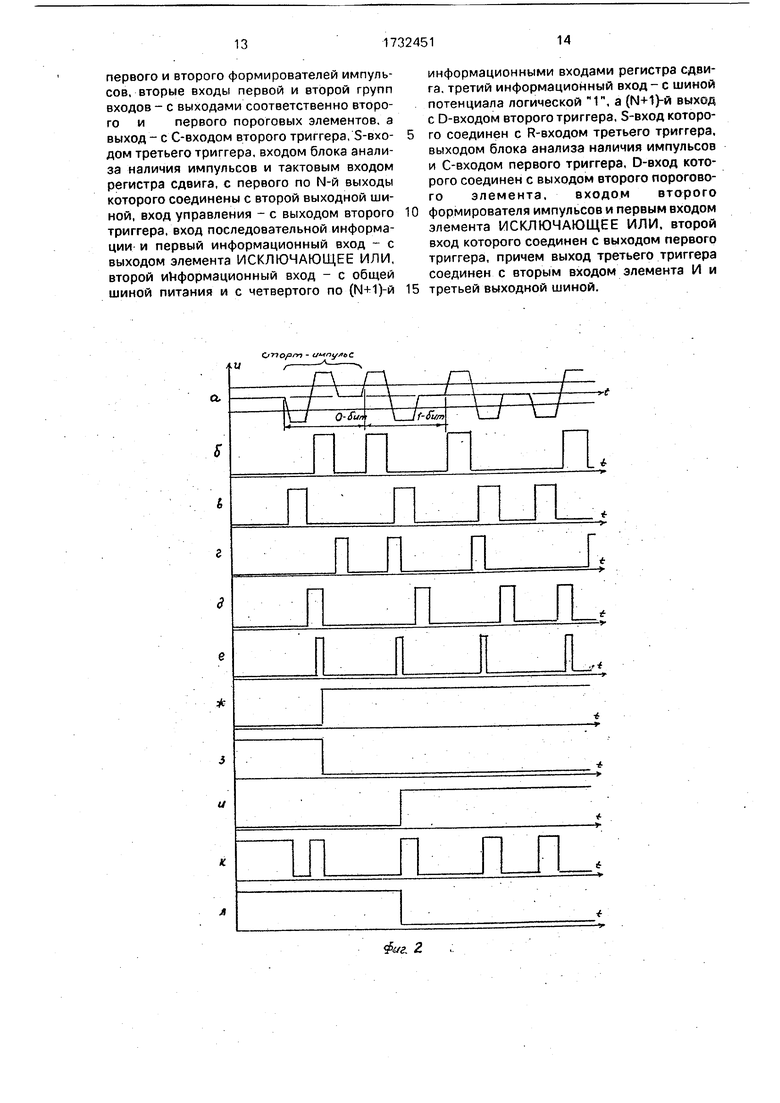

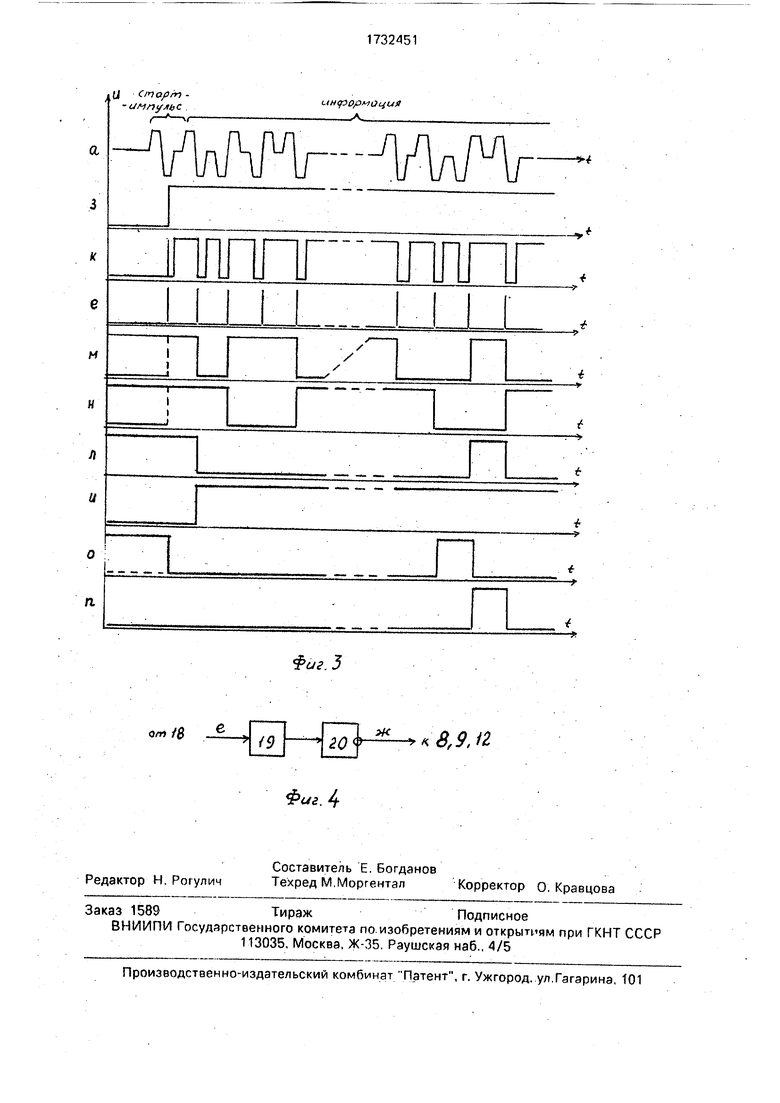

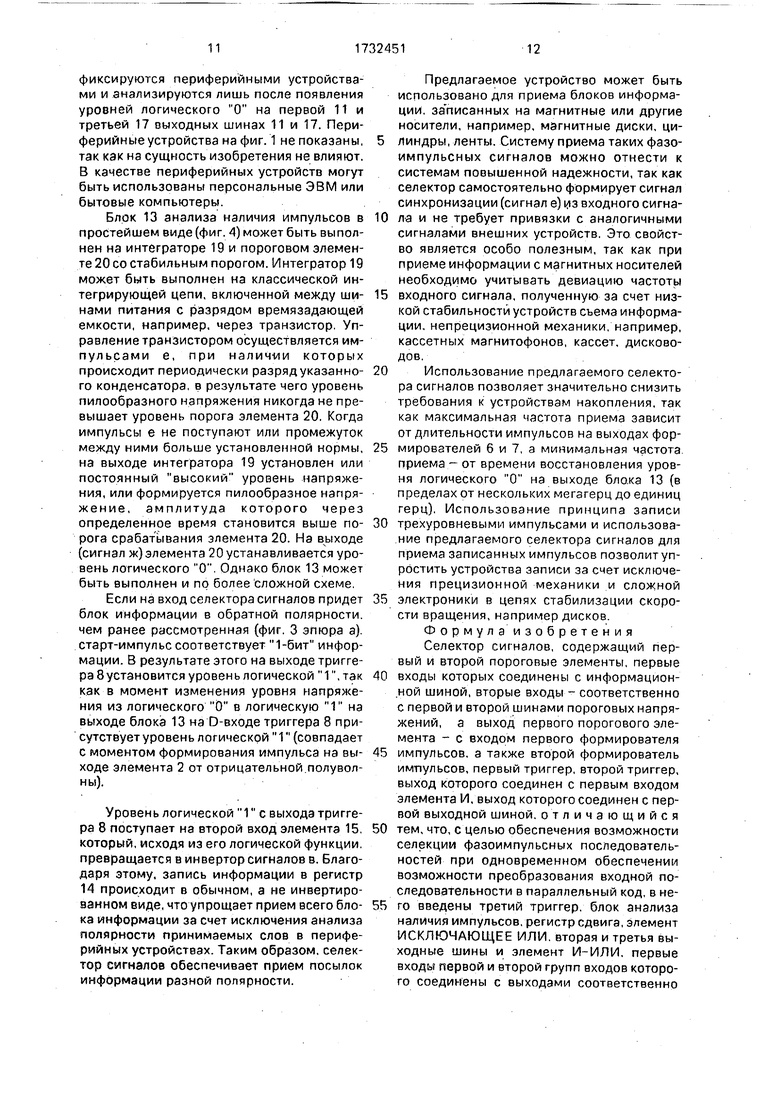

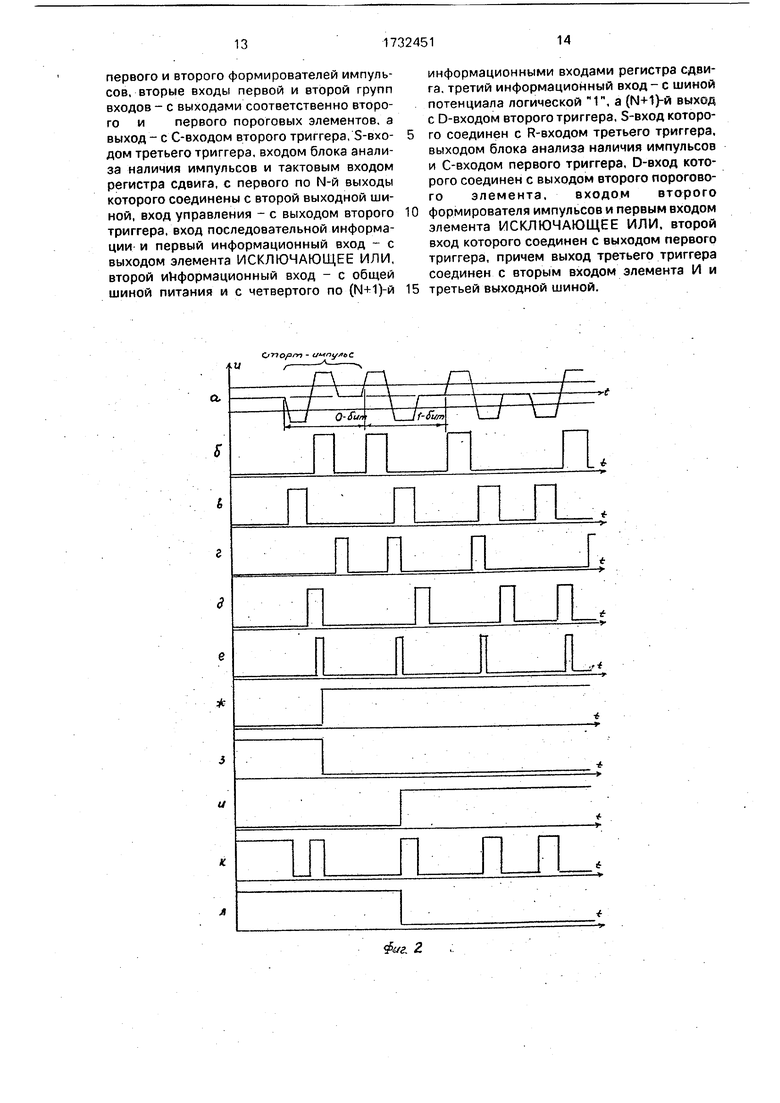

0 На фиг. 1 представлена структурная электрическая схема селектора сигналов; на фиг. 2 и 3 - эпюры напряжений на входах и выходах блоков; на фиг. 4 - блок анализа наличия импульсов.

5 Схема содержит первый 1 и второй 2 пороговые элементы, информационную шину 3, первую и вторую 5 шины порогового напряжения, первый 6 и второй 7 формирователи импульсов, первый 8 и второй 9 триггеры, элемент И 10. первую выходную шину

11, третий триггер 12, блок 13 анализа наличия импульсов, регистр 14 сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, вторую 16 и третью 17 выходные шины, элемент И-ИЛИ 18, интегратор 19 варианта выполнения блока 13, пороговый элемент 20 варианта выполнения блока 13.

а...п - эп юры напряжений на выходах блоков в процессе его работы.

Селектор сигналов (фиг. 1) содержит первый 1 и второй 2 пороговые элементы, первые входы которых соединены с информационной шиной 3. Вторые входы элементов 1 и 2 подключены соответственно к первой 4 и второй 5 шинам пороговых на- пряжений, выход элемента 1 - с входом первого формирователя б импульсов и вторым входом второй группы входов элемента 18. Выход элемента 2 соединен с входом второго формирователя 7 импульсов, вторым вхо- дом первой группы входов элемента 18 первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и D-входом первого триггера 8.

Выходы формирователей 6 и 7 соедине- ны соответственно с первыми входами первой и второй групп входов элемента 18, выход которого соединен с тактовым входом регистра 14 сдвига, С-входом второго триггера 9. S-входом третьего триггера 12 и входом блока 13 анализа наличия импульсов. Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 соединен с выходом первого триггера 8. а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ - с входом последовательного занесения информации и информационным входом первого разряда регистра 14. Выход блока 13 соединен с С-входом первого триггера 8, S-входом второго триггера 9 и R-вхо- дом третьего триггера 12.

Выход второго триггера 9 соединен с входом управления регистра 14 и первым входом элемента И 10. второй вход которого подключен к выходу третьего триггера 12 и третьей выходной шине 17, а выход - к пер- вой выходной шине 11. Информационный вход второго разряда регистра 14 подключен к общей шине питания, к которой подключены информационные входы с четвертого по (N-H)-u разрядов регистра 14 С первого по N+1 выходы регистра 14 соединены с второй выходной шиной 16, а выход (N+1)-ro разряда регистра 14 связан с D-входом второго триггера 9.

Селектор работает следующим обра- зом.

На информационный вход 3 поступает сигнал а, форма которого показана на фиг. 2 и 3. Сигнал состоит из импульсов, несущих информацию о логическом О или 1 Импульс, несущий информацию о логическом О состоит из отрицательной полуволны, положительной полуволны и паузы, длительности которых на уровне напряжения паузы приблизительно равны между собой (0-бит). Импульс, несущий информацию о логической 1 (1-бит), состоит из положительной полуволны, отрицательной полуволны и паузы, длительность которых на. уровне напряжения паузы приблизительно равны между собой. Положительная полуволна - напряжение (обычно импульсное), превышающее уровень напряжения, принятого за паузу. Отрицательная полуволна - напряжение ниже уровня напряжения паузы. По амплитуде полуволны приблизительно равны между собой.

Серия из 0-бит, 1-бит информации образует своеобразную фазоимпульсную последовательность блока (или файла) информации. Каждый блок информации имеет старт-импульс, который является первым импульсом в блоке и соответствует 0-би- ту. Если первым приходит 1-бит - это является признаком, что блок информации на входной шине идет с инверсией.

На входы пороговых элементов 1 и 2 поступают трехуровневые импульсы (фиг. 2а), которые сравниваются с пороговыми напряжениями, поступающими на шины 4 и 5..Пороговые напряжения выбраны так, что напряжение на шине 4 больше значения напряжения при паузе, но меньше амплитуды положительной полуволны входного импульса..Пороговое напряжение на шине 5 выбирают так. чтобы оно было меньше значения напряжения при паузе, но больше амплитуды отрицательной полуволны входного импульса. При отсутствии входного сигнала на выходах элементов 1 и 2 не формируются импульсы, т. е. на их выходах присутствует, например, уровень логического О. Это приводит к тому, что на выходе элемента 18 (сигнал е) и соответственно на выходе блока 13 (эпюра ж) тоже присутствует уровень логического О.

На выходе триггера 12 и соответственно на первой 11 и третьей 17 выходных шинах (эпюры п, и) установлены уровни логического О, а на выходе триггера 9 - уровень логической 1. Благодаря уровню логической 1 на выходе триггера 9 регистр 14 сдвига находится в режиме параллельной записи и устанавливает информацию на своих выходах, равную кодам на информационных входах при появлении фронта импульса на тактовом входе.

При появлении на информационной шине 3 первого импульса (принимают что блок информации приходит без инвертироваиия), соответствующего О-бит информации, формируется импульс на выходе элемента 2 (эпюра в), а затем импульс на выходе элемента 1 (эпюра б). Задними фронтами каждого из этих импульсов (срезами) осуществляется запуск соответственно формирователей 7 и 6. В качестве формирователей 6 и 7 могут быть использованы, например, дифференцирующие цепочки или ждущие мультивибраторы.

Длительность импульсов д выбирают такой, чтобы сформированный импульс д мог совпадать (во времени) с импульсом б при О-бит информации на входе 3 и не совпадать с ним при 1-бит информации (обычно его длительность равна величине задержки между концом импульса в и серединой импульса б на максимально принимаемых частотах). Длительность импульсов г выбирают такой, чтобы сформированный импульс г мог совпадать с импульсом в при 1-бит информации на шине 3 и не совпадать с ним при О-бит информации (обычно его длительность равна величине задержки между комцом импульса б и серединой импульса в на максимально принимаемых частотах).

При первом импульсе, соответствующем О-бит информации, осуществляется совпадение во времени импульсов д и б на логическом элементе 18 В результате этого на выходе элемента 18 формируется импульс е. Элемент 18 представляет собой логический элемент 2-2И-2ИЛИ, который широко используется в вычислительной технике, Он содержит два логических элемента 2И, объединенных выходами по ИЛИ. Входы каждого из логических элементов 2И образуют входы, условно названные первой и второй группой элемента 18.

Фронтом импульса е осуществляется установка выходов регистра 14 в следующие состояния: выход первого разряда м или в логический О, или в логическую 1 в зависимости от состояния выхода триггера 8 выход третьего разряда н - в состояние логической выходы остальных разрядов - в состояние логического О. Однако на выходах триггеров 9 и 12 остаются описанные ранее уровни, так как на соответствующих установочных входах этих триггеров 9 и 12 присутствует уровень логического О Первый импульс е поступает также на вход блока 13, на выходе которого с некоторой задержкой устанавливается уровень логической 1, Перепадом (фронтом) напряжения из логического О в логическую 1 на выходе блока 13 осуществляется запись уровня с D-входа триггера 8 на его выход. Если первый бит (старт-бит) соответствует 0бит информации, то в момент записи на D-входе триггера 8 присутствует уровень логического О (фиг. 2).

Таким образом на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается уровень логического О, а сигналы на выходе этого элемента (эпюра к) повторяют форму сигнала с выхода элемента 2 (эпюра в).

0 Первый импульс (старт-импульс) устанавливает выход триггера 8 в соответствующее состояние, подготавливает триггеры 9 и 12 к работе, сняв уровень логического О с их установочных входов, и предваритель5 но устанавливает состояние выходов регистра 14. Из этого предварительного состояния самым важным является то, что на выходе (М-Н)-го разряда регистра 14 (эпюра о), а значит и на D-входе триггера 9,

0 установлен уровень логического О.

Вслед за старт-импульсом на входе 3 может быть любой бит информации. Предположим, что это 1-бит информации (фиг. 2). Таким образом, сначала формируется

5 сигнал на выходе элемента 1, затем - на выходе элемента 2 (эпюры б и в). Сформированный импульс г на выходе формирователя 6 совпадает с импульсом на выходе элемента 2 на логическом элементе И-ИЛИ 18, В

0 результате этого на его выходе формируется второй импульс (эпюра е). учитывая, что на входе управления регистра 14 по-прежнему присутствует уровень логической 1, фронтом импульса е осуществляется запись ин5 формации с информационного входа первого разряда на выход этого же разряда. В это время на выходе элемента 2 и соответственно элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 присутствует уровень логической 1, по0 этому на выходе первого разряда регистра 14 установится уровень логической 1 (если бы вторым битом информации был не 1- бит, а О-бит, на выходе регистра 14 установился бы уровень логического О).

5 Остальные выходы регистра 14 остаются в том же состоянии, что и после прихода старт-бита. Фронтом второго импульса осуществляется запись уровня логического О на выход триггера 9 и установка уровня ло0 гической 1 на третьей выходной шине (сигнал и). Регистр 14 переходит в режим сдвига информации и будет ее осуществлять последующими импульсами на его тактовом входе. Однако на первой выходной шине 11

5 no-прежнему остается уровень логического О.

Появление уровня логической 1 на третьей выходной шине 17 (эпюра и) свидетельствует о том, что селектор сигналов готов принимать информацию и

сигнализирует об этом периферийным устройствам, которые могут быть подключены к селектору сигналов. С приходом следующего бита информации осуществляется запись его эквивалента через вход последовательного занесения информации в регистр 14с одновременным сдвигом информации в этом регистре от младших разрядов к старшим.

Триггер 9 является своеобразным продолжением регистра 14 в режиме сдвига информации. Его выход эквивалентен (N+2)- му разряду регистра 14. С приходом каждого из импульсов на тактовый вход регистра 14 и соответственно на синхровход триггера 9 осуществляется запись информации в младший разряд и одновременный сдвиг ранее установленной информации. Это продолжается до тех пор. пока на выходе триггера 9 не установится уровень логической 1. На выходе элемента И 10 на первой выходной шине 11 устанавливается уровень логической 1, который является флажком, сигнализирующим периферийным устройствам о том, что на выходах регистра 14 (с первого по N-й) установлено слово информации и его необходимо перенести (переписать) за время действия уровня логической 1 на первой выходной шине 11 в память периферийного устройства.

Следующий импульс на выходе элемента 18 устанавливает на выходе триггера 9 уровень логического О благодаря тому, что заранее этот уровень записан по второму разряду регистра 14. Фронтом этого же сигнала осуществляется параллельная запись информации в регистр 14, так как на его входе управления установлен уровень логической 1. При этом 1-й бит информации следующего слова записывается через информационный вход первого разряда на выход первого разряда, на выходе третьего разряда н устанавливается уровень логической 1, а на остальных выходах регистра 14 - уровни логического О. Процесс заполнения регистра 14 повторяется, Для полного заполнения регистра 14, имеющего N выходов, требуется N тактов или N импульсов на его тактовом входе, причем один такт (импульс) используется при параллельной записи, а N - 1 - для сдвига информации до появления уровня логической 1 на выходе триггера 9.

Триггер 9 не предусматривает какие-либо связи, устанавливающие его в состояние логического О после появления логической 1 на его выходе, поэтому установка его выхода в состояние логического О возможна лишь при условии, что с приходом фронта импульса на его С-вход на D-входе

будет уровень логического О. Это возможно, если уровень логического О заранее записать в младшем, но смежном с тем разрядом, где устанавливается уровень логиче- 5 ской 1 регистра 14. Представленная схема устройства (фиг. 1) является наиболее оптимальной, так как в первый разряд записывается 1-й бит информации (при параллельном занесении), во второй раз0 ряд - уровень логического О, а в третий - уровень логической 1. Во все остальные разряды записываются уровни логического О, чтобы поддержать этот уровень на выходе триггера 9. Уровни логического О и

5 1 можно было записать в более старшие разряды, но при этом число разрядов регистра 14 должно быть увеличено, так как на заполнение информацией с 1-го по N-й разряды должно быть ровно столько же тактов,

0 сколько их требуется на сдвиг установленной логической 1 до появления ее на выходе триггера 9. Таким образом, многие разряды такого регистра 14 оказались бы холостыми, что является не рациональ5 ным.

При окончании серии импульсов на информационном входе 3 или при паузе, превышающей установленную заранее блоком 13, на выходе этого блока устанавливается

0 уровень логического О, который обеспечивает установку триггеров 9 и 12 в исходное состояние. Таким образом на первой 11 и третьей 17 выходных шинах установится уровень логического О, на второй выход5 ной шине - последнее принятое слово. Сигналы на первой 11 и третьей 17 выходных шинах, кроме указанной функции, могут нести еще одну функцию: анализ ошибки при приеме,

0 Таким образом осуществляется прием блока информации, который содержит стартовый импульс и непрерывную последовательность из дальнейшего описания, организуются в слова из N-бит (по числу

5 разрядов регистра 14). Если в процессе приема регистр 14 заполнен информацией (с первого по N-й разряд), на первой выходной шине 11 формируется уровень логической 1. Таким образом, если перед исчезнове0 нием сигнала на входе 3 на первой 11 и третьей 17 выходных шинах установлены уровни логической 1, можно считать, что весь блок информации принят качественно. Если же в этот момент на первой выходной

5 шине 11 устанавливается уровень логического О, а на третьей 17 выходной шине - уровень логической 1, это признак неполного заполнения регистра 14, а значит, ошибки при приеме или ошибки в переданном блоке информации. Указанные уровни

фиксируются периферийными устройствами и анализируются лишь после появления уровней логического О на первой 11 и третьей 17 выходных шинах 11 и 17. Периферийные устройства на фиг. 1 не показаны, так как на сущность изобретения не влияют. В качестве периферийных устройств могут быть использованы персональные ЭВМ или бытовые компьютеры.

Блок 13 анализа наличия импульсов в простейшем виде (фиг. 4) может быть выполнен на интеграторе 19 и пороговом элементе 20 со стабильным порогом. Интегратор 19 может быть выполнен на классической интегрирующей цепи, включенной между шинами питания с разрядом времязадающей емкости, например, через транзистор Управление транзистором осуществляется им- пульсами е, при налич-ии которых происходит периодически разряд указанного конденсатора, в результате чего уровень пилообразного напряжения никогда не превышает уровень порога элемента 20. Когда импульсы е не поступают или промежуток между ними больше установленной нормы, на выходе интегратора 19 установлен или постоянный высокий уровень напряжения, или формируется пилообразное напряжение, амплитуда которого через определенное время становится выше порога срабатывания элемента 20. На выходе (сигнал ж)элемента 20 устанавливается уровень логического О Однако блок 13 может быть выполнен и по более сложной схеме

Если на вход селектора сигналов придет блок информации в обратной полярности чем ранее рассмотренная (фиг. 3 эпюра а) старт-импульс соответствует 1-бит информации. В результате этого на выходе триггера 8 установится уровень логической 1 лак как в момент изменения уровня напряжения из логического О в логическую 1 на выходе блока 13 на D-входе триггера 8 присутствует уровень логической 1(совпадает с моментом формирования импульса на выходе элемента 2 от отрицательной полуволны).

Уровень логической 1 с выхода триггера 8 поступает на второй вход элемента 15 который, исходя из его логической функции превращается в инвертор сигналов в. Благодаря этому, запись информации в регистр 14 происходит в обычном, а не инвертированном виде, что упрощает прием всего блока информации за счет исключения анализа полярности принимаемых слов в периферийных устройствах. Таким образом, селектор сигналов обеспечивает прием посылок информации разной полярности.

Предлагаемое устройство может быть использовано для приема блоков информации за писанных на магнитные или другие носители, например, магнитные диски, цилиндры, ленты. Систему приема таких фазо- импульсных сигналов можно отнести к системам повышенной надежности, так как селектор самостоятельно формирует сигнал синхронизации (сигнал е) из входного сигна0 ла и не требует привязки с аналогичными сигналами внешних устройств. Это свойство является особо полезным, так как при приеме информации с магнитных носителей необходимо учитывать девиацию частоты

5 входного сигнала, полученную за счет низкой стабильности устройств съема информации, непрецизионной механики, например, кассетных магнитофонов, кассет, дисководов

0Использование предлагаемого селектора сигналов позволяет значительно снизить требования к устройствам накопления, так как максимальная частота приема зависит от длительности импульсов на выходах фор5 мирователей 6 и 7, а минимальная частота приема - от времени восстановления уровня логического О на выходе блока 13 (в пределах от нескольких мегагерц до единиц герц) Использование принципа записи

0 трехуровневыми импульсами и использование предлагаемого селектора сигналов для приема записанных импульсов позволит упростить устройства записи за счет исключения прецизионной механики и сложной

5 электроники в цепях стабилизации скорости вращения, например дисков Формула изобретения Селектор cntналов, содержащий первый и второй пороговые элементы, первые

0 входы которых соединены с информационной шиной, вторые входы - соответственно с первой и второй шинами пороговых напряжений, а выход первого порогового элемента - с входом первого формирователя

5 импульсов, а также второй формирователь импульсов, первый триггер, второй триггер, выход которого соединен с первым входом элемента И, выход которого соединен с первой выходной шиной, отличающийся

0 тем, что, с целью обеспечения возможности селекции фазоимпульсных последовательностей при одновременном обеспечении возможности преобразования входной последовательности в параллельный код, в не5 го введены третий триггер, блок анализа наличия импульсов, регистр сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ вторая и третья выходные шины и элемент И-ИЛИ, первые входы первой и второй групп входов которого соединены с выходами соответственно

первого и второго формирователей импульсов, вторые входы первой и второй групп входов- с выходами соответственно второго и первого пороговых элементов, а выход - с С-входом второго триггера, S-вхо- дом третьего триггера, входом блока анализа наличия импульсов и тактовым входом регистра сдвига, с первого по N-й выходы которого соединены с второй выходной шиной, вход управления - с выходом второго триггера, вход последовательной информации и первый информационный вход - с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй информационный вход - с общей шиной питания и с четвертого по (М+1)-й

Јj noprn -

0

информационными входами регистра сдвига, третий информационный вход- с шиной потенциала логической Г, а (N+1}-n выход с D-входом второго триггера, S-вход которого соединен с R-входом третьего триггера, выходом блока анализа наличия импульсов и С-входом первого триггера, D-вход которого соединен с выходом второго порогового элемента, входом второго формирователя импульсов и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. второй вход которого соединен с выходом первого триггера, причем выход третьего триггера соединен с вторым входом элемента И и третьей выходной шиной.

у с/ПО/У т - -иппуяьс

информация л

а

-WJV---WV

пш

1

И

/

/

фуг. J

-9-4

л

| Авторское свидетельство СССР № 1198745, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-05-07—Публикация

1989-12-05—Подача