(54) УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1978 |

|

SU738151A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1982 |

|

SU1067598A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU873405A1 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1977 |

|

SU660232A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2037267C1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1988 |

|

SU1670616A2 |

| Аналого-цифровой преобразователь | 1974 |

|

SU525240A1 |

1

Изобретение относится к цифровой электроизмерительной технике и предназначено для преобразования широкополосных электрических сигналов в цифровой код.

В общем случае процесс аналогоцифрового преобразования изменяющихся во времени сигнашов приводит к тому, что результаты преобразования сдвинуты во времени относительно кодируемого сигнала на величину фазового сдвига. При этом значение динамической погрешности аналого-цифрового преобразования при заданном частотном спектре кодируемого сигнала зависит от величины задержки отсчета, достигает минимальной величины при задержке отсчета равной.фазовому сдвигу. Так как процесс аналогоцифрового преобразования носит нелинейный характер, а величина фазового сдвига зависит от частотного спектра кодируемого сигнала, то величина задержки отсчета не может быть задана заранее.

Известны устройства аналого-цифрового преобразования с автоматической коррекцией динамической погрешности L lОднако введение дополнительных тактов коррекции увеличивает . время преобразования. Кроме того, указанные устройства не позволяют определить фазовый сдвиг для получения минимального зна,чения динамической погрешности при кодировании широкополосных сигнгшой.

Известно устройство аналого-цифtoрового преобразования, содержащее сравнивающее устройство, первый вход которого соединен со входной шиной, второй вход - с выходом цифроаналогового преобразователя, а выход - со 15 входом устройства управления 1.2}.

Недостатком устройства является большая динамическая погрешность аналого-цифрового преобразования, возникающая при кодировании широко20полосных сигналов.

Цель изобретения - получение минимального значения дийамической погрешности.

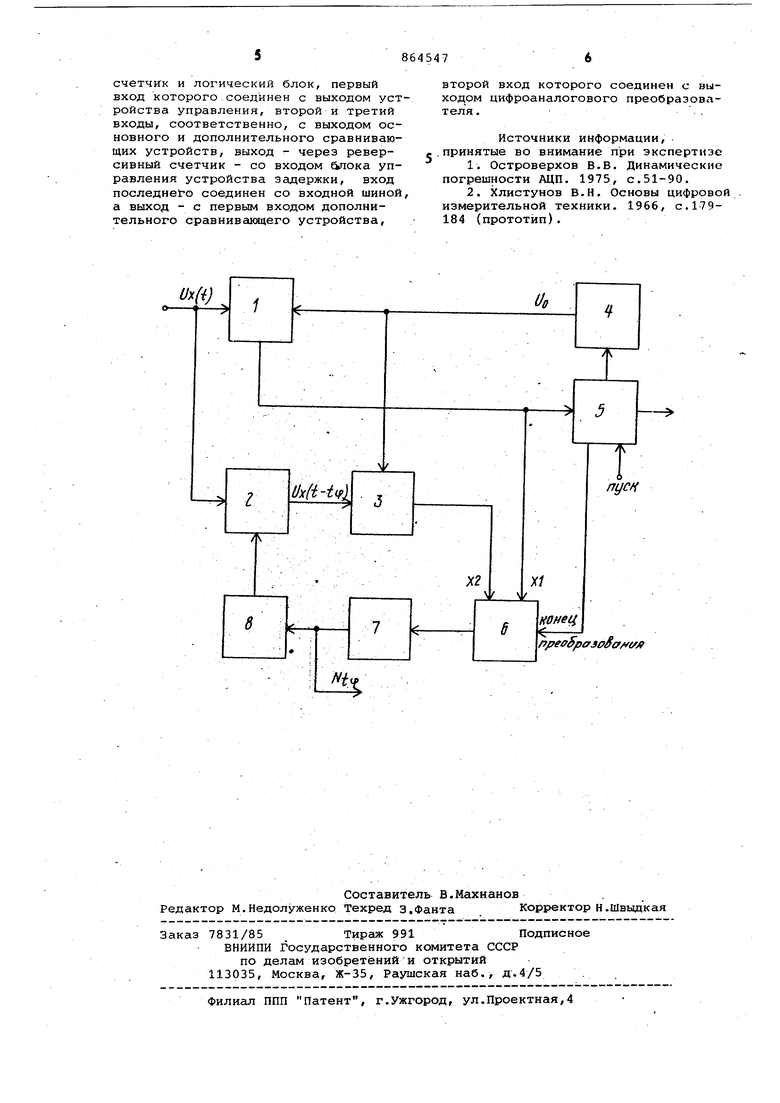

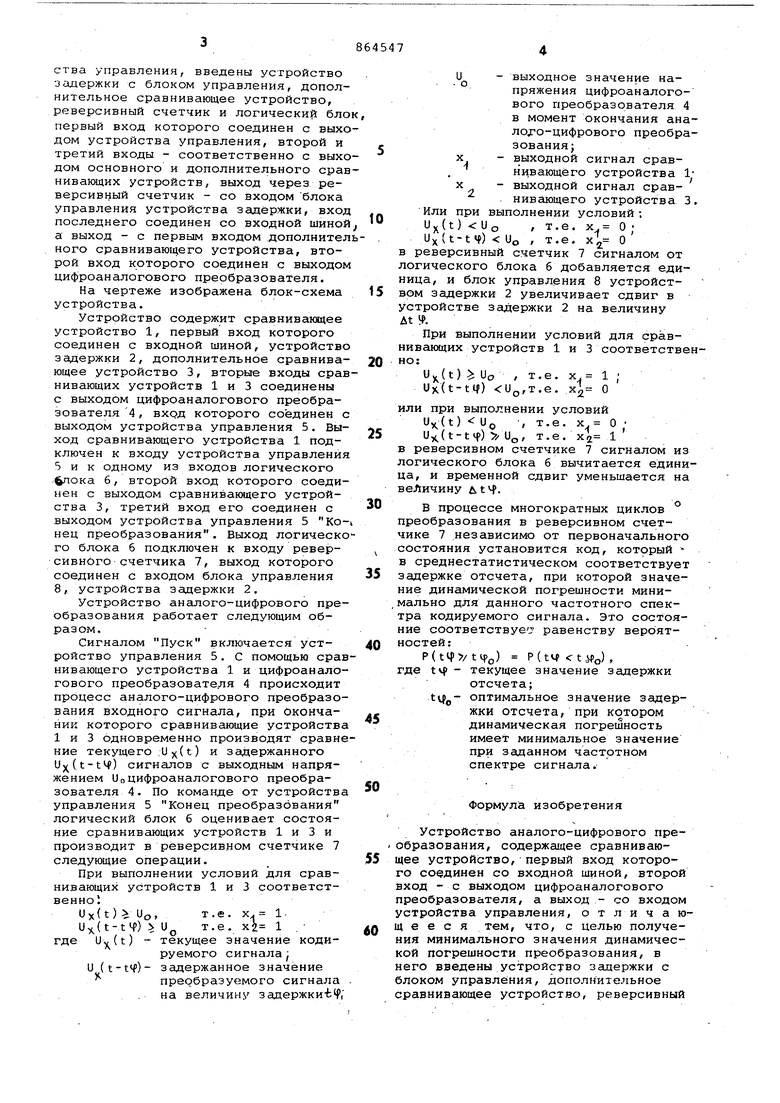

Цель достигается тем, что в уст25ройство аналого-цифрового преобразования, содержащее сравнивающее устройство, первый вход которого соединен со входной шиной, второй вход с выходом цифроаналоговрго преобразователя, а выход - со входом устрой30ства управления, введены устройство задержки с блоком управления, дополнительное сравнивающее устройство, реверсивный счетчик и логический бло первый вход которого соединен с выхо дом устройства управления, второй и третий входы - соответственно с выхо дом основного и дополнительного срав нивающих устройств, выход через реверсивный счетчик - со входом блока управления устройства задержки, вход последнего соединен со входной шинoй а выход - с первым входом дополнител ного сравнивающего устройства, второй вход которого соединен с выходом дифроан алогового преобразователя, На чертеже изображена блок-схема устройства. Устройство содержит сравнивающее устройство 1, первый вход которого соединен с входной шиной, устройство задержки 2, дополнительное сравнивающее устройство 3, вторые входы срав нивающих устройств 1 и 3 соединены с выходом цифроаналогового преобразователя 4, вхрд которого соединен с выходом устройства управления 5. Выход сравнивающего устройства 1 подключен к входу устройства управления 5 и к одному из входов логического ока 6, второй вход которого соединен с выходом сравнивающего устройства 3, третий вход его соединен с выходом устройства управления 5 Koнец преобразования. Выход логическо го блока 6 подключен к входу реверсивного счетчика 7, выход которого соединен с входом блока управления 8, устройства задержки 2. Устройство аналого-цифрового преобразования работает следующим образом. Сигналом Пуск включается устройство управления 5. С помощью срав нивающего устройства 1 и цифроаналогового преобразователя 4 происходит процесс аналого-цифрового преобразования входного сигнала, при окончании которого сравнивающие устройства 1 и 3 одновременно производят сравне ние текущего .иx(t) и задержанного ) сигналов с выходным напряжением иоцифроаналогового преобразователя 4. По команде от устройства управления 5 Конец преобразования логический блок 6 оценивает состояние сравнивающих устройств 1 и 3 и производит в реверсивном счетчике 7 следующие операции. При выполнении условий для сравнивающих устройств 1 и 3 соответственнойUx(t) Uo, т.е. х 1U4(t-t4) и. где Ux,(t) - текущее значение кодируемого сигнала| и (t-t4)- задержанное значение преобразуемого сигнала . на величину задержки-Ьф, и - выходное значение напряжения цифроаналогового преобразователя 4 в момент окончания аналод:о-цифрового преобразования;X - выходной сигнал срав. нивающёго устройства X - выходной сигнал сравнивающёго устройства 3. Или при выполнении условий; Uj(t)Uo ,т.е. x 0 Ux(t-tЧ) Uo , т.е, к О в реверсивный счетчик 7 сигналом от логического блока б добавляется единица, и блок управления 8 устройством задержки 2 увеличивает сдвиг в устройстве задержки 2 на величину At 1. При выполнении условий для сравнивающих устройств 1 и 3 соответственно:) $: Uo , т.е. Ux(t-tif) Uo,T.e. х О или при выполнении условий U(t) UQ , т.е. X О ; Ux(t-t4) Uo, т.е. xi 1 в реверсивном счетчике 7 сигналом из логического блока 6 вычитается единица, и временной сдвиг уменьшается на величину At Ч. В процессе многократных циклов преобразования в реверсивном счетчике 7 независимо от первоначального состояния установится код, который в среднестатистическом соответствует задержке отсчета, при которой значение динамической погрешности минимально для данного частотного спектра кодируемого сигнала. Это состояние соОтветствуе равенству вероятностей:P() P(tM ctiPo) где tvf - текущее значение задержки отсчета; ,- оптимальное значение задержки отсчета, при котором динамическая погрешность имеет минимальное значение при заданном частотном спектре сигнала. Формула изобретения Устройство аналого-цифрового преобразования, содержащее сравнивающее устройство, первый вход которого соединен со входной шиной, второй вход - с выходом цифроаналогового преобразователя, а выход - со входом устройства управления, отличающееся тем, что, с целью получения минимального значения динамической погрешности преобразования, в него введены устройство задержки с блоком управления, дополнительное сравнивающее устройство, реверсивный

счетчик и логический блок, первый вход которого соединен с выходом устройства управления, второй и третий входы, соответственно, с выходом основного и дополнительного сравнивающих устройств, выход - через реверсивный счетчик - со входом блока управления устройства задержки, вход последнего соединен со входной шиной а выход - с первым входом дополнительного сравнивающего устройства.

второй вход которого соединен с выходом цифроаналогового преобразователя .

Источники информации, .принятые во внимание при экспертизе 1. Островерхов В.В. Динамические погрешности АЦП. 1975, с.51-90.

Авторы

Даты

1981-09-15—Публикация

1979-11-26—Подача