Изобретение относится цифровой электроизмерительной технике и может быть использовано в цифровых измерительных приборах и информационных измерительных системах.

Цель изобретения - повышение точности и помехозащищенности.

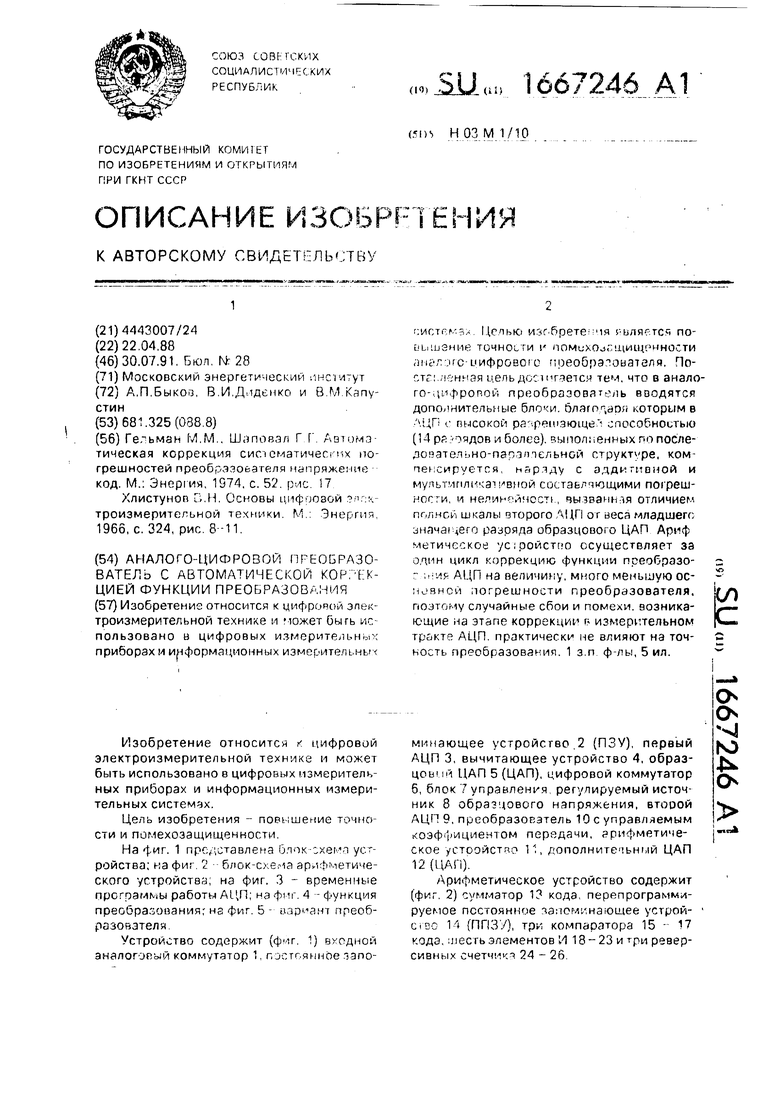

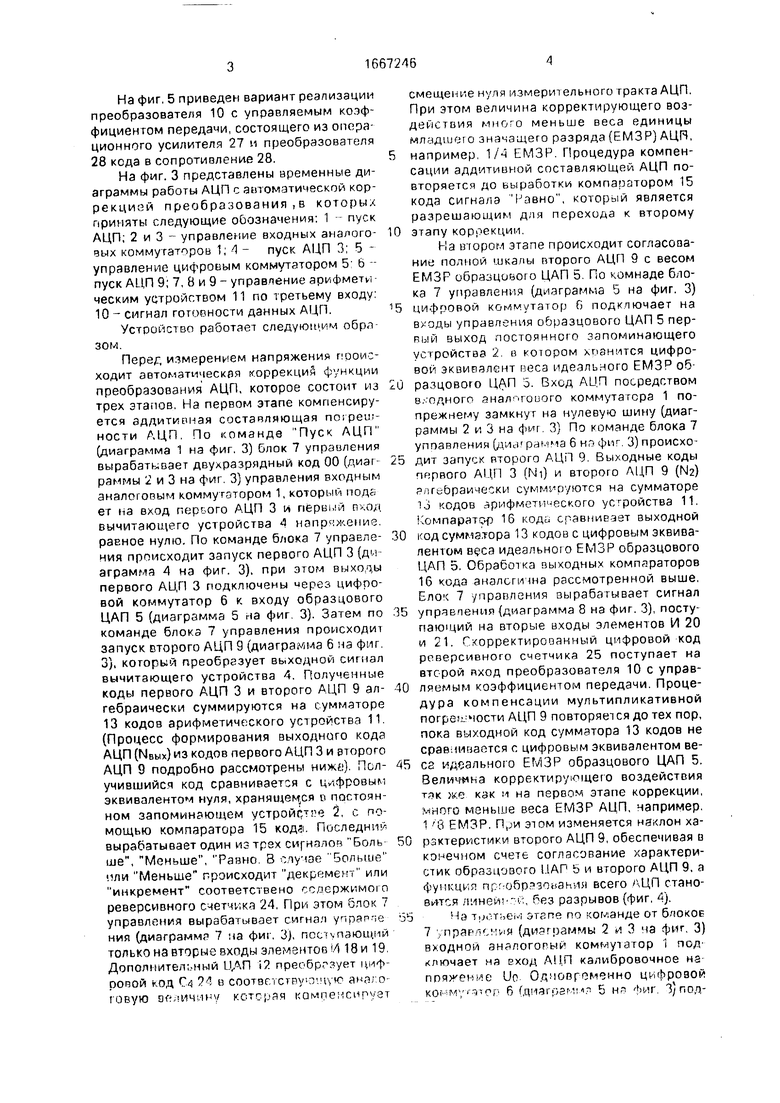

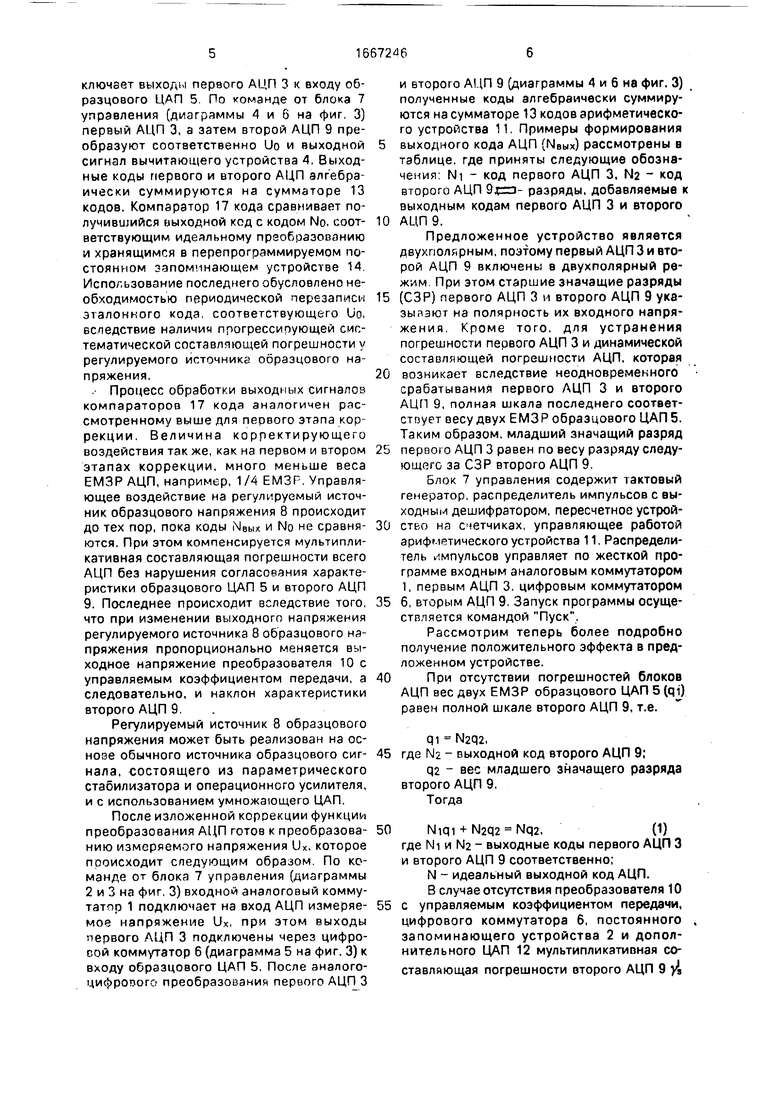

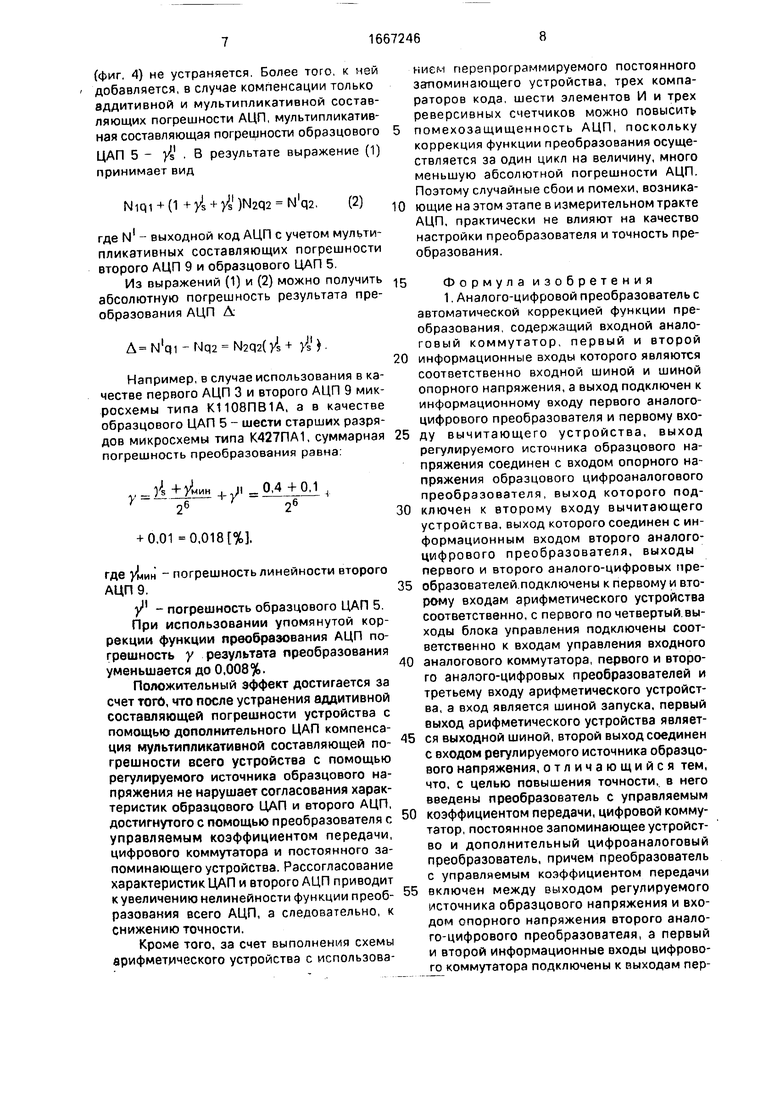

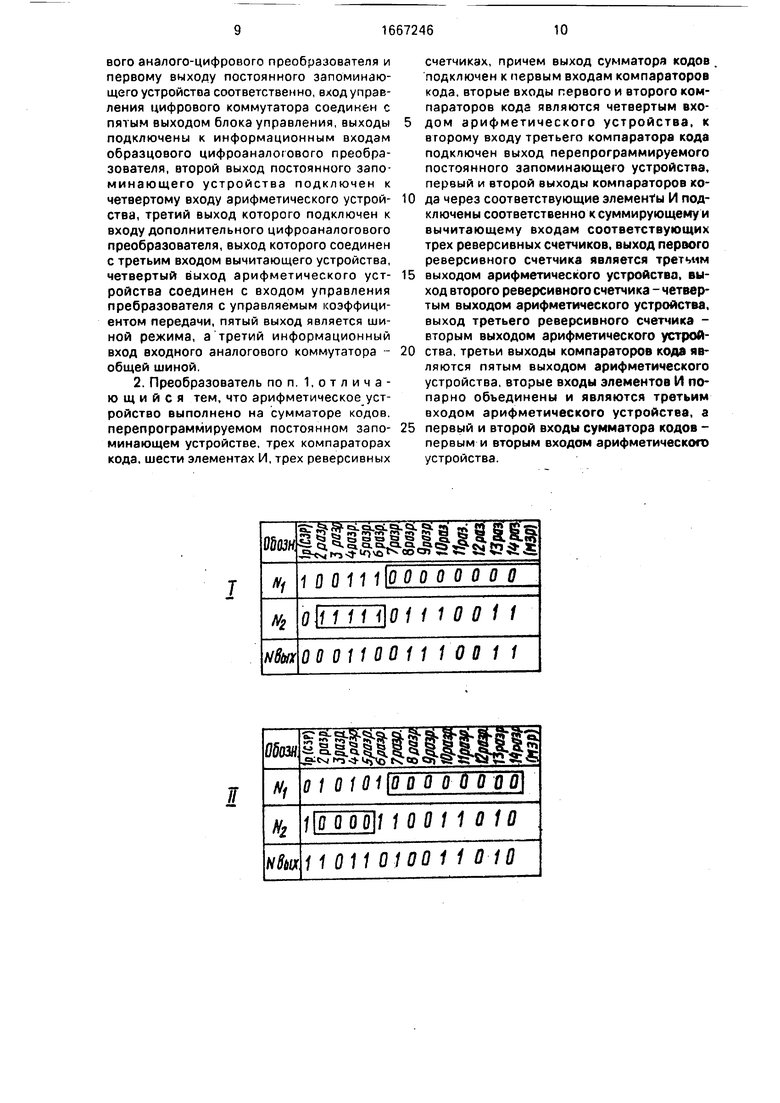

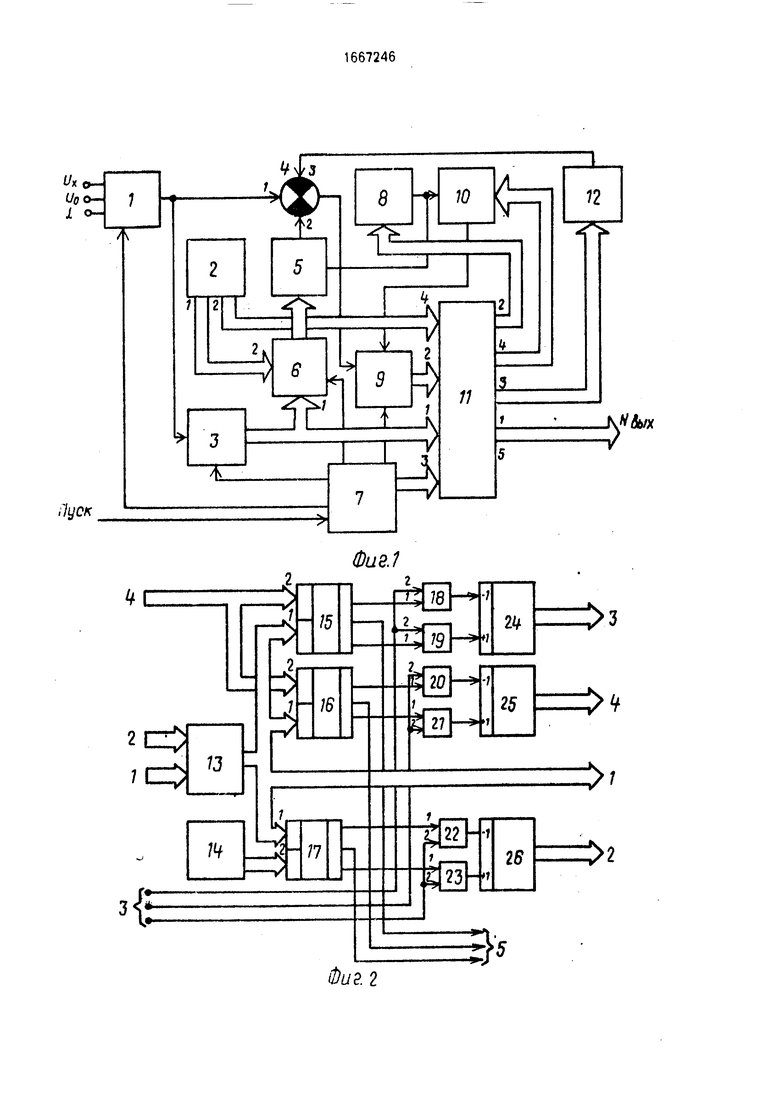

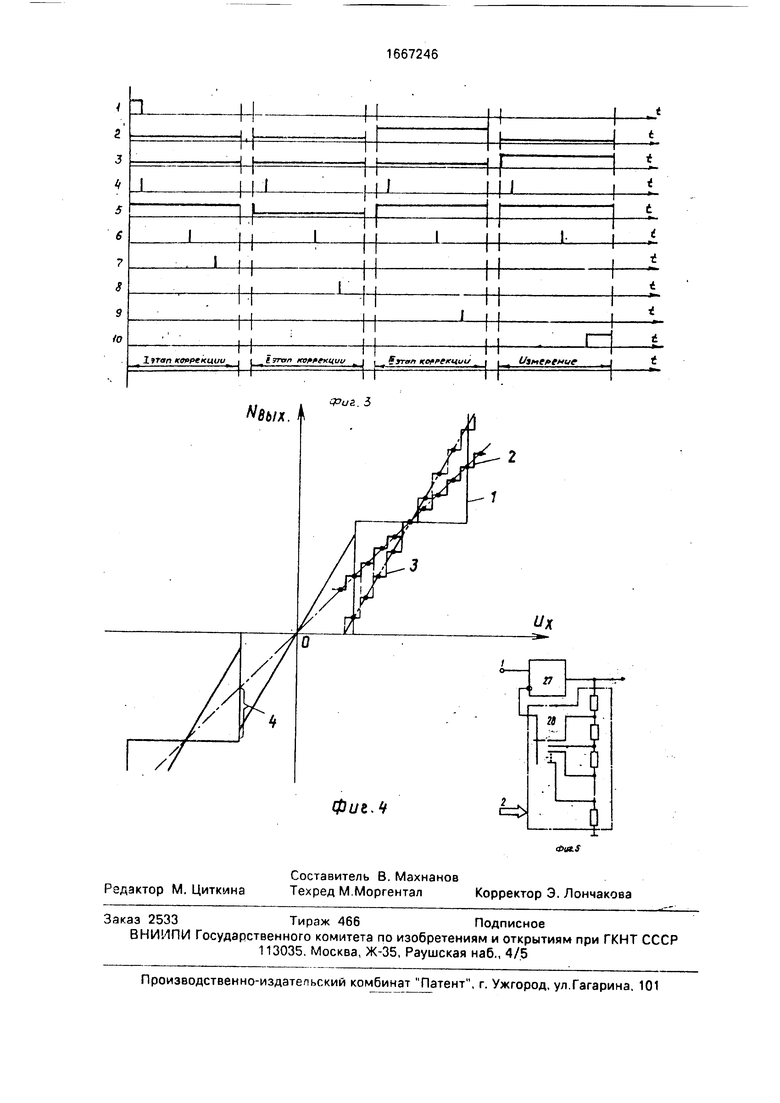

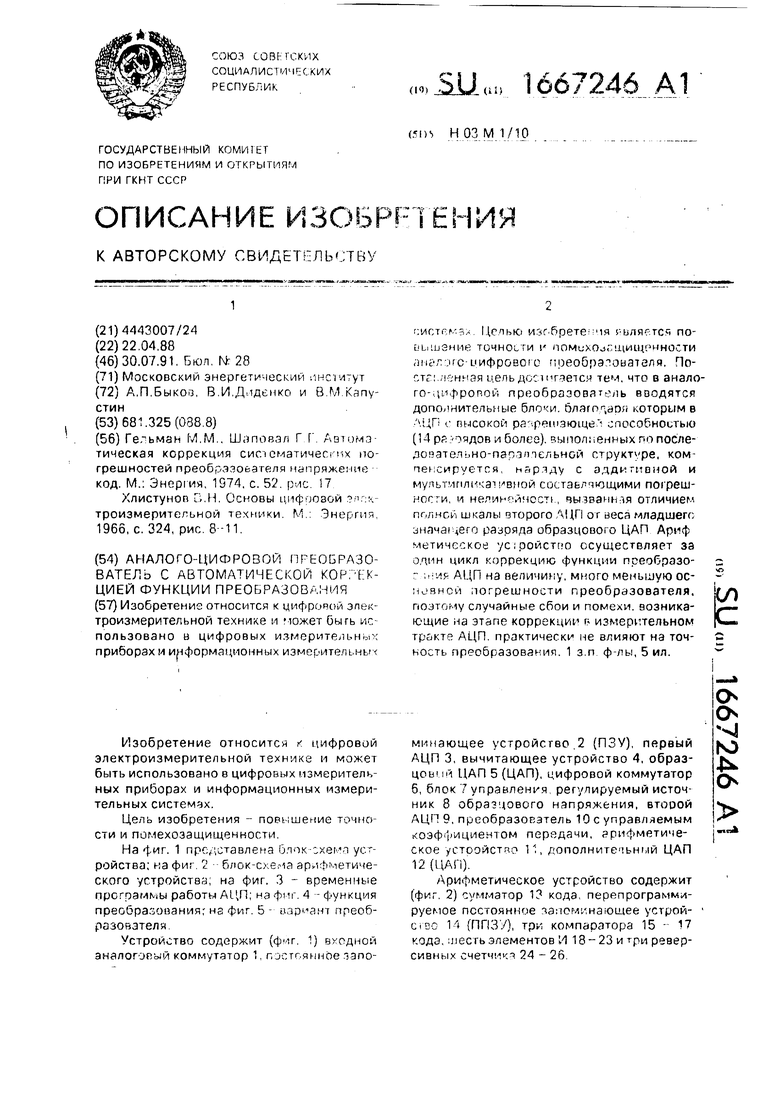

На фиг. 1 представлена Опок :хегм устройства; на фиг 2 блок-схе.ча арифметического устройства, на фиг. 3 - временные программы работы АЦП; на фиг 4 -функция преобразования; на фиг 5- tiap- am преобразователя

Устройство содержит (фиг 1) входной аналоговый коммутатор 1, постоянное запоминающее устройство 2 (ПЗУ), первый АЦП 3, вычитающее устройство 4, образцов1 1й ЦАП 5 (ЦАП), цифровой коммутатор 6, блок /управления регулируемый источник 8 образцового напряжения, второй АЦП 9, преобразователь 10с управляемым коэффициентом передачи, ррифметиче- ское устоойстпс 11, /юполнитечьнмй ЦАП 12 (ЦАП).

Арифметическое устройство содержит (фиг. 2) сумматор 1 кода, перепрограммируемое постоянное запоминающее устрой- CIGC И (ППЗД три компаратора 15 - 17 кода, uiecrb элементов И 18-23 и три реверсивных счетчик 24 - 26

О

о

х|

ю

Јь

о

На фиг, 5 приведен вариант реализации преобразователя 10 с управляемым коэффициентом передачи, состоящего из опера ционного усилителя 27 и преобразователя 28 кеда в сопротивление 28.

На фиг. 3 представлены временные диаграммы работы АЦП с автоматической коррекцией преобразования которых приняты следующие обозначения: 1 пуск АЦП, 2 и 3 - управление входных аналоговых коммутаторов 1,1- пуск АЦП 3, 5 - управление цифровым коммутатором 5 b пуск АЦП 9; 7, 8 и 9 - улравпение арифмети ческим устройством 11 по третьему входу 10 - сигнал готовности данных АЦП.

Устройство работает следующим обра

30 М

Перед измерением напряжения РООИ;- ходит автоматическая коррекций функции преобразования АЦП, которое состоит из трех этапов На первом этапе компенсируется аддитиЕ1ная составляющая nospeui- ности АЦП По команде Пуск АЦП (диаграмма 1 на фиг, 3) Олок 7 управления вырабатывает двухразрядный код 00 (диаг раммы 2 и 3 на фиг 3) управления входным аналоювым коммутатором 1, который поде ег на вход первого АЦП 3 и первой вычитающего устройства з напряжение равное нулю. По команде блока 7 управления происходит запуск первого АЦП 3 (дм аграмма 4 на фиг. 3), при этом выходы первого АЦП 3 подключены через цифпо- вой коммутатор 6 к входу образцового ЦАП 5 (диаграмма 5 на фиг 3). Затем по команде блока 7 управления происходит запуск второго АЦП 9 (диаграмма 6 на фиг 3), который преобразует выходной сигнал вычитающего устройства 4. Полученные коды первого АЦП 3 и второго АЦП 9 алгебраически суммируются на сумматоре 13 кодов арифметического устройства 11 (Процесс формирования выходного кода АЦП (Мвых) из кодов первого АЦП 3 и второго АЦП 9 подробно рассмотрены ниже) Получившийся код сравнивается с цифровым эквивалентом нуля, хранящемся ц постоянном запоминающем устроимте 2, с помощью компаратора 15 кода Последние вырабатывает один из трех сигналов Боль ше, Меньше, Равно 8 опучае Больше или Меньше происходит декремент1 или инкремент соответствено слержимо1 о реверсивного счет-и.ка 24, При этом блок 7 управления вырабатывает сигнал упрап-.е нип (диаграмм 7 ма фи, 3), посылающий только на вторые входы элементов 118 и 19 Дополнительный ЦАП 7 преобразует циф ровой год ( Ул в соотвг icrnyiT uf1 anpj о ювую af-. Ич n-v кстсрач компенсирует

смещение нуля измерительного тракта АЦП При этом величина корректирующего воздействия мною меньше веса единицы младшего значащего разряда (ЕМЗР) АЦП,

например 1/ч ЕМЗР Процедура компенсации аддитивной составляющей АЦП повторяется до выработки компаоатором 15 кода сигнала Равно, который является разрешающим для перехода к второму

0 этапу коррекции

На втором этапе происходит согласование полной шкапы второго АЦП 9 с весом ЕМЗГ образцового ЦАП 5 По комнаде блока 7 управления (диаграмма 5 на фиг. 3)

5 цифровой коммутатор С; подключает на входы управления образцового ЦАП 5 первый выход постоянною запоминающего устройства J в котором хпанится цифровой эквивалент иеса идеального ЕМЗР об

и разцового ПАП 5 Вход посредством в одного анал rouoro коммутатора 1 по- прежнему замкнут на нулевую шину (диаграммы 2 и 3 на фиг 3} По команде блока 7 уппавления (диаг pat ма 6 нг фиг 3) происхо5 дит запуск второго АЦП 9 Выходные коды пррвого АЦП 3 (Ni) и второго АЦП 9 (N2) )ГйЬраически су мм и о /юте я ча сумматоре 1 j кодов арифмети -еского устройства 11 .омпарат7 р 16 коде, сравнивает выходной

0 код сумматора 13 кодов с цифровым эквивалентом веса идеального ЕМЗР образцового ЦАП 5, Обработка выходных компараторов 16 кода аналоги 1на рассмотренной выше, Елоч 7 управления вырабатывает сигнал

5 управления {диаграмма 8 на фиг 3), поступающий на вторые входы элементов И 20 и 21. Г орректирооанный цифровой код реверсивного счетчика 25 поступает на втсрой пход преобразователя 10 с управ0 ляемым коэффициентом передачи Процедура компенсации мультипликативной погрег- мости АЦП 9 повторяется до тех пор, пока выходной код сумматора 13 кодов не срав шваотся с цифровым эквивалентом ве5 сг идеальною ЕМЗР образцового ЦАП 5, Величина корректирующею воздействия хке как и на первом этапе коррекции, много меньше веса ЕМЗР АЦП, например 1 8 ЕМЗР n,jn этом изменяется наклон ха0 рзктеристики ВТОРОГО АЦП 9, обеспечивая в конечном счете согласование характеристик образцового ПАР b и второго АЦП 9, а пг о&р зонаи ui всего ЛЦП становится линей1 -I Рез разрывов (фиг, &)

ЪНа тигт eivi тгпе по команде от бчокое

7 прарт,ир (диаграммы 2 и 3 ча фиг 3) в однои аналогогыи коммутатор 1 под ключает на вход АИП калибровочное на пряжение Uo Оцчовроменно цифровой ко м1 -п, 6 Сцчзгоа i 1 5 и-14 3} подключзет выходи первого АЦП 3 к входу образцового ЦАП 5 По команде от блока 7 управления (диаграммы 4 и 6 на фиг, 3) первый АЦП 3, а затем второй АЦП 9 преобразуют соответственно Uo и выходной сигнал вычитающего устройства 4. Выходные коды первого и второго АЦП алгебраически суммируются на сумматоре 13 кодов. Компаратор 17 кода сравнивает получившийся выходной код с кодом No, соответствующим идеальному преобразованию и хранящимся в перепрограммируемом постоянном запоминающем устройстве 14 Использование последнего обусловлено необходимостью периодической перезаписи эталонного кода, соответствующего Uo, вспедствие наличия прогрессиоующей систематической составляющей погрешности у регулируемого источника образцового напряжения.

Процесс обработки выходных сигналов компараторов 17 кода аналогичен рассмотренному выше для первого этапа коррекции. Величина корректирующего воздействия так же, как на первом и втором этапах коррекции, много меньше веса ЕМЗР АЦП, например, 1/4 ЕМЗГ. Управляющее воздействие на регулируемый источник образцового напряжения 8 происходит до тех пор, пока коды Мвых и No не сравняются. При этом компенсируется мультипликативная составляющая погрешности всего АЦП без нарушения согласования характеристики образцового ЦАП 5 и второго АЦП 9. Последнее происходит вследствие того, что при изменении выходного напряжения регулируемого источника 8 образцового напряжения пропорционально меняется выходное напряжение преобразователя 10 с управляемым коэффициентом передачи, а следовательно, и наклон характеристики второго АЦП 9.

Регулируемый источник 8 образцового напряжения может быть реализован на ос- нозе обычного источника образцового сигнала, состоящего из параметрического стабилизатора и операционного усилителя, и с использованием умножающего ЦАП.

После изложенной коррекции функции преобразования АЦП готов к преобразованию измеряемого напряжения U, которое ПРОИСХОДИТ следующим образом По команде от блока 7 управления (диаграммы 2 и 3 на фиг, 3) входной аналоговый коммутатор 1 подключает на вход АЦП измеряемое напряжение Ux, при этом выходы первого АЦП 3 подключены через цифровой коммутатор 6 (диаграмма 5 на фиг. 3) к входу образцового ЦАП 5. После аналого- цифрового преобразования первого АЦП 3

и второго АЦП 9 (диаграммы 4 и 6 на фиг. 3) полученные коды алгебраически суммируются на сумматоре 13 кодов арифметического устройства 11. Примеры формирования выходного кода АЦП (NBbix) рассмотрены в таблице, где приняты следующие обозначения NI - код первого АЦП 3, N2 - код второго АЦП 9Јгэ- разряды, добавляемые к выходным кодам первого АЦП 3 и второго

АЦП 9.

Предложенное устройство является двухполйрным, поэтому первый АЦП 3 и второй АЦП 9 включены в двухполярный режим При этом старшие значащие разряды

(СЭР) первого АЦП 3 и второго АЦП 9 указывают на полярность их входного напряжения Кроме того, для устранения погрешности первого АЦП 3 и динамической составляющей погрешности АЦП, которая

возникает вследствие неодновременного срабатывания первого АЦП 3 и второго АЦП 9, полная шкала последнего соответствует весу двух ЕМЗР образцового ЦАП 5. Таким образом, младший значащий разряд

перво о АЦП 3 равен по весу разряду следующего за СЭР второго АЦП 9.

Блок 7 управления содержит тактовый генератор, распределитель импульсов с выходным дешифратором, пересчетное устройстьо на с (етчиках, управляющее работой арифмртического устройства 11. Распределитель импульсов управляет по жесткой программе входным аналоговым коммутатором 1, первым АЦП 3. цифровым коммутатором

б, вторым АЦП 9, Запуск программы осуществляется командой Пуск,

Рассмотрим теперь более подробно получение положительного эффекта в предложенном устройстве.

При отсутствии погрешностей блоков АЦП вес двух ЕМЗР образцового ЦАП 5 (qi) равен полной шкале второго АЦП 9, т.е.

Q1 N2Q2, где NZ - выходной код второго АЦП 9;

q2 - вес младшего значащего разряда второго АЦП 9, Тогда

Niqi + N2Q2 Nq2,(1)

где Mi и N2 - выходные коды первого АЦП 3 и второго АЦП 9 соответственно;

N - идеальный выходной код АЦП.

В случае отсутствия преобразователя 10

с управляемым коэффициентом передачи, цифрового коммутатора 6, постоянного , запоминающего устройства 2 и дополнительного ЦАП 12 мультипликативная составляющая погрешности второго АЦП 9 4

(фиг. 4) не устраняется. Более того, к май добавляется, в случае компенсации только аддитивной и мультипликативной составляющих погрешности АЦП, мультипликативная составляющая погрешности образцового

ЦАП 5 - ys . В результате выражение (1) принимает вид

Niqi + (1 + yl + уУ )N2Q2 N q2, (2)

где N1 - выходной код АЦП с учетом мультипликативных составляющих погрешности второго АЦП 9 и образцового ЦАП 5,

Из выражений (1) и (2) можно получить абсолютную погрешность результата преобразования АЦП Л:

A N qi-Nq2 N2q2(yi+ уУ

Например, в случае использования в качестве первого АЦП 3 и второго АЦП 9 микросхемы типа К1108ПВ1А, а в качестве образцового ЦАП 5 - шести старших разрядов микросхемы типа К427ПА1, суммарная погрешность преобразования равна

у гА+Умин . л 0.4 +0,1 2бУ2б

+ 0,01 - 0,018 %.

где УМИН - погрешность линейности второго АЦП 9.

у - погрешность образцового ЦАП 5.

При использовании упомянутой коррекции функции преобразования АЦП погрешность у результата преобразования уменьшается до 0,008%.

Положительный эффект достигается за счет того, что после устранения аддитивной составляющей погрешности устройства с помощью дополнительного ЦАП компенсация мультипликативной составляющей погрешности всего устройства с помощью регулируемого источника образцового напряжения не нарушает согласования характеристик образцового ЦАП и второго АЦП, достигнутого с помощью преобразователя с управляемым коэффициентом передачи, цифрового коммутатора и постоянного запоминающего устройства. Рассогласование характеристик ЦАП и второго АЦП приводит к увеличению нелинейности функции преобразования всего АЦП, а следовательно, к снижению точности.

Кроме того, за счет выполнения схемы арифметического устройства с использованием перепрограммируемого постоянного запоминающего устройства, трех компараторов кода, шести элементов И и трех реверсивных счетчиков можно повысить

помехозащищенность АЦП, поскольку коррекция функции преобразования осуществляется за один цикл на величину, много меньшую абсолютной погрешности АЦП. Поэтому случайные сбои и помехи, возникающие на этом этапе в измерительном тракте АЦП, практически не влияют на качество настройки преобразователя и точность преобразования.

Формула изобретения

1. Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования, содержащий входной аналоговый коммутатор, первый и второй

информационные входы которого являются соответственно входной шиной и шиной опорного напряжения, а выход подключен к информационному входу первого аналого- цифрового преобразователя и первому входу вычитающего устройства, выход регулируемого источника образцового напряжения соединен с входом опорного напряжения образцового цифроаналогового преобразователя, выход которого подключей к второму входу вычитающего устройства, выход которого соединен с информационным входом второго аналого- цифрового преобразователя, выходы первого и второго аналого-цифровых иреобразователей подключены к первому и второму входам арифметического устройства соответственно, с первого по четвертый выходы блока управления подключены соответственно к входам управления входного

аналогового коммутатора, первого и второго аналого-цифровых преобразователей и третьему входу арифметического устройства, а вход является шиной запуска, первый выход арифметического устройства является выходной шиной, второй выход соединен с входом регулируемого источника образцового напряжения, отличающийся тем, что, с целью повышения точности, в него введены преобразователь с управляемым

коэффициентом передачи, цифровой коммутатор, постоянное запоминающее устройство и дополнительный цифроаналоговый преобразователь, причем преобразователь с управляемым коэффициентом передачи

включен между выходом регулируемого источника образцового напряжения и входом опорного напряжения второго аналого-цифрового преобразователя, а первый и второй информационные входы цифрового коммутатора подключены к выходам первого аналого-цифрового преобразователя и первому выходу постоянного запоминающего устройства соответственно, вход управления цифрового коммутатора соединен с пятым выходом блока управления, выходы подключены к информационным входам образцового цифроаналогового преобразователя, второй выход постоянного запоминающего устройства подключен к четвертому входу арифметического устрой- ства, третий выход которого подключен к входу дополнительного цифроаналогового преобразователя, выход которого соединен с третьим входом вычитающего устройства, четвертый выход арифметического уст- ройства соединен с входом управления пребразователя с управляемым коэффициентом передачи, пятый выход является шиной режима, а третий информационный вход входного аналогового коммутатора - общей шиной.

2. Преобразователь по п. 1,отличающий с я тем, что арифметическое устройство выполнено на сумматоре кодов, перепрограммируемом постоянном запо- минающем устройстве, трех компараторах кода, шести элементах И, трех реверсивных

счетчиках, причем выход сумматора кодов подключен к первым входам компараторов кода, вторые входы первого и второго компараторов кода являются четвертым входом арифметического устройства, к второму входу третьего компаратора кода подключен выход перепрограммируемого постоянного запоминающего устройства, первый и второй выходы компараторов кода через соответствующие элементы И подключены соответственно к суммирующему и вычитающему входам соответствующих трех реверсивных счетчиков, выход первого реверсивного счетчика является третьим выходом арифметического устройства, выход второго реверсивного счетчика - четвертым выходом арифметического устройства, выход третьего реверсивного счетчика - вторым выходом арифметического устройства, третьи выходы компараторов кода являются пятым выходом арифметического устройства, вторые входы элементов И попарно объединены и являются третьим входом арифметического устройства, а первый и второй входы сумматора кодов - первым и вторым входом арифметического устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2334355C1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

| Устройство для автоматического определения динамических характеристик аналого-цифровых преобразователей | 1985 |

|

SU1288909A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1690197A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| ДАТЧИК ДАВЛЕНИЯ | 2013 |

|

RU2523754C1 |

| Интегрирующий аналого-цифровой преобразователь | 1981 |

|

SU982191A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых измерительных приборах и информационных измерительных системах. Целью изобретения является повышение точности и помехозащищенности аналого-цифрового преобразователя. Поставленная цель достигается тем, что в аналого-цифровой преобразователь вводятся дополнительные блоки, благодаря которым в АЦП с высокой разрешающей способностью (14 разрядов и более), выполненных по последовательно-параллельной структуре, компенсируются, наряду с аддитивной и мультипликативной составляющими погрешности, и нелинейность, вызванная отличием полной шкалы второго АЦП от веса младшего значащего разряда образцового ЦАП. Арифметическое устройство осуществляет за один цикл коррекцию функции преобразования АЦП на величину, много меньшую основной погрешности преобразователя, поэтому случайные сбои и помехи, возникающие на этапе коррекции в измерительном тракте АЦП, практически не влияют на точность преобразования. 1 з.п. ф-лы, 5 ил.

Об(Ш

1

10011 ПО О О О О О О О

000110011 10В 1 1

0бШ

ST iS-ecSf.

9{/т

щ

О 1 0 О О О О 00

NBblX

1 1011 010011 0 10

9{Фиг 2

Нвыя.

Фиг. 3

фиьЛ

| Гегьман М.М | |||

| Шаповэл Г Г Автомэ тическая коррекция сиглсматичег, х погрешностей преобразователя напряжение код | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Двухтактный двигатель внутреннего горения | 1924 |

|

SU1966A1 |

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

Авторы

Даты

1991-07-30—Публикация

1988-04-22—Подача