(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля магнитных накопителей | 1982 |

|

SU1095232A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Способ автоматического контроляМАгНиТНыХ НАКОпиТЕлЕй C зАпиСьюСигНАлОВ пО дВуМ уРОВНяМ и C пЕРЕК-лючЕНиЕМ пОТОКА пРи зАпиСи ЕдиНиц | 1978 |

|

SU794670A1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875474A1 |

| Устройство для контроля многоканального накопителя на магнитной ленте | 1980 |

|

SU930374A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| Устройство для контроля многоканального аппарата магнитной записи | 1985 |

|

SU1310895A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство для обработки и ввода экспериментальный данных в вичислительную машину | 1975 |

|

SU541162A1 |

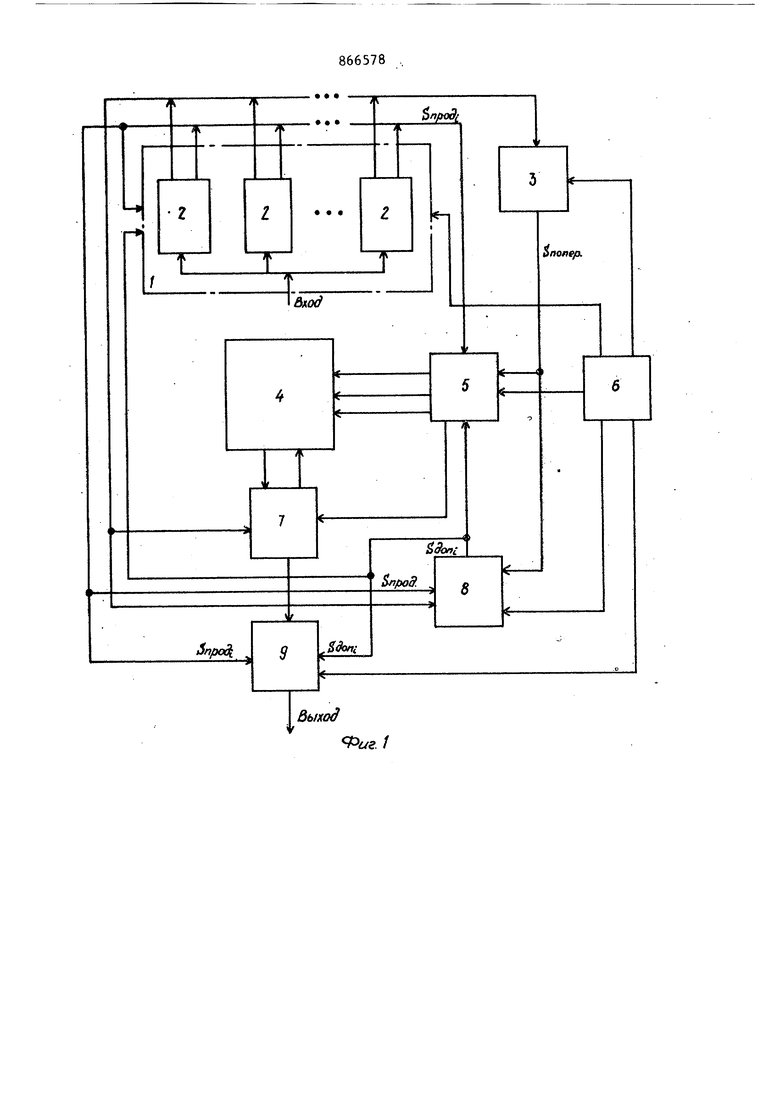

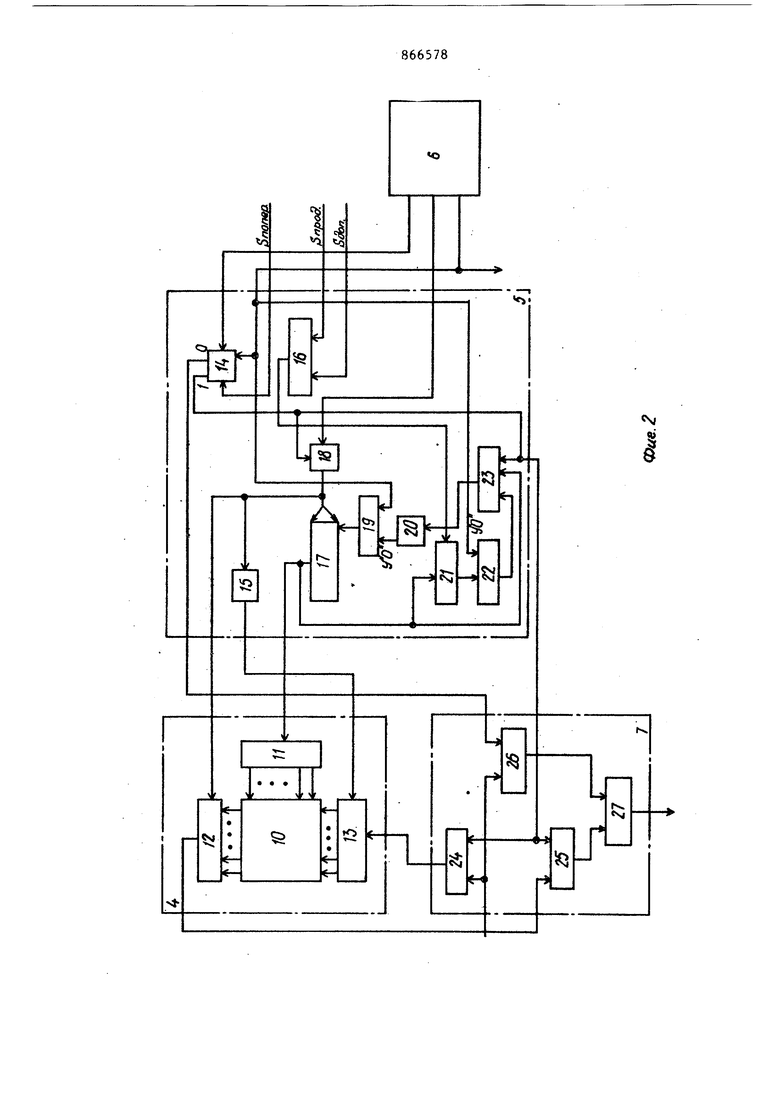

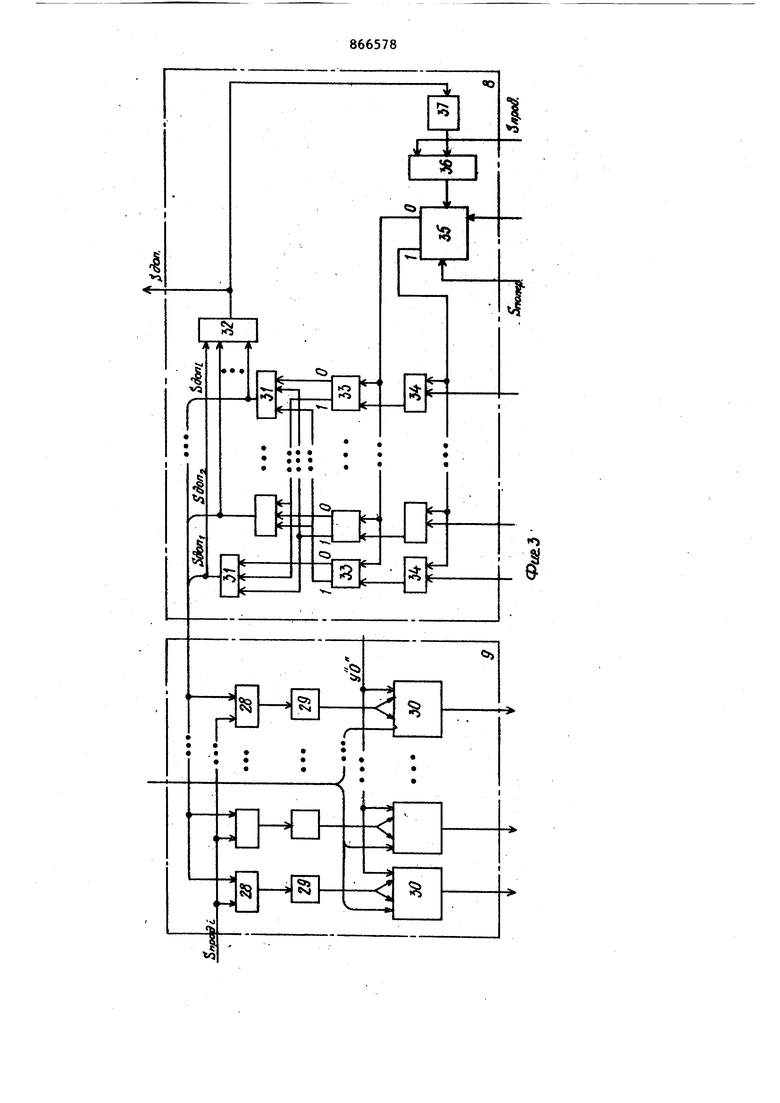

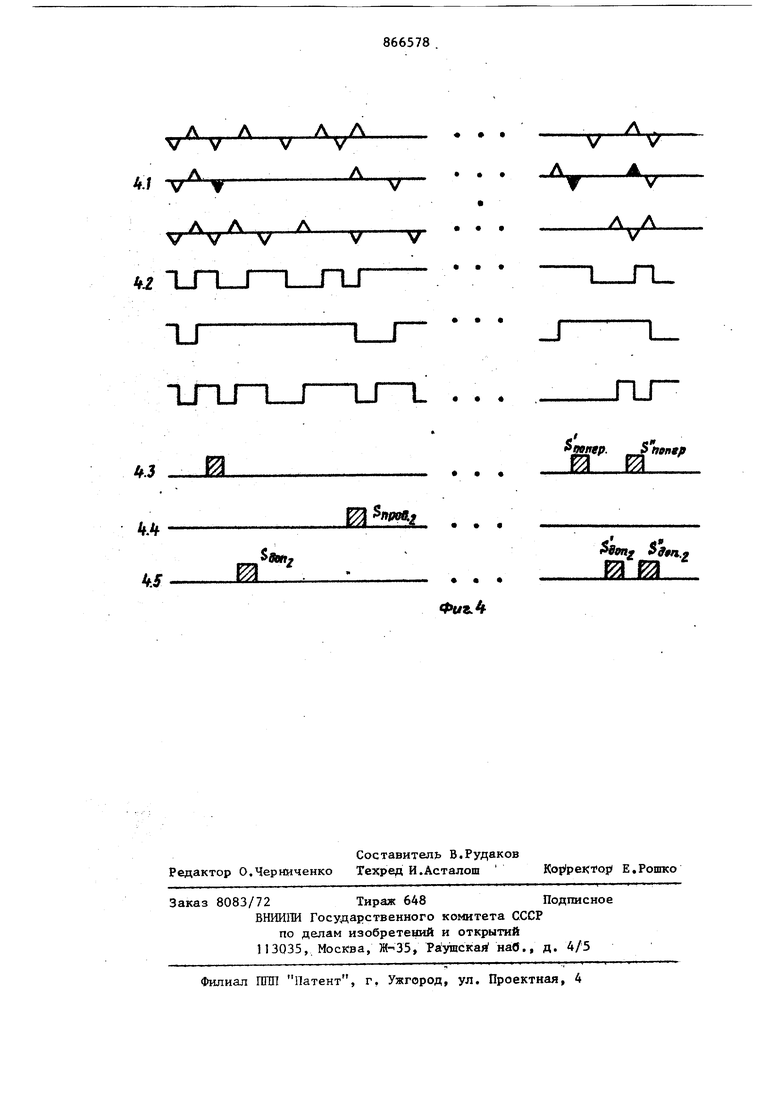

Изобретение относится к запоминающим устройствам и может быть исполь зовано ВО внешних запоминающиз устройствах вычислительных машин и управляющих систем. Известно устройство для контроля магнитных накопителей, содержащее триггер записи, блок управления, усилитель воспроизведения разнополярных .импульсов, элементы задержки, элемен1ты ИЛИ и И 13. Недостатком этого устройства является невысокое быстродействие. Наиболее близким к изобретению по технической супцюсти является устройство для контроля магнитных накопителей, содержащее блоки поканального контроля, форг-афователь сигнала опшбки, буферный накопитель, блок местного управления, блок коммутации, блок коррекции, формирователь дополнительного сигнала ошибки и блок управления r2J. Недостатками известного устройства являются большие аппаратурные затраты невысокое быстродействие, в случае наличия длительных последовательностей нулей в воспроизведенных с накопителя сигналах. Цель изобретения - упрощение устройства и повышение оперативности контроля. Поставленная цель достигается тем, Что в устройстве для контроля магнитных накопителей, содержащем группу блоков поканального контроля, формирователь сигнала ошибки, буферный накопитель, блок местного управления, блок коммутации, блок коррекции, формирователь дополнительного сигнала ошибки и блок управления, причем выходы блоков поканального контроля подключены соответственно ко входу формирователя сигнала ошибки, первым входам блока местного управления, блока коммутации, блока коррекции и формирователя дополнительного сигнала ошибки и одним из входов блоков пока нального контроля, выход формировате ля сигнала ошибки соединен со вторым вxoдa и блока местного управления и формирователя дополнительного сигнал ошибки, выход которого подключен к третьему входу блокаjместного управл .НИН, первый и второй выходы которого и первый выход блока коммутации подключены к соогветствуюпщм входам буф рного накопителя, выход которого сое динен со вторым входом блока коммута ции, выход которого подключен ко вто рому входу блока коррекции, третий вход которого соединен с выходом фор мирователя дополнительного сигнала ошибки, управляющие входы формироват ля сигнала ошибки, блоков поканального контроля, блока местного управления, формирователя дополнительного сигнала ощибки и блока коррекции под ключены к выходам блока управления, в нем третий и четвертый выходы блока местного управления прдключень соответственно к другому входу буферного накопителя и третьему входу блока коммутации, выход формирователя дополнительного сигнала ошибки соединен с другими входами блоков поканального контроля, одни из выходов которых подключены к третьему входу формирователя дополнительного сигнала ошибки, На фиг. 1 изображена структурная схема предлагаемого устройстваj на фиг. 2 - структурные схемы буферного накопителя, блока местного управления и блока коммутации; на фиг, 3 структурные формирователя дополнительного сигнала ошибки и блока коррекции; на фиг. 4 - временные диаграммы работы устройства. Устройство (фиг, l) содержит груп пу 1 блоков 2 поканального контроля, формирователь 3 сигнала ошибки, буферный накопитель 4, блок 5 местного управления, блок 6 управления, блок 7 коммутации, формирователь 8 дополнительного сигнала ошибки и блок 9 коррекции. Первый и второй выходы блока 5 подключены к одним из входов накопителя 4. Первый и второй входы блока 7 подключены соответственно к одним из выходов блоков 2 и выходу накопителя 4. Третий и четвертый выходы блока 5 подключены соответственно к другому входу накопителя 4 и третьему входу блока 7. Выходы блоков 2 подключены к одним из входов этих блоков, другие входы которых соединены с выходом формирователя 8, первый, второй и третий входы которого соединены с выходами блоков 2 и формирователя 3, Буферный накопитель 4 (фиг. 2) содержит запоминшощую матрицу 10, дешифратор П адреса, усилители 12 13 записи. считывания,усилители Блок 5 местного управления содержит триггер 14, элемент J5 задержки, элемент 16 ИЛИ, счетчик .17 адреса, ключ 18 элемент ИЛИ 19, .ключ 20 группу элементов 21 И,регистр 22 и группу элементов 23 И, Блок 7 коммутации содержит группы элементов И 24-26 и группу элементов 27 ШШ, Блок 9 коррекции содержит (фиг.З элементы ШШ 28, элементы задержки 29, одноразрядные регистры 30. Формирователь 8 содержит элементы И 3J, элемент ЮШ 32, регистры 33, элементы И 34, ТЕШггер 35, элемент ИЛИ 36 и элемент,задержки 37, На фиг, 4.1 изображены сигналы, подаваемые на вход устройства (защтриховань пропавшие при воспроизэедении ) J на иг. 4,2 1федста-т влены результаты суммирования по модулю два воспроизведенных импульсов, -которые получаются в каждом из блоков 2J на фиг. 4.3 изображены сигналы ошибки которые вырабатывает формирователь 3; на; фиг. 4.4 изображен сигнал ошибки дпер вырабатываемый блоками 2; на фиг. 2.5 - сигнал , вырабатываемый формироваг телем 8. Устройство работает следующим образом. Информация поступает с магнитного носителя йо t (I-N) каналам (N+ +1-ЫЙ канал - контрольный) на блоки 2, Далее информация поступает на блок 7 коммутации и формирователь 3. Если ошибки отсутствуют, то с блока коммутации 7 информация через блок :9 коррекции проходит на выход устройства неизменной. В случае появления Ошибки формирователь 3 вырабатывает сигнал ошибки Sj,Qf,gp jкоторый поступает на блок 5, формирователь 8 и блок 7 коммутации. По сигналу ошибки информация начинает поступать в накопитель 4, блок 5 начинает формирование сегмента в накопителе 4, формирователь 8 начинает анализировать последующую информацию Если в любь|Х N каналах появятся и пульсы воспроизведения, фородрова тель 8 формирует дополиительный сигнал ошибки %oii)B том канале, в, котором импульсы воспроизведения не появились, Сигнал 5, поступает на 2, блокируя появление сигнала те1А.4 блок 5, который заканчивав ет фэрмирование сегмента в накопите ле 4 и вырабатывает сигнгш на чтение информации из него. Информация из накопителя проходит через блок 7 коннутацни на блок корекцци, где содержимое сбойного разрядау находя цегосй на пересечении сбойной строки (сбойная строка записана в накопител 4 ПерЗвой) и сбойного канала, устанав ливаемого по сигналу ошибки в соотве ствующем канале с формирователем 8 инвертируется. Таким образом, информ ция с выхода блока 9 поступает на выход устройства в исправленном ви де ,, .- . Если блоки 2 вырабатывают сигнал /ошибки Sfip в канале, то он поступа ет на формирователь 8, блокируя по явление. %(}пи« на блок 4 и блок 9 коррекции, Исправление ощибки проис ходит таким же образом, как и в случае появления Svgn. Таким образом, предлагаемое изобретение позволяет повысить точность контроля за счет направления всех нечетных ошибок, в том числе нечетных ошибок, в сумме дающих четное число искаженных разрядов и разделен ных последовательностями нулей,. Кро ме того, повьййает точность локалиseaijtm ошибок за счет формирования сигнала д„ , а также повьшает быстродействие контроля. Формула изобретения Устройство для контроля магнитных накопителей, содержащее группу блоков поканального контроля, формирователь сигнала ошибки, буферный на копитель, блок местного управления, блок коммутации, блок коррекции, фор мирователь дополнительного сигнала ошибки и блок управления, причем выхо;Ф 1 блоков поканального контроля подключены соответственно ко входу формирователя сигнала ошибки, первым входам блока местного управления, блока коммутации, блока коррекции и формирователя дополнительного сигнала оощбки и первым входам блоков поканального контроля, выход формиро вателя сигнала ошибки соединен со вторыми входами блока местного управления и формирователя дополнительного сигнала ошибки, выход которого цодкгадчен. третье блока ного управления, первый и второй выходы которого и первый выход блока коммутации подключены к соответствую- щим входам буферного накопителя, выход которого (инeн со вторым входоц блока коммутации, выход которого подключен ко второму входу блока коррекции, третий вход соторого соеДинен с Выходом формирователя дополнительного сигнала ошибки, управляющие входы фop {иpoвaтeля сигнала ошибки, блоков поканального контроля, блока местного управления, формиро вателя дополнительного сигнала ошибки и блока коррекции подключены к выходам блока управления, о т л ич ia ю щ е е с я тем, что, с целью упрощения устройства и повьрения оперативности контроля, в нем третий и erisepTbtfi выходч блока г естного управления подключены соответственно к другому входу буферного накопителя и третьему входу блока коммутации, выход фОр1№ рователя дополнительного сигнала ошибки соединен со вторыми входами поканального онтроля, одни из выходов которад цодключены К третьему вяоду формирователя дополнительного сигнала ошибки. Источники информации, при1&тые во вннмание при экспертизе 1.Авторское свидетельство CCCJ 38П02, кл. Gn С 29/00, J971. 2.Авторское свидетельство СССР по заявке 2677455/18-24, кл. G 11 С 29/00, 1978 (прототиц),

Л л

4/

Л Л

V V V

W

и

T-TLn-J LJ L . . .

т

Л А

V

А Л

г

МРР ..W

Авторы

Даты

1981-09-23—Публикация

1979-08-15—Подача