Изобретение относится к приборостроению и может быть использовано в запоминающих устройствах на подвижном носителе, а также в устройствах передачи и приема цифровой информации.

Известен способ записи-воспроизведения многоканальной цифровой информации, в котором записывают основную и дублирующую информацию с контрольными разрядами по четности для каждой из строк, контролируют построчно воспроизведенную информацию и четность, заменяют при обнаружении ошибки дефектную строку на дублирующую строку [1].

Недостатком такого способа является невысокая достоверность, поскольку не выявляются дефектные строки с четным количеством ошибок в строке при воспроизведении, не исправляются дефекты, если они содержатся в одних и тех же строках основного и дублирующего массива информации.

Наиболее близким к предлагаемому является способ записи-воспроизведения многоканальной цифровой информации, в котором формируют при записи на носитель для каждой строки информации контрольный разряд путем суммирования по модулю 2 несовпадающих между собой информационных разрядов по одному в каждом канале в двух направлениях, формируют при воспроизведении признаки ошибок при отклонении от четности суммы информационных и контрольного разрядов, соответствующих суммируемым разрядам и формируемому контрольному разряду при записи, сравнивают между собой признаки ошибок, определяют дефектный канал по длительности интервала между совпавшими признаками одного и того же дефекта, инвертируют дефектные разряды, соответствующие признакам ошибок. Для исключения взаимного влияния дефектов в каналах корректируют разряды информации поканально последовательно, начиная с двух крайних каналов [2].

Недостатком такого способа является невысокая достоверность, вызванная возможностью размножения ошибок при неблагоприятном сочетании дефектов по строкам и каналам, а также отсутствием контроля качества записанной информации. Другим недостатком способа является его низкое быстродействие, связанное с поканально последовательной коррекцией информации.

Целью изобретения является повышение достоверности записи-воспроизведения многоканальной цифровой информации и повышение быстродействия при воспроизведении.

Поставленная цель достигается тем, что в способе записи-воспроизведения многоканальной цифровой информации, основанном на формировании при записи на носитель для каждой строки информации контрольного разряда в дополнительном канале путем суммирования по модулю 2 несовпадающих между собой информационных разрядов по одному в каждом канале в двух направлениях, формировании при воспроизведении признаков ошибок при отклонении от четности суммы информационных и контрольного разрядов, соответствующих суммируемым разрядам и формируемому контрольному разряду при записи, сравнении между собой признаков ошибок, определении дефектного канала по длительности интервала между совпавшими признаками одного и того же дефекта, инвертировании дефектных разрядов, соответствующих признакам ошибок, коммутируют при записи информационные и дополнительный каналы поочередно на все дорожки носителя, осуществляют при воспроизведении обратную коммутацию информации дорожек на информационные и дополнительный каналы, сравнивают признаки ошибок пакетами, инвертируют дефектные разряды при совпадении пакетов признаков ошибок, формируют сигнал дефектности при несовпадении признаков ошибок, а при контроле качества записанной информации сравнивают поразрядно воспроизведенную нескорректированную информацию с запомненной исходной информацией при записи.

Совокупность вновь введенных операций не обнаружена ни в одном из известных источников информации и не следует из уровня техники. Следовательно, предложенное техническое решение соответствует изобретательскому уровню.

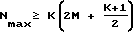

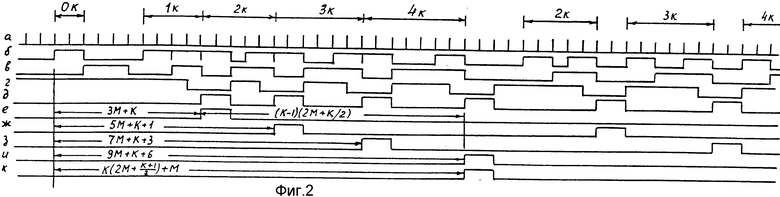

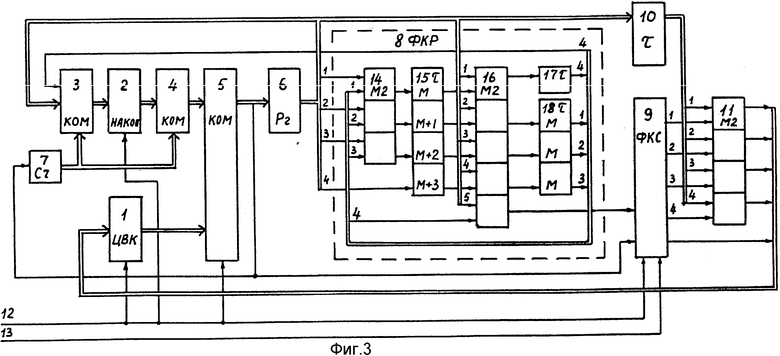

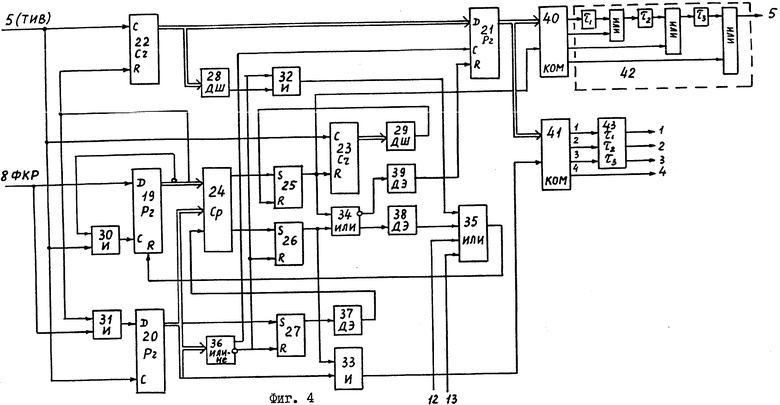

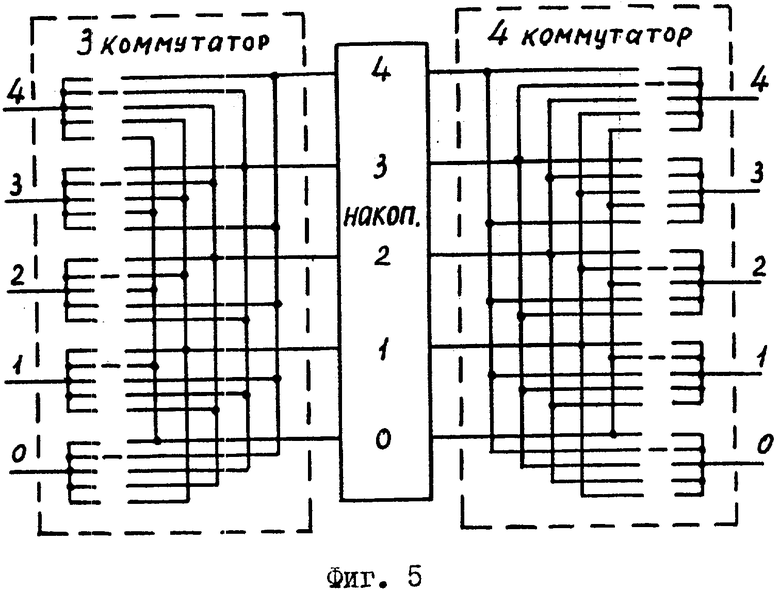

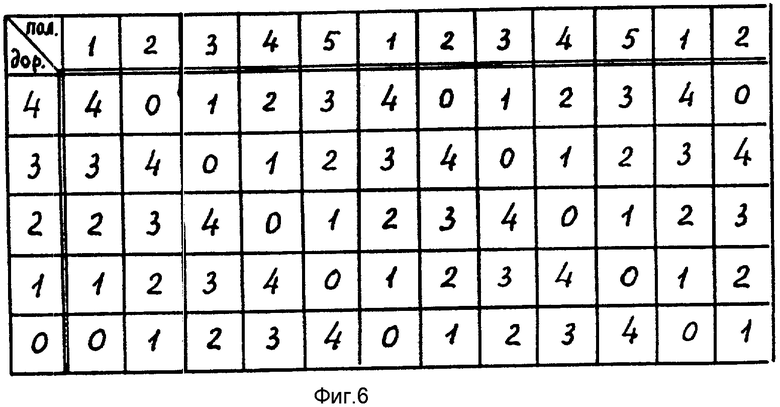

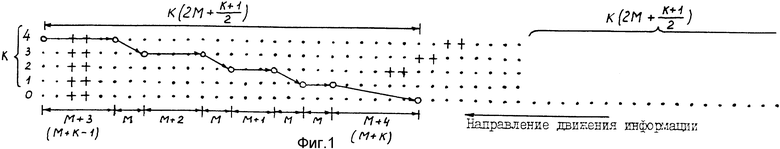

На фиг. 1 представлен пример формирования контрольных разрядов векторного кода при записи четырехканальной информации на носитель; на фиг. 2 - пример формирования корректирующих сигналов при воспроизведении; на фиг. 3 - структурная схема устройства кодирования и коррекции информации; на фиг. 4 - структурная схема формирователя корректирующих сигналов (ФСК); на фиг. 5 - коммутаторы для перемещения информации на входе и выходе накопителя; на фиг. 6 - таблица размещения информации каналов на дорожках носителя при различных положениях коммутаторов для перемежения.

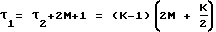

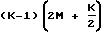

На фиг. 1 информация размещена в K = 4 информационных каналах накопителя. Пятый канал предназначен для размещения контрольных разрядов векторного кода. Максимальная длина массива исправляемых ошибок равна M строк. Стрелками обозначено направление суммирования информационных разрядов при формировании контрольного разряда при записи информации. После окончания массива информации в контрольном канале продолжается формирование контрольных разрядов в течение

тактов.

Устройство на фиг. 3 содержит цифровой вычислительный комплекс (ЦВК) 1, накопитель 2, коммутаторы 3, 4 и 5, регистр 6, счетчик 7, формирователь 8 контрольных разрядов (ФКР), формирователь 9 корректирующих сигналов, блок 10 элементов задержки, блок 11 сумматоров по модулю 2, шину 12 управления записью-воспроизведением и шину 13 управления воспроизведением без коррекции.

Формирователь 8 контрольных разрядов содержит блок 14 сумматоров по модулю 2, блок 15 из K = 4 элементов задержки, блок 16 сумматоров по модулю 2, элемент 17 задержки и блок 18 из K-1 элементов задержки. Длительность задержки первого из элементов блока 15 равна M тактов (разрядов), а в каждом из последующих элементов увеличивается на один разряд по сравнению с предыдущим элементом, достигая в последнем элементе этого блока величины M + K - 1 разрядов. Длительность задержки в элементе 17 составляет M + K разрядов, а длительность задержки в каждом из элементов блока 18 составляет M разрядов. Блок 14 содержит K-1, а блок 16 содержит K + 1 двухвходовых сумматоров по модулю 2.

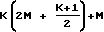

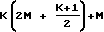

Формирователь 9 корректирующих сигналов на фиг. 4 содержит регистры 19 - 21, счетчики 22 - 23 импульсов, блок 24 сравнения, триггеры 25 - 27, дешифраторы 28, 29, элементы И 30 - 33, элементы ИЛИ 34, 35, элемент ИЛИ-НЕ 36, элементы 37-39 дифференцирования, коммутаторы 40, 41, блоки 42, 43 задержки. Величина задержек в блоке 42 равна τ1 = 2M + 1 разрядов, τ2 = 2M + 2 разрядов, . .., τk-1 = 2M + K - 1 разрядов, при этом вход задержки τ1 блока 42 подключен к входу коммутатора 40, соответствующему информации первого информационного канала, ближнего к контрольному. Выход коммутатора 40, соответствующий последнему K информационному каналу, подключен без задержки через последний элемент ИЛИ к выходу блока 42, который является (K + 1) - м выходом формирователя 9. Аналогично выход коммутатора 41, соответствующий K информационному каналу, является K-выходом формирователя 9. Величина задержки в блоке 43 для выходной информации K-1 канала коммутатора 42 составляет τk-1 = 2M + K - 1 разрядов, для (K-2) - канала τk-2= τk-1 + 2M +K - 2 разрядов и т.д. Величина задержки в блоке 43 для выходной информации первого канала коммутатора 41 составляет ,

,

разрядов и равна суммарной задержке в блоке 42 для информации первого канала.

Устройство работает в режиме записи информации из ЦВК 1 в накопитель 2 с формированием контрольных разрядов векторного кода путем суммирования по модулю 2 информационных разрядов в двух диагональных направлениях; в режиме воспроизведения информации из накопителя 2 с коррекцией одиночных и пакетов ошибок длины M одновременно в нескольких каналах с обозначением дефектной неисправляемой информации; в режиме контрольного воспроизведения записанной информации из накопителя 2 вместе с разрядами векторного кода без коррекции. Управление режимами работы осуществляется по шинам 12 и 13.

В режиме записи информация по K каналам построчно поступает с выходов ЦВК 1 (фиг. 3) через коммутатор 5 в регистр 6. На фиг. 1 информация следует в направлении справа налево. В блоке 16 информация принятой строки с выхода регистра 6 поразрядно суммируется с выходной информацией блока 15 элементов задержки, разряды которой задержаны по отношению к принятой строке на различное количество от M до M + K - 1 тактов (разрядов) в зависимости от номера канала. В блоке 14 выходная информация регистра 6 поразрядно суммируется по модулю 2 с выходной информацией блока 18 элементов задержки, все разряды которой смещены на входе блока 14 на один канал по отношению к выходной информации регистра 6. Все элементы блока 18 имеют задержку на M тактов (разрядов). На выходе блока 16, подключенном к элементу 17 задержки, формируется контрольный разряд векторного кода, который с выхода элемента 17 вместе с информационными разрядами принятой строки с выходов регистра 6 поступают через коммутатор 3 на вход записи накопителя 2. По окончанию массива информации, подлежащего записи, в накопитель 2 в течение

тактов продолжается запись контрольных разрядов векторного кода (фиг. 1). Счетчик 7 производит подсчет количества записываемых строк с коэффициентом пересчета (1 + K) M. После каждых M записанных в накопитель 2 строк информации коммутатор 3 переключается на одну позицию (фиг. 5) и запись информации каналов смещается на одну дорожку накопителя 2. В результате на каждой дорожке накопителя 2 поочередно записывается информация всех каналов, как представлено в таблице на фиг. 6. Остальные блоки устройства в режиме записи не участвуют.

В режиме воспроизведения информации вместе с контрольными разрядами векторного кода построчно поступает с выходов накопителя 2 через коммутаторы 4 и 5 в регистр 6. Каждая строка информации сопровождается тактовым импульсом воспроизведения ТИВ (фиг. 2а). Счетчик 7 производит по ТИВ подсчет количества воспроизведенных строк с тем же M (K + 1) коэффициентом пересчета. Коммутатор 4 работает аналогично коммутатору 3. В результате выходная информация накопителя 2 поканально восстанавливается и контрольные разряды поступают в регистр 6 по контрольному каналу и далее следуют на первый вход одного сумматора блока 16. На выходе элемента 17 формирователя 8 в режиме воспроизведения так же, как и в режиме записи, формируются значения контрольного разряда векторного кода путем суммирования по модулю 2 информационных разрядов в двух диагональных направлениях согласно фиг. 1. Сформированные значения контрольного разряда поступают на второй вход одного сумматора блока 16, где после суммирования с воспроизведенным тем же контрольным разрядом формируется признак ошибки.

При отсутствии ошибок в информационных и контрольном разрядах с выхода одного сумматора блока 16 на информационный вход регистра 19 поступают нулевые сигналы, что приводит к нулевым сигналам в регистрах 19 - 21 и на выходах коммутаторов 42 - 43 формирователя 9. Выходная информация регистра 6 задерживается в блоке 10 на величину.

разрядов и без изменения в блоке 11 поступает в ЦВК 1.

При наличии ошибок в массиве воспроизведенной информации (на фиг. 1 обозначены крестами на информации) на выходе формирователя 8, подключенном к входу регистра 19 в формирователе 9, формируются по фронтам ТИВ единичные признаки ошибок (фиг. 2б), образующиеся при суммировании ошибочного бита сначала в одном, а потом в другом диагональных направлениях. Каждому ошибочному информационному биту соответствуют два признака ошибок, расстояние в тактах между которыми равно M - 1 + Ki (где Ki - номер дефектного информационного канала). Выходная информация формирователя 8 последовательным кодом записывается в M - разрядный регистр 19. При заполнении регистра 19 M - разрядным пакетом ошибок его старший разряд устанавливается в 1 (фиг. 2в), элемент И 30 закрывается и запись информации в регистр 19 прекращается. Одновременно снимается запрет с R - входа счетчика 22 и он начинает счет ТИВ, срабатывая по их срезам. Открывается элемент И 31 для приема в регистр 20 второго пакета признаков ошибок. По первому единичному сигналу этого пакета, записанному в регистр 20, на выходе элемента ИЛИ-НЕ 36 формируется нулевой сигнал (фиг. 2г) и срезом этого сигнала информация счетчика 22 записывается в регистр 21. Выходная информация формирователя 8, соответствующая второму пакету признаков ошибок, записывается последовательным кодом в регистр 20. После записи M разрядов единичный сигнал с выхода M - разряда регистра 20 устанавливает в 1 триггер 27 (фиг. 2д) и фронтом его выходного сигнала, сформированного элементом 37, опрашивается блок 24 сравнения. При равенстве пакетов признаков ошибок с выходов регистров 19 и 20 выходной сигнал блока 24 устанавливает в 1 триггер 26 (фиг. 2д). По фронту сигнала триггера 26 элементом 38 формируется импульс, устанавливающий в 0 регистр 19 (фиг. 2в). Счетчик 22 обнуляется, элемент И 31 закрывается, прекращая запись информации в регистр 20, и открывается элемент И 30 для приема следующего пакета ошибок в регистр 19. Единичный сигнал триггера 26 открывает элемент И 33, и пакет признаков ошибок (корректирующих сигналов) с выхода M - разряда регистра 20 поступает на один, соответствующий дефектному каналу, выход коммутатора 41. Номер дефектного канала определяется кодом регистра 21. Временное положение пакета корректирующих сигналов на выходах коммутатора 41 по отношению к дефектным строкам определяется номером дефектного канала. Так, для первого информационного канала пакет корректирующих сигналов на выходах коммутатора 41 задержан по отношению к дефектным строкам на 3M + K тактов. С учетом задержки в блоке 43 для первого канала на величину

общая задержка на выходе формирователя 9 для корректирующих сигналов первого канала составит

тактов. Для второго информационного канала задержка пакета корректирующих сигналов составит 5M + K + 1 тактов, а общая задержка на выходе формирователя 9 с учетом задержки в блоке 41 (на 2M + 1 тактов меньше задержки для информации первого канала) будет равна общей задержке информации первого канала. Так будет и для всех остальных каналов. В результате задержка корректирующих сигналов на выходе формирователя 9 для всех каналов будет равна задержке информации в блоке 10. В блоке 11 сумматоров по модулю 2 производится инвертирование ошибочных разрядов дефектной строке одновременно во всех каналах. Скорректированная истрока информации записывается в ЦВК 1.

Коррекция каждого пакета ошибок продолжается до тех пор, пока в регистре 20 содержатся единичные признаки ошибок. При нулевом значении кода регистра 20 на выходе элемента ИЛИ-НЕ 36 формируется единичный сигнал (фиг. 2г), устанавливающий в 0 триггеры 26 и 27. По срезу выходного сигнала триггера 26 элемент 39 вырабатывает сигнал сброса в 0 регистра 21. При наличии очередного пакета признаков ошибок в регистре 19 процесс коррекции повторяется. Корректирующие сигналы на выходах коммутатора 41 для ошибок, помеченных крестами на фиг. 1, представлены на фиг. 2 е, ж, з, и. Корректирующие сигналы на выходах формирователя 9 для дефектных строк тех же ошибок (для всех каналов одновременно) представлены на фиг. 2к. При наличии корректируемых ошибок на выходах триггера 25, коммутатора 40 и блока 42 формируются нулевые сигналы.

При наличии ошибок воспроизведения в контрольном канале (фиг. 2б) формируется только один пакет признаков ошибок, который записывается в регистр 19, и по единичному сигналу с выхода его старшего разряда начинает работу счетчик 22. При коде K счетчика 22 срабатывает дешифратор 28, выходной сигнал которого через открытый элемент И 32 и элемент ИЛИ 35 сбрасывает регистр 19 (фиг. 2в). Коррекция информации в контрольном канале не производится, наличие ошибки в контрольном канале нигде не обозначается.

При несовпадении пакетов признаков ошибок в регистрах 19 и 20 по сигналу элемента 37 блок 24 сравнения вырабатывает сигнал, устанавливающий в 1 триггер 25. В зависимости от кода регистра 21, обозначающего номер дефектного канала, выходной сигнал триггера 25 через коммутатор 40 поступает на соответствующий выход блока 42, где задерживается на число тактов в соответствии с номером дефектного канала. На выходе блока 42 формируется единичный сигнал, совпадающий по времени с появлением с выходов блока 10 дефектных строк, признаки ошибок которых находятся в регистрах 19 и 20. Триггер 26 находится в нулевом состоянии, элемент И 33 закрыт, на выходах коммутатора 41 и блока 43 - нулевые сигналы. Коррекция дефектной строки не производится. Дефектная строка вместе с единичным сигналом ее дефектности записывается в ЦВК 1. При единичном состоянии триггера 25 снимается блокировка с R - входа счетчика 23 и он начинает подсчет ТИВ. При коде M счетчика 23 срабатывает дешифратор 29 и устанавливает в 0 триггер 25. По срезу сигнала триггера 25 элемент 38 вырабатывает импульс сброса регистра 19. устройство готово к приему информации о следующем пакете признаков ошибок.

При контроле качества записанной в накопитель 2 информации устройство работает в режиме воспроизведения информации, однако ее коррекция не производится. По сигналу "Воспроизведение без коррекции" по шине 13 регистр 19 устанавливается в 0. Триггеры 25 - 27, счетчики 22 - 23, регистр 20 находятся в нулевом состоянии. На выходах коммутаторов 40, 41 и блоков 42 - 43 формируются нулевые сигналы. Выходная информация накопителя 2 вместе с разрядами векторного кода через коммутаторы 4 и 5 поступает в регистр 6 и после задержки в блоке 10 проходит без изменения в ЦВК 1, где сравнивается с расчетной информацией.

Разработанный способ без коммутации каналов (коммутаторы 3 и 4) позволяет исключить одиночные ошибки или пакеты ошибок в M разрядов по одному из каналов, если бездефектный промежуток не менее M разрядов для первого канала (ближнего к контрольному), M + 1 разрядов для второго канала, M + 2 разрядов для третьего канала и т.д. Для последнего K канала бездефектный промежуток не может быть менее M + K - 1 разрядов. В способе исключаются массивы ошибок в M строк одновременно по всем каналам при бездефектном промежутке между дефектными массивами

строк. Если в предыдущем дефектном массиве отсутствуют ошибки в последних K, K-1, ... каналах, то бездефектный промежуток до следующего пакета или массива уменьшается до величины

строк, где n - номер последнего дефектного канала.

Введение коммутации каналов на все дорожки носителя и обратной коммутации (коммутаторы 3 и 4) позволяет значительно увеличить длину исправляемых пакетов ошибок в одном из каналов. Основным условием исправляемости пакета ошибок при этом является наличие только одного пересечения обобщенного вектора суммирования информационных разрядов при формировании контрольного разряда с развернутым по каналам с помощью коммутаторов 3 и 4 пакетом ошибок. Минимальная длина исправляемых пакетов зависит от значений M и K.

Достоинством разработанного способа является возможность исправления одиночных и пакетов ошибок значительной длины в одном из каналов, исправления ограниченного по длине массива ошибок одновременно по всем каналам при отсутствии эффекта размножения ошибок при коррекции, характерного для сверточных кодов. Для этого необходимо выбрать достаточную длину M сравниваемых пакетов признаков ошибок. В способе обозначаются неисправляемые пакеты ошибок, что позволяет его использовать совместно с другим способом коррекции, в частности, заменять дефектную неисправленную часть информации на бездефектную часть того же содержания из дублирующего массива по наличию сигнала дефектности.

В зависимости от особенностей практического использования и характера возможных дефектов в носителе 2 из устройства, реализующего способ, могут быть исключены отдельные блоки. Например, если используется только один векторный метод коррекции без замены неисправленной дефектной части, то в блоке (формирователе) 9 могут быть исключены элементы (40 и 42). Если в накопителе 2 маловероятны пакеты ошибок значительной длины, то можно исключить коммутаторы 3 и 4.

Источники информации.

1. Авторское свидетельство СССР N 1001166, кл. G 11 B 5/02, 1981.

2. Авторское свидетельство СССР N 1190409, кл. G 11 B 20/10, 1984 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для записи и воспроизведения цифровой информации | 1990 |

|

SU1742856A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| МНОГОУРОВНЕВЫЙ АНАЛИЗАТОР-РЕГИСТРАТОР НАПРЯЖЕНИЯ ИСТОЧНИКА ПОСТОЯННОГО ТОКА | 1991 |

|

RU2046357C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| НАКОПИТЕЛЬ ЦИФРОВОЙ ИНФОРМАЦИИ | 2002 |

|

RU2236710C2 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 1993 |

|

RU2107390C1 |

| УСТРОЙСТВО ЗАПИСИ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840746A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

Изобретение относится к приборостроению и может быть использовано в запоминающих устройствах на подвижном носителе, а также в устройствах передачи и приема цифровой информации. Способ записи-воспроизведения многоканальной информации основан на формировании при записи на носитель для каждой строки информации контрольного разряда в дополнительном канале путем суммирования по модулю 2 несовпадающих между собой информационных разрядов по одному в каждом канале в двух направлениях, формировании при воспроизведении признаков ошибок при отклонении от четности суммы информационных и контрольного разрядов, соответствующих суммируемым разрядам и формируемому контрольному разряду при записи, сравнении между собой признаков ошибок, определении дефектного канала по длительности интервала между совпавшими признаками одного и того же дефекта, инвертировании дефектных разрядов, соответствующих признакам ошибок. Особенность способа заключается в том, что коммутируют при записи информационные и дополнительный каналы на все дорожки носителя поочередно, осуществляют при воспроизведении обратную коммутацию информации дорожек на информационные и дополнительный каналы, сравнивают признаки ошибок пакетами, инвертируют сигнал дефектности при несовпадении пакетов, а при контроле качества записанной информации сравнивают поразрядно воспроизведенную информацию с исходной информацией при записи. 6 ил.

Способ записи-воспроизведения многоканальной цифровой информации, основанный на формировании при записи на носитель для каждой строки информации контрольного разряда в дополнительном канале путем суммирования по модулю 2 несовпадающих между собой информационных разрядов по одному в каждом канале в двух направлениях, формировании при воспроизведении признаков ошибок при отклонении от четности суммы информационных и контрольного разрядов, соответствующих суммируемым разрядам и формируемому контрольному разряду при записи, сравнении между собой признаков ошибок, определении дефектного канала по длительности интервала между совпавшими признаками одного и того же дефекта, инвертировании дефектных разрядов, соответствующих признакам ошибок, отличающийся тем, что коммутируют при записи информационные и дополнительный каналы на все дорожки носителя поочередно, осуществляют при воспроизведении обратную коммутацию информации дорожек на информационные и дополнительный каналы, сравнивают признакуи ошибок пакетами, иныертируют дефектные разряды при совпадении пакетов признаков ошибок, формируют сигнал дефектности при несовпадении пакетов признаков ошибок, а при контроле качества записанной информации сравнивают поразрядно воспроизведенную некорректированную информацию с запомненной исходной информацией при записи.

| SU, авторское свидетельство, N 1190409, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1998-03-20—Публикация

1995-12-18—Подача