(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОВС?^СОЮЗНАЯR'f"-<-;;?t -':n''fi'^vv/"tJli .4 i \М i bd -11.Л«Я sir«lt«flЕЧБЛИОТЕНА | 1972 |

|

SU333605A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1144153A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Запоминающее устройство | 1976 |

|

SU631994A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

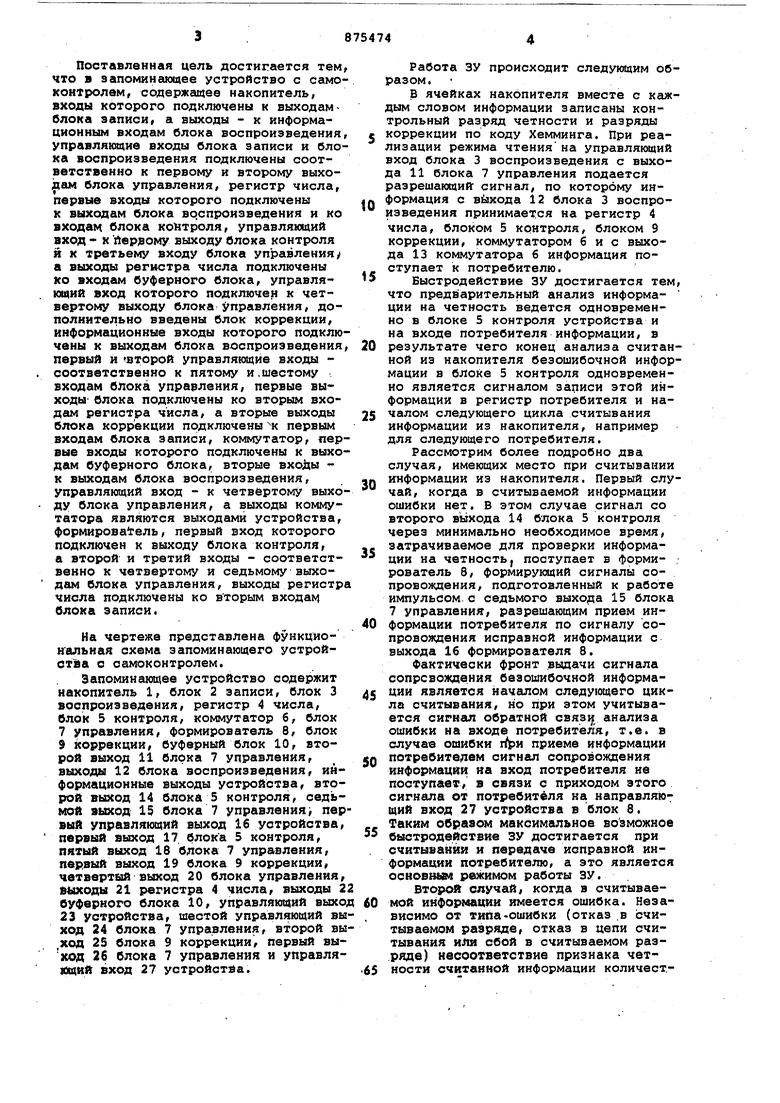

Изобретение отнбсится к вычислительной технике, в частности к запоминающим устройствам (ЗУ) и может быть использовано при передаче цифро вой информации. Известно устройство для обнаружения и локализации одиночных ошибок при передаче цифровой информации, в которую с целью исправления ошибок информации вводится избыточность путем увеличения разрядности хранимых слов (код Хемминга)13. Однако такое устройство ограничивает быстродействие ЗУ в режиме считывания в виду прохождения каждого слова информации из накопителя к потребителю через устройство коррекций по кодам Хемминга, независимо от при сутствия или отсутствия ошибки в сло ве информации. Наиболее близким к предлагаемому: по технической сущности является з.апоминающее устройство с Сс1моконтролем, содержащееоперативный накопитель, подключенный через блок воспроизведения к регистру числа/ блок контроля достоверности информации, соединенный с блоком управления L2J . Недостатком известного устройства ;является ограничение быстродействия ЗУ в режиме считывания информации и передачи в другие устройства-потребители. Это объясняется тем, что с применением современных быстродействующих схем накопителей с циклом чтения порядка десятков наносекунд время, необходимое для обнаружения ошибки в Ксокдом считанном слове и организация сигналов вьвдачи (или блокировки в случае обнаружения ошибки) после анализа информации к потребителям, становится соизмеримым с циклом считывания со схем накопителя, при этом имеется в виду, что считываемая . информация из памяти, в основном, является безошибочной. Кроме того, в современных .вычислительных устройствах потребители ин формации (процессор, канал, регистры и т.д.) перед использованием ее, тратят дополнительное время на контроль, в частности по модулю два. Быстродействие,ЗУ должно определяться не только собственной скоростью цикла работы ЗУ, но и его взаимодействием с потребителями по передаче счи-, танной информации. Цель изобретения - повышение быстродействия запоминающего устройства с самоконтролем. Поставленная цель достигается тем что в запоминающее устройство с само контролем, содержащее накопитель, входы которого подключены к выходамблока записи, а выходы - к информационным входам блока воспроизведения управляющие входы блока записи и бло ка воспроизведения подключены соответственно к первому и второму выхо|1ам блока управления, регистр числа, первые входы которого подключены к выходам блока воспроизведения и ко входам блока контроля, управляющий вход к первому выходу блока контроля и к третьему входу блока управленияу а выходы регистра числа подключены ко входам буферного блока, управлякедий вход которого подключен к четвертому выходу блока Управления, дополнительно введены блок коррекции, информационные входы которого подклю чены к выходам блока воспроизведения первый и «второй управляющие входы соответственно к пятому и,шестому входам блока управления, первые выходы блока подключены ко вторым входем регистра числа, а вторые выходы блока коррекции подключены к первым входам блока записи, коммутатор, пер вые входы которого подключены к выхо дам буферного блока, вторые вхоДы к выходам блока воспроизведения, управляющий вход - к четвертому выхо ду блока управления, а выходы коммутатора явл;1ются выходами устройства, формирователь, первый вход которого подключен к выходу блока контроля, а второй и третий входы - соответственно к четвертому и седьмому выходам блока управления, выходы регистр числа подключены ко вторым входам блока записи. Иа чертеже представлена функциональная схема запоминающего устройCTla с самоконтролем. Запоминающее устройство содержит накопитель 1, блок 2 записи, блок 3 воспроизведения, регистр 4 числа, блок 5 контроля, коммутатор 6, блок 7 управления, формирователь В, блок 9 коррекции, буферный блок 10, второй выход 11 блока 7 управления, выходы 12 блока воспроизведения, информационные выходы устройства, второй выход 14 блока 5 контроля, седьмой выход 15 блока 7 управления; пер вый управляющий выход 16 устройства, первый выход 17 блока 5 контроля, пятый выход 18 блока 7 управления, первый выход 19 блока 9 коррекции, четвертый выход 20 блока управления выходы 21 регистра 4 числа, выходы 2 буферного блока 10, управляющий выхо 23 устройства, шестой управляющий вы ход 24 блока 7 управления, второй вы ход 25 блока 9 коррекции, первый выход 26 блока 7 управления и управля1йщий вход 27 устройства. Работа ЗУ происходит следующим образом. В ячейках накопителя вместе с кажым словом информации записаны контрольный разряд четности и разряды коррекции по коду Хемминга. При реализации режима чтения на управляющий вход блока 3 воспроизведения с выхоа 11 блока 7 управления подается разрешающий сигнал, по которому информация с выхода 12 блока 3 воспроизведения принимается на регистр 4 числа, блоком 5 контроля, блоком 9 коррекции, коммутатором бис выхода 13 коммутатора 6 информация поступает к потребителю. Быстродействие ЗУ достигается тем, что предварительный анализ информа- ° ции на четность ведется одновременно в блоке 5 контроля устройства и на входе потребителя информации, в результате чего конец анализа считанной из накопителя безошибочной информации в блоке 5 контроля одновременно является сигналом записи этой информации в регистр потребителя и началом следующего цикла считывания информации из накопителя, например для следующего потребителя. Рассмотрим более подробно два случая, имеющих место при считывании информации из накопителя. Первый случай, когда в считываемой информации ошибки нет. В этом случае сигнал со второго выхода 14 блока 5 контроля через минимально необходимое время, затрачиваемое для проверки информации на четность, поступает в форми- , рователь 8, формирующий сигналы сопровождения, подготовленный к работе импульсом, с седьмого выхода 15 блока 7 управления, разрешающим прием информации потребителя по сигналу сопровождения исправной информации с выхода 16 формирователя 8. Фактически фронт выдачи сигнала сопровождения безошибочной информации является началом следующего цикла считывания, но при этом учитывается сигнал обратной csnsif анализа ошибки на входе потребителя, т.е. в случае ошибки rtp приеме информации потребителем сигнал сопровохшения информации на вход потребителя не поступает, в связи с приходом этого сигнала от потребителя на направляющий вход 27 устройства в блок 8. Таким образом максимальное возможное быстродействие ЗУ достигается при считывании и передаче исправной информации потребителю, а это является основным режимом работы ЗУ. второй случай, когда в считываемой информации имеется ошибка. Независимо от типа-ошибки (отказ .в считываемом разряде, отказ в цепи считывания или сбой в считываемом разряде) несоответствие признака четности считанной информации количеству единиц в числе будет зафиксировано блоком 5 контроля (и соответствен но на входе потр(ебителя), и сигнал ошибки на выходе 17 блока 5 контроля будет передан в устройство 7 управления, на регистр числа 4, при этом по выходу 14 блока 5 контроля проиэойдет блокировка выдачи сигнала сопровождения исправной информации формирователем по выходу 16. Блок 7 управления сигналом на выходе 18 включает блок 9 коррекции 2 и в нем происходит анализ ошибки. По окончании анализа по выходу 19 блока 9 коррекции в регистре 4 числа произ ведётся коррекция сбойного разряда с одновременной выработкой числа четно ти скорректированного слова. По выходу 20 блока 7 управления происходит запись скорректированной информа ции с выхода 21 регистра 4 числа на буферный блок 10 с одновременным переключением коммутатора 6 на прием по выходу 22 буферного блока 10 и йередачей потребителю по выходу 13 коммутатора б, а также подготовка Формирователем 8 по выходу 20 блока 7 управления сигнала сопровождения скорректированной информации по входу 23. Через минимальное время анализа исправленной информации на входе потребителя по четности, т.е. по снятию сигнала ошибки, на входе потребителя, формирователь 8 по входу 23 организует сигнал сопровождения исправленной информации для записи ее в регистр потребителя. По окончании передачи скорректированной информации.потребителю, устройство 7 управления организует цикл записи скорректированной инфор мации в ячейку накопителя по тому же адресу, для исправления информации в ячейке накопителя. С выхода 24 блока 7 управления сигнал запускает в блоке 9 коррекции формирователи контрольных разрядов коррекции по коду Хемминга, а также разрядо1з четности, после чего скорректированная информация с выходов 21 регистра 4 числа с контрольными разрядами коррекции и четности, с выхода 25 блока 9 коррекции поступает на вход блока 2 записи. По сигналу с выхода 26 блока управления 7 информация записывается в накопитель Таким образом, сбой разряда информации в ячейке накопителя устраняется а в случае отказа не устраняется, при этом информация корректируется для передачи потребителю при каждом цикле считывания отказавшей ячейки накопителя.. -Предлагаемое изобретение позволяет повысить быстродейст вие ЗУ при считывании безошибочной информации, а это основной режим работы ЗУ, за счет уменьшения времени передачи информации на величину задержек в регистре числа, времени выработкиблоком управления разрешающего сигнала для блока вьщачи кодов и времени срабатывания блока выдачи кодов, так как в данном устройстве информация поступает одновременно как блоку , контроля достоверности информации, подготавливая к включению блок сопровождения сигнала информации, так и через коммутатор на вход потреби1теля. После одинакового и практически одновременного анализа информация на ее четность выработанным сигналом сопровождения производится ее запись на вход потребителя. Кроме того, изобретение позволяет исправлять ошибки при считывании, возникающие при случайных сбоях в ячейках накопителя. Формула изобретения Запоминающее устройство с сомоконтролем, содержащее накопитель, входы которого подключены к выходам блока записи, а выходы - к информационным входам блока воспроизведения, управляющие входы блока записи-и блока воспроизведения подключены соответственно к первому и второму выходам блока управления, регистр числа, первые входы которого подключены к выxoдгuv блока воспроизведения и ко входам блока контроля, управляющий вход к первому выходу блока контроля и к третьему входу блока управления, а выходы регистра числа подключены ко входам буферного блока, управляющий вход которого подключен к четвертому выходу блока управления, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок коррекции, информационные входы которого подключены к выходам блока воспроизведения, первый и второй управляющие входы - соответстве/1но к пятому и шестому входам блока управления, первые выходы блока коррекции подключены ко вторым входам регистра числа, а вторые выходы блока коррекции подключены к первым входам блока записи, коммутатор, первые входы которого подключены к выходам буферного блока, вторыэ входы - к выходам блока воспроизведения, управляющий вход - к четвертому выходу блока управления, а выходы коммутатора являются выходами устройства/ формирователь, первый вход которого подключен к выходу блока контроля, а второй и третий входы - соответственно к четвертому и седьмому выходгил блока управления, а выходы регистре

числа подключены ко вторым входам блока записи.

I

Источники информации, п инятыё во внимание экспертизе

свидетельство СССР 333605, кл.С 11 С 29/00, 1970 (прототип).

Авторы

Даты

1981-10-23—Публикация

1980-02-28—Подача