Изобретение относится к вычислительной технике и может найти применение при построении оперативных запоминающих устройств (ОЗУ).

Цель изобретения - повышение надежности устройства.

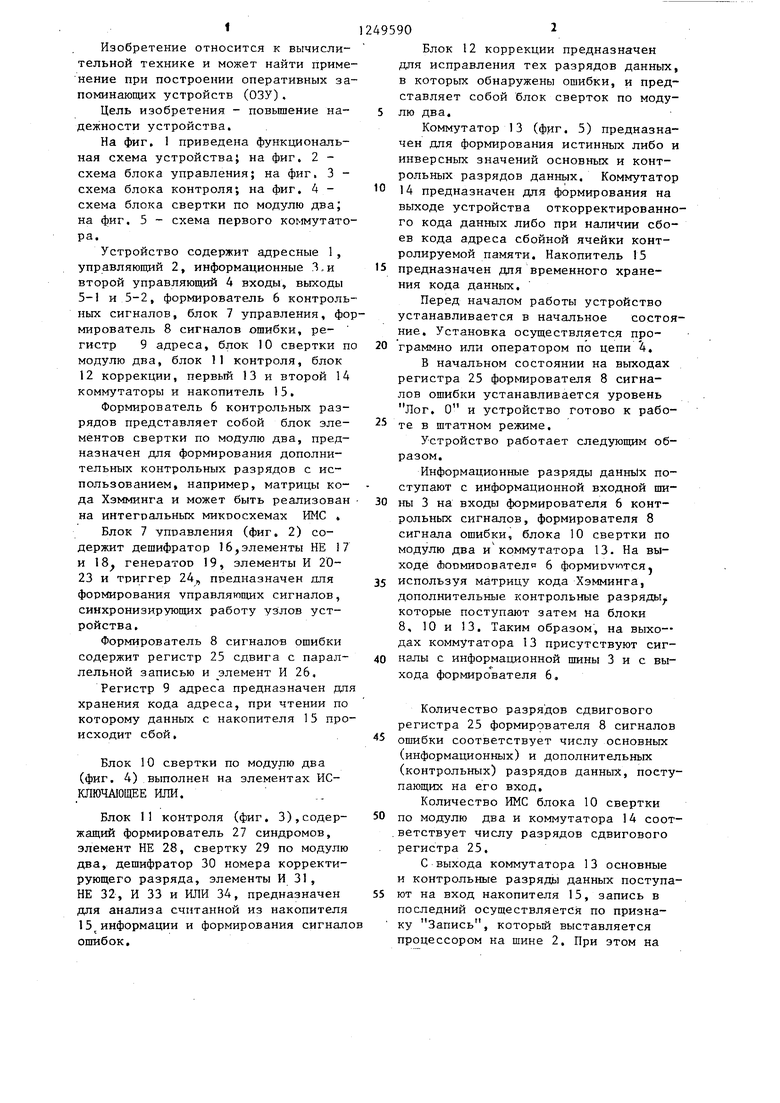

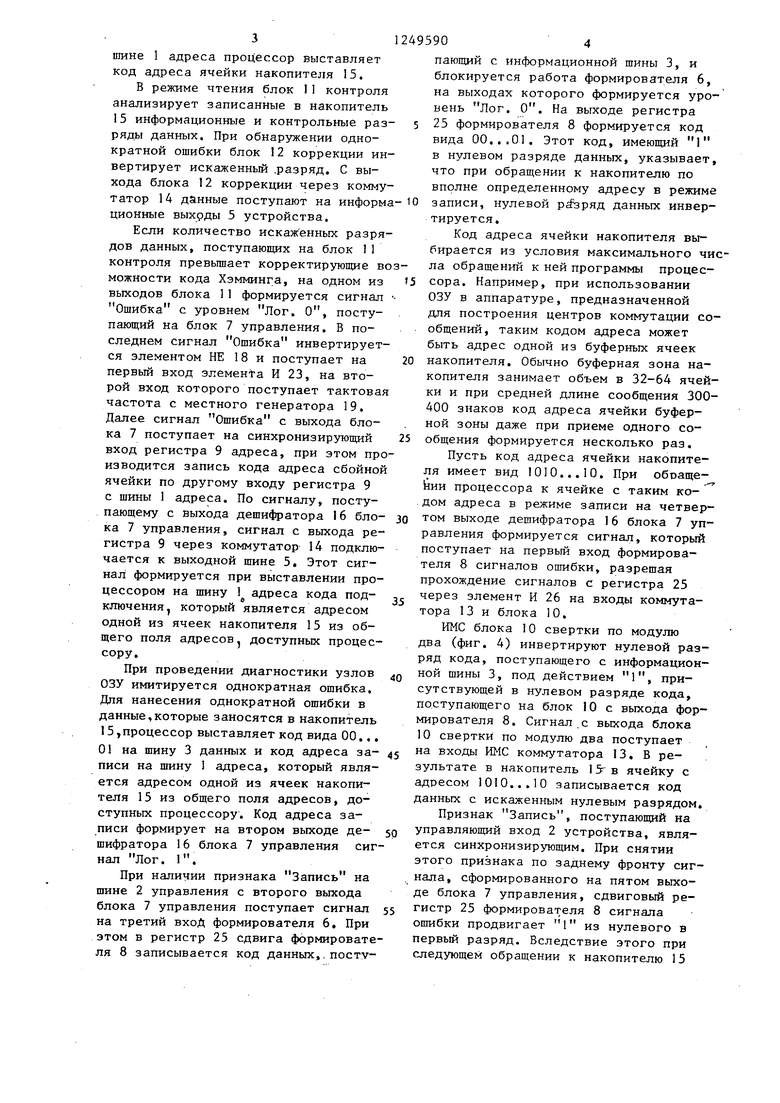

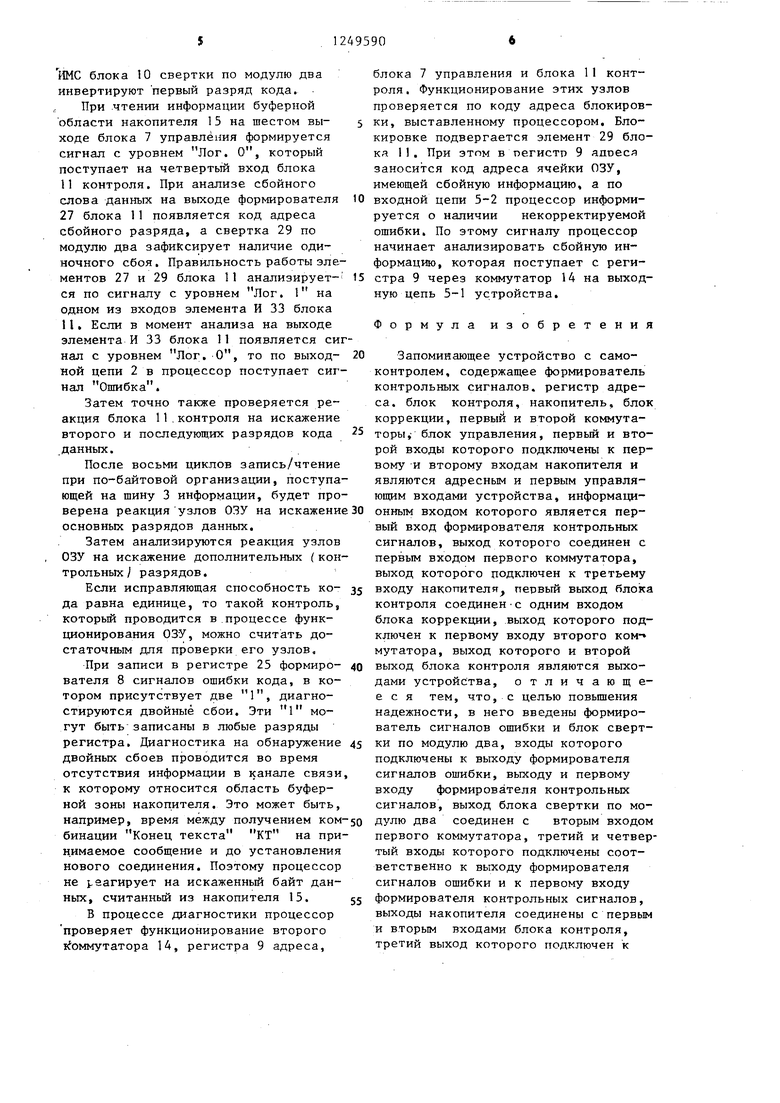

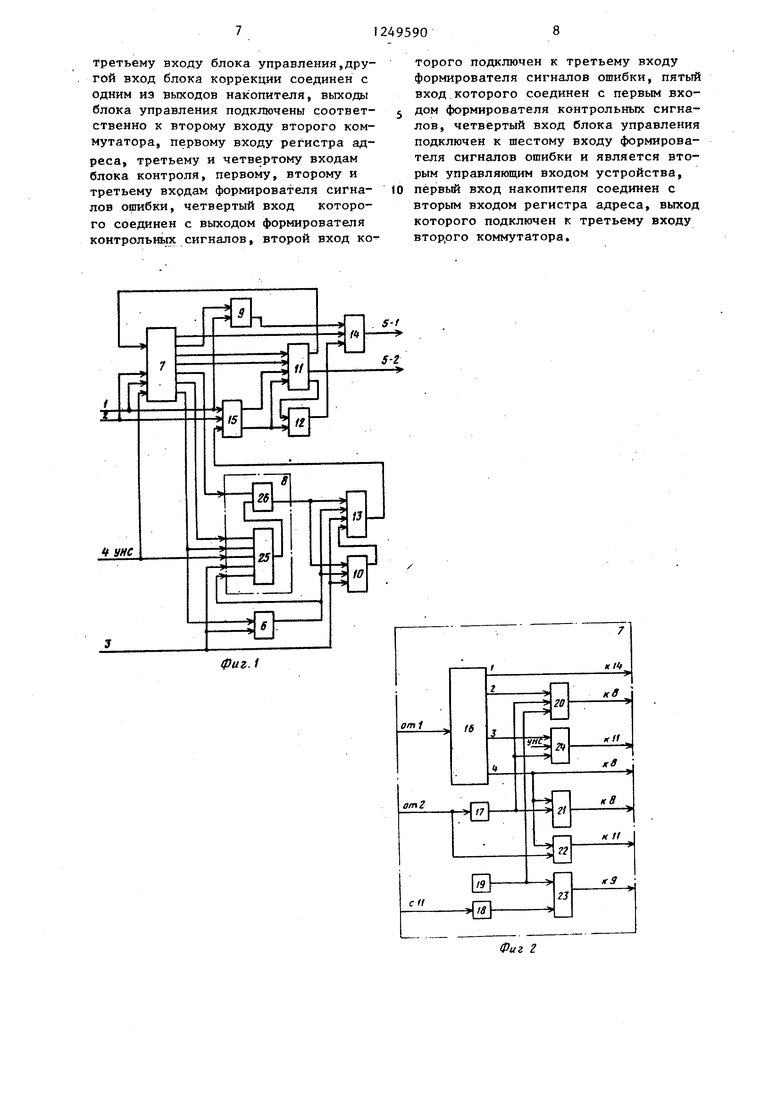

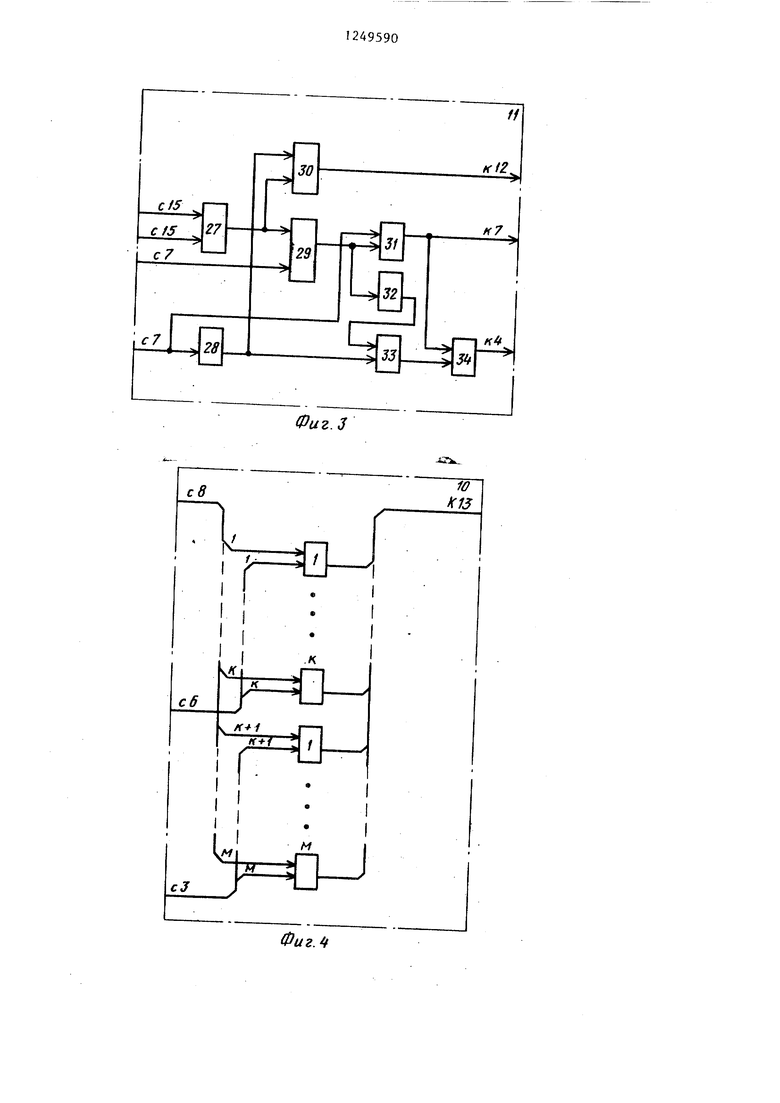

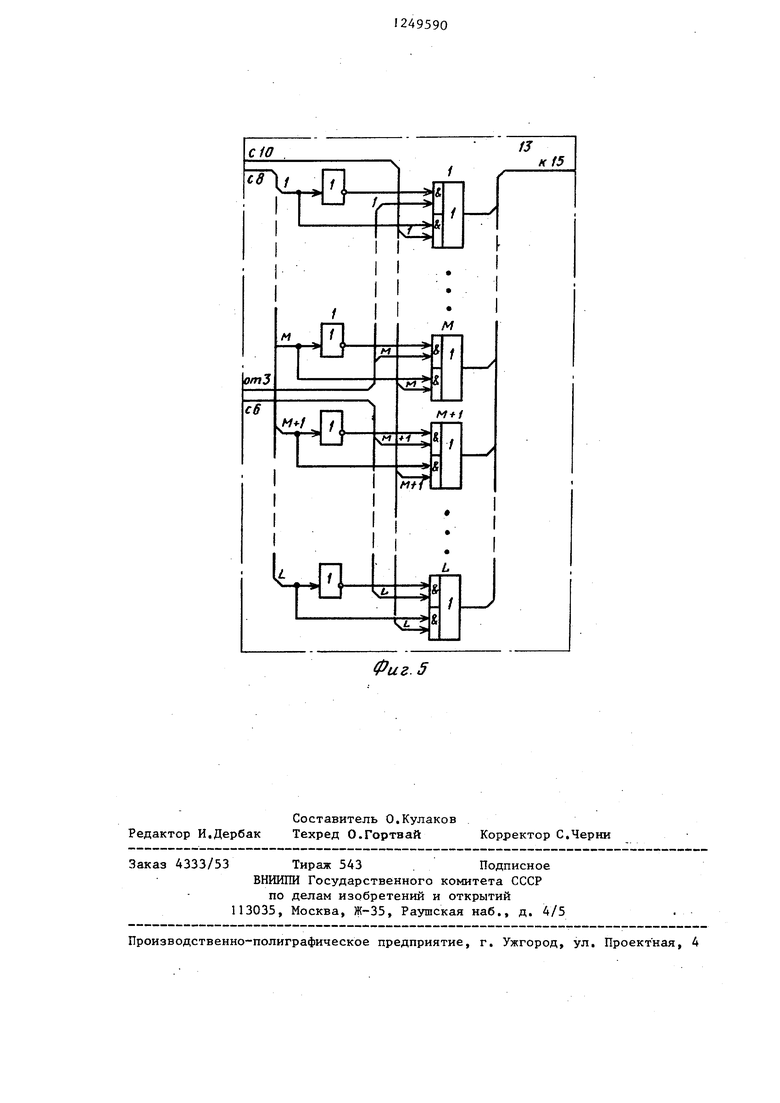

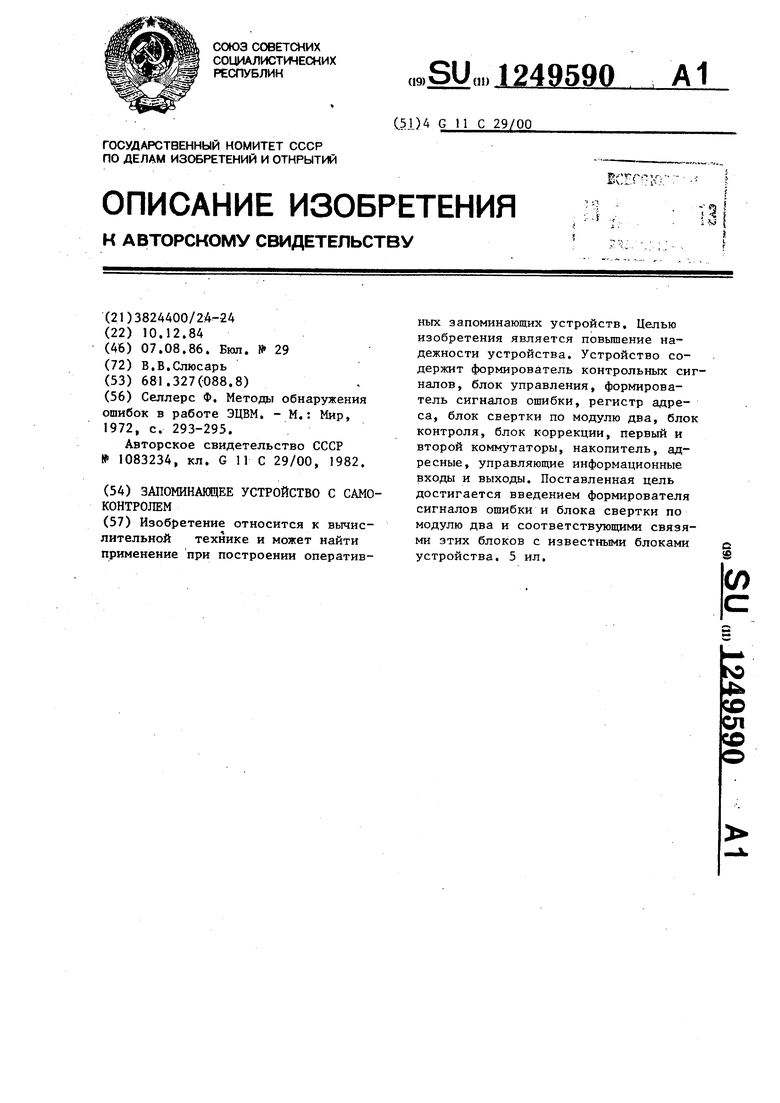

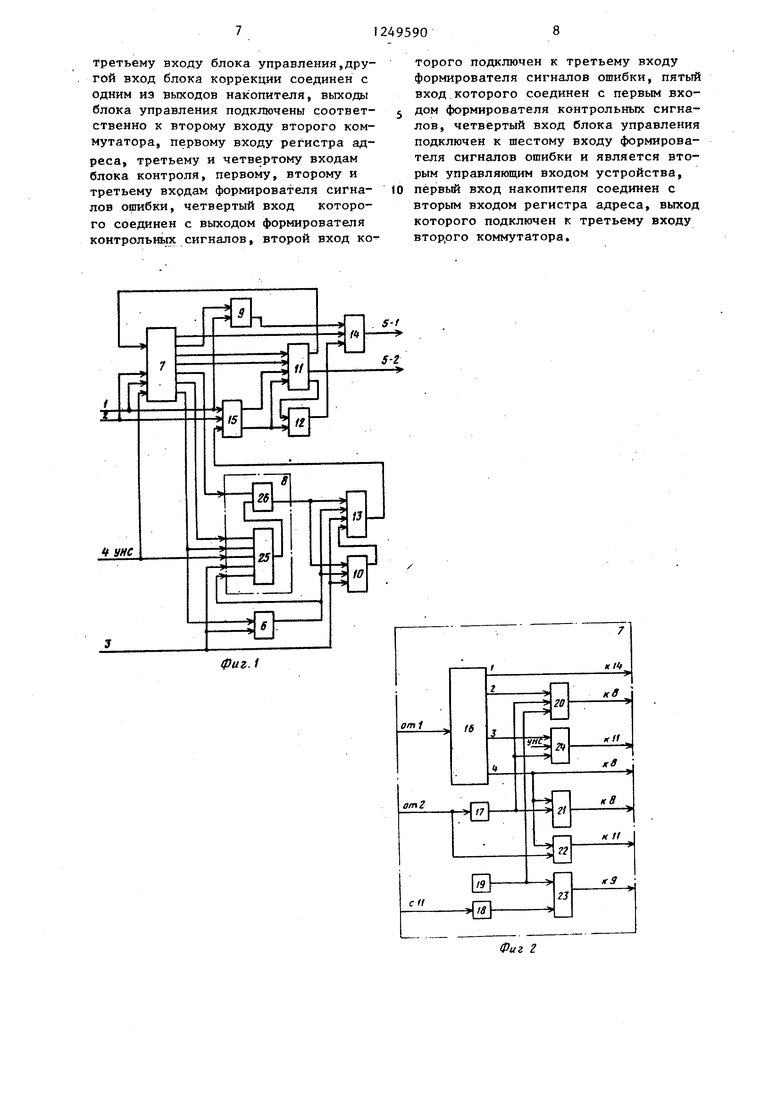

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока контроля; на фиг. 4 - схема блока свертки по модулю два; на фиг. 5 - схема первого коммутатора.

Устройство содержит адресные 1, управляющий 2, информационные 3,и второй управляющий 4 входы, выходы 5-1 и 5-2, формирователь 6 контрольных сигналов, блок 7 управления, формирователь 8 сигналов ошибки, ре- гистр 9 адреса, блок 10 свертки по модулю два, блок 11 контроля, блок 12 коррекции, первый 13 и второй 14 коммутаторы и накопитель 15.

Формирователь 6 контрольных разрядов представляет собой блок элементов свертки по модулю два, предназначен для формирования дополнительных контрольных разрядов с использованием, например, матрицы кода Хзмминга и может быть реализован на интегральных микросхемах ИМС

Блок 7 управления (фиг. 2) содержит дешифратор 16,элементы НЕ 17 и 18 генератор 19, элементы И 20- 23 и триггер 24д предназначен яля формирования управляюпщх сигналов, синхронизирующих работу узлов устройства.

Формирователь 8 сигналов ошибки содержит регистр 25 сдвига с параллельной записью и элемент И 26,

Регистр 9 адреса предназначен для хранения кода адреса, при чтении по которому данных с накопителя 15 происходит сбой.

Блок 10 свертки по модулю два (фиг. 4) выполнен на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ.

Блок 11 контроля (фиг. 3),содержащий формирователь 27 синдромов, элемент НЕ 28, свертку 29 по модулю два, дешифратор 30 номера корректирующего разряда, элементы И 31, НЕ 32, И 33 и ИЛИ 34, предназначен для анализа считанной из накопителя 15 информации и формирования сигнало ошибок.

5

Блок 12 коррекции предназначен для исправления тех разрядов данных, в которых обнаружены ошибки, и представляет собой блок сверток по модулю два.

Коммутатор 13 (фиг. 5) предназначен для формирования истинных либо и инверсных значений основных и контрольных разрядов данных. Коммутатор 14 предназначен для формирования на выходе устройства откорректированного кода данных либо при наличии сбоев кода адреса сбойной ячейки контролируемой памяти. Накопитель 15 предназначен для временного хранения кода данных.

Перед началом работы устройство устанавливается в начальное состояние. Установка осуществляется про- 0 граммно или оператором по цепи 4.

В начальном состоянии на выходах регистра 25 формирователя 8 сигналов ошибки устанавливается уровень Лог. О и устройство готово к работе в штатном режиме.

Устройство работает следующим образом.

Информационные разряды даннь1х поступают с информационной входной шины 3 на входы формирователя 6 контрольных сигналов, формирователя 8 сигнала ошибки, блока 10 свертки по модулю два и коммутатора 13. На выходе Формирователя 6 формируетсяj 5 используя матрицу кода Хэмминга, дополнительные контрольные разряды которые поступают затем иа блоки 8, 10 и 13. Таким образом, на выхо-- дах коммутатора 13 присутствуют сигналы с информационной шины 3 и с выхода формирователя 6,

5

0

0

Количество разрядов сдвигового регистра 25 формирователя 8 сигналов ошибки соответствует числу основных (информационных) и дополнительных (контрольных) разрядов данных, поступающих на его вход.

Количество ИМС блока 10 свертки по модулю два и коммутатора 14 соот- ветствует числу разрядов сдвигового регистра 25.

С выхода коммутатора 13 основные и контрольные разряды данных поступа- ют на вход накопителя 15, запись в

последний осуществляется по призна- ку Запись, который выставляется процессором на шине 2. При этом на

вотне 1 адреса процессор выставляет код адреса ячейки накопителя 15.

В режиме чтения блок 11 контроля анализирует записанные в накопитель 15 информационные и контрольные разряды данных. При обнаружении однократной ошибки блок 12 коррекции инвертирует искаженный .разряд. С выхода блока 12 коррекции через коммутатор 14 данные поступают на информа-Ю записи, нулевой р&ряд данных инверционные выхрды 5 устройства.

Если количество искаж енных разрядов данных, поступающих на блок 11 контроля превьшгает корректируюш е вможности кода Хэмминга, на одном из выходов блока I 1 формируется сигнал Ошибка с уровнем Лог. О, поступающий на блок 7 управления. В последнем сигнал Ошибка инвертируется элементом НЕ 18 и поступает на первый вход элемента И 23, на второй вход которого поступает тактова частота с местного генератора 19. Далее сигнал Ошибка с выхода блока 7 поступает на синхронизирующий вход регистра 9 адреса, при этом призводится запись кода адреса сбойной ячейки по другому входу регистра 9 с шины 1 адреса. По сигналу, поступающему с выхода дешифратора 16 бло- ка 7 управления, сигнал с выхода регистра 9 через коммутатор 14 подключается к выходной шине 5, Этот сигнал формируется при выставлении процессором на шину адреса кода подключения , который является адресом одной из ячеек накопителя 15 из общего поля адресов доступных процес сору.

При проведении диагностики узлов ОЗУ имитируется однократная ошибка. Для нанесения однократной ошибки в данные,которые заносятся в накопитель 15,процессор выставляет код вида 00.., 01 на шину 3 данных и код адреса за- писи на шину 1 адреса, который является адресом одной из ячеек накопителя 15 из общего поля адресов, доступных процессору. Код адреса записи формирует на втором выходе де- шифратора 16 блока 7 управления сигнал Лог. 1.

При наличии признака Запись на шине 2 управления с второго выхода блока 7 управления поступает сигнал на третий вхоД формирователя 6, При этом в регистр 25 сдвига формирователя 8 записывается код данных,, посту

2495904

пающий с информационной шины 3, и блокируется работа формирователя 6, на выходах которого формируется уровень Лог. О. На выходе регистра 5 25 формирователя 8 формируется код вида 00...01. Этот код, имеющий 1 в нулевом разряде данных, указывает, что при обращении к накопителю по вполне определенному адресу в режиме

20 25 зо

5 0

5

5

0

тируется.

Код адреса ячейки накопителя выбирается из условия максимального числа обращений к ней программы процессора. Например, при использовании ОЗУ в аппаратуре, предназначенной для построения центров коммутации сообщений, таким кодом адреса может быть адрес одной из буферных ячеек накопителя. Обычно буферная зона накопителя занимает объем в 32-64 ячейки и при средней длине сообщения 300- 400 знаков код адреса ячейки буферной зоны даже при приеме одного сообщения формируется несколько раз.

Пусть код адреса ячейки накопителя имеет вид 1010...10. При обращении процессора к ячейке с таким кодом адреса в режиме записи на четвертом выходе дешифратора 16 блока 7 управления формируется сигнал, который поступает на первый вход формирователя 8 сигналов ошибки, разрешая прохождение сигналов с регистра 25 через элемент И 26 на входы коммутатора 13 и блока 10.

ИМС блока 10 свертки по модулю два (фиг. 4) инвертируют нулевой разряд кода, поступающего с информационной шины 3, под действием 1, присутствующей в нулевом разряде кода, поступающего на блок 10 с выхода формирователя 8. Сигнал с выхода блока 10 свертки по модулю два поступает на входы ИМС коммутатора 13, В результате в накопитель 15 в ячейку с адресом 1010...10 записывается код данных с искаженным нулевым разрядом.

Признак Запись, поступающий на управляюш 1й вход 2 устройства, является синхронизирующим. При снятии этого признака по заднему фронту сигнала, сформированного на пятом выходе блока 7 управления, сдвиговый регистр 25 формирователя 8 сигнала ошибки продвигает 1 из нулевого в первый разряд. Вследствие этого при следующем обращении к накопителю 15

l-IMC блока 10 свертки по модулю два инвертируют первый разряд кода.

При .чтении информации буферной области накопителя 15 на шестом вы- ходе блока 7 управления формируется сигнал с уровнем Лог. О, который поступает на четвертый вход блока 11 контроля. При анализе сбойного слова данных на выходе формирователя 27 блока 11 появляется код адреса сбойного разряда, а свертка 29 по модулю два зафиксирует наличие одиночного сбоя. Правильность работы элементов 27 и 29 блока 11 анализируется по сигналу с уровнем Лог. 1 на одном из входов элемента И 33 блока 1I, Если в момент анализа на выходе элемента И 33 блока 11 появляется синал с уровнем Лог. О, то по выход- ной цепи 2 в процессор поступает сигнал Ошибка.

Затем точно также проверяется реакция блока 11.контроля на искажение второго и последующих разрядов кода данных.

После восьми циклов запись/чтение при по-байтовой организации, поступающей на шину 3 информации, будет проверена реакция узлов ОЗУ на искажени основных разрядов данных.

Затем анализируются реакция узлов ОЗУ на искажение дополнительных ( контрольных/ разрядов.

Если исправляющая способность ко- да равна единице, то такой контроль, который проводится в процессе функционирования ОЗУ, можно считать достаточным для проверки его узлов,

При записи в регистре 25 формиро- вателя 8 сигналов ошибки кода, в котором присутствует две 1, диагностируются двойные сбои. Эти 1 могут быть записаны в любые разряды регистра. Диагностика на обнаружение двойных сбоев проводится во время отсутствия информации в канапе связи к которому относится область буферной зоны накопителя. Это может быть, например, время между получением KOM бинации Конец текста КТ на принимаемое сообщение и до установления нового соединения. Поэтому процессор не реагирует на искаженный байт данных, считанный из накопителя 15.

В процессе диагностики процессор проверяет функционирование второго т оммутатора 14, регистра 9 адреса.

блока 7 управления и блока 11 контроля. Функционирование этих узлов проверяется по коду адреса блокировки, выставленному процессором. Блокировке подвергается элемент 29 блока 1. При этом в пегистр 9 апоеся заносится код адреса ячейки ОЗУ, имеющей сбойную информацию, а по входной цепи 5-2 процессор информируется о наличии некорректируемой ошибки. По этому сигналу процессор начинает анализировать сбойную информацию, которая поступает с регистра 9 через коммутатор 14 на выходную цепь 5-1 устройства.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее формирователь контрольных сигналов, регистр адреса, блок контроля, накопитель, блок коррекции, первый и второй коммутаторы,- блок управления, первый и второй входы которого подключены к первому -и второму входам накопителя и являются адресным и первым управля- юшим входами устройства, информационным входом которого является первый вход формирователя контрольных сигналов, выход которого соединен с первым входом первого коммутатора, выход которого подключен к третьему входу накопителя первый выход блока контроля соединенс одним входом блока коррекции, выход которого подключен к первому входу второго ком- мутатора, выход которого и второй выход блока контроля являются выходами устройетва, отличающееся тем, что, с целью повьш1ения надежности, в него введены формирователь сигналов ошибки и блок свертки по модулю два, входы которого подключены к выходу формирователя сигналов ошибки, выходу и первому входу формирователя контрольных сигналов, выход блока свертки по модулю два соединен с вторым входом первого коммутатора, третий и четвертый входы которого подключены соответственно к выходу формирователя сигналов ошибки и к первому входу формирователя контрольных сигналов, выходы накопителя соединены с первым и вторым входами блока контроля, третий выход которого подключен к

третьему входу блока управления,другой вход блока коррекции соединен с одним из выходов накопителя, выходы блока управления подключены соответственно к второму входу второго коммутатора, первому входу регистра адреса, третьему и четвертому входам блока контроля, первому, второму и третьему входам формирователя сигналов ошибки, четвертый вход которого соединен с выходом формирователя контрольньгх сигналов, второй вход которого подключен к третьему входу формирователя сигналов ошибки, пятый вход которого соединен с первым вхо- дом формирователя контрольных сигналов, четвертый вход блока управления подключен к шестому входу формирователя сигналов ошибки и является вторым управляющим входом устройства, первый вход накопителя соединен с вторым входом регистра адреса, выход которого подключен к третьему входу вторрго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

| Резервированное запоминающее устройство | 1980 |

|

SU936035A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

Изобретение относится к вычислительной технике и может найти применение при построении оперативных запоминающих устройств. Целью изобретения является повьппение надежности устройства. Устройство содержит формирователь контрольных сигналов, блок управления, формирователь сигналов ошибки, регистр адреса, блок свертки по модулю два, блок контроля, блок коррекции, первый и второй коммутаторы, накопитель, адресные, управляющие информационные входы и выходы. Поставленная цель достигается введением формирователя сигналов ошибки и блока свертки по модулю два и соответствующими связями этих блоков с известными блоками устройства. 5 ил. с $ (Л

(Риг.1

/4

го

кО

ami

16

л

кИ

от г

-Ч 7

21

19

к а

с 11

23

Фиг. 3

8

w

Х13

7

с6

Y

r

u

И

c3

fe(

ФигЛ

Фиг. 5

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| - М.: Мир, 1972, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПОДАЧИ УГЛЯ В ТЕНДЕР ПАРОВОЗА | 1920 |

|

SU293A1 |

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-07—Публикация

1984-12-10—Подача