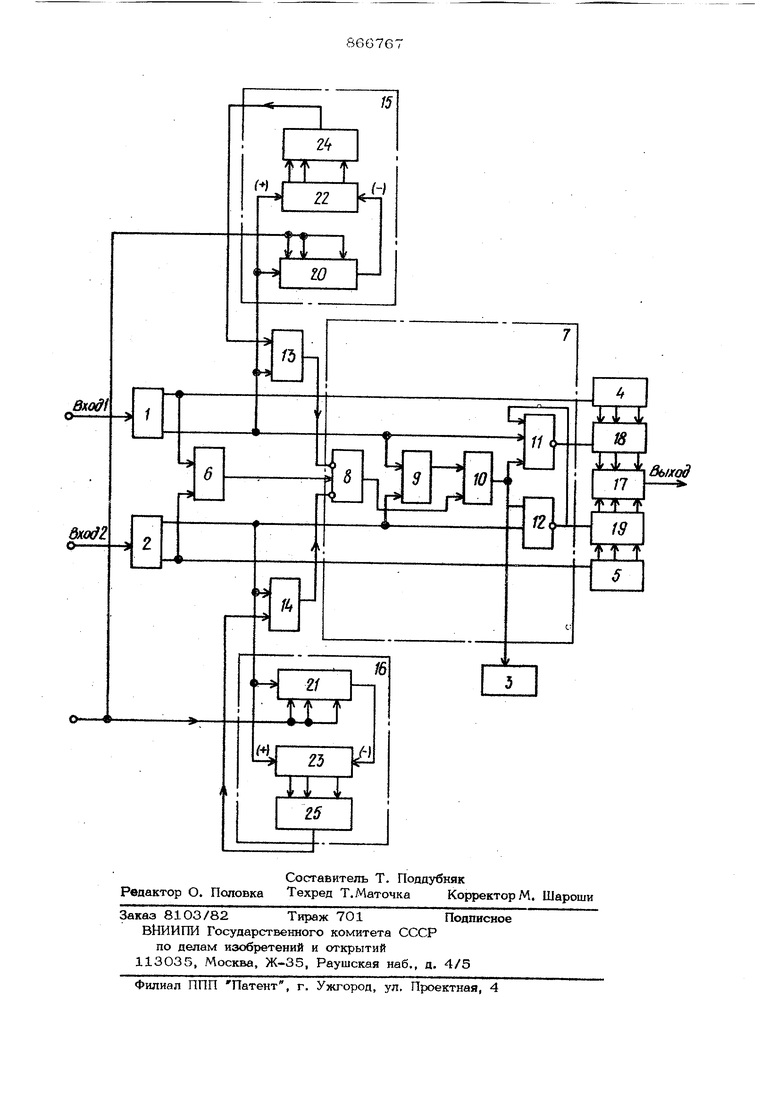

6 накопителя и к соответствующему входу сумматора по модулю два, а управляющий выход - к соответствующему входу логической схемы, включенной на выходе сумматора по модулю два, при этом выходы каждого накопителя подключены к соответствующим входам регистра выдачи информации через ключевой блок, управляемый логической схемой, один из выходов которой подключен к управляющему входу блока управления повторением кодовых ко комбинаций, введены в каждый канал анализатор плотности ошибок элемент ИЛИ, выход которого подсоединен к дополнительному входу логической схемы, первый вход элемента ИЛИ объединен с управляющим выходом блока повыщения достоверности и входам анализатора плотности ошибок, выход которого подключен ко вто рому входу элемента ИЛИ, кроме того, анализатор плотности ощибок содержит последовательно соединенные регистр, реверсивный счетчик и декодер, выход которого является выходом анализатора плотности ощибок, вход регистра объединен с дополнительным, входом ревесивного счетчику и является входом анализатора плотности ошибок, а на входы Сброс регист ра поданы тактовые импульсы. На чертеже представлена структурноэлектрическая схема устройства. Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью содержит блоки 1 и 2 повышения достоверности (по одному в каждой канапе связи), блок 3 управления повторением кодовых комбинаций. Инфор шционный выход каждого из блоков 1 и 2 повышения достоверности подключен ко входу соответствующего накопителя 4 или 5 и к соответствующему входу сумматора 6 по модулю два, а управляющий выход - к соответствующему входу логической схемы 7, состоящей из элемента 8 запрета, элемента И 9, элемента ИЛИ Ю и элементов ИЛИ-НЕ 11 и 12, включенной на выходе сумматора 6 по модулю дв а также объединен с первыми входами элементов ИЛИ 13 и 14 и входами анализаторов 15 и 16 плотности ощибок. Вы ходы каждого из накопителей 4 и 5 подключены к соответствующим входам регистра 17 выдачи информации через ключевые блоки IS и 19, управляемые логи ческой схемой 7, один из выходов которо подключен к управляющему входу блока 3 управления повторением кодовых комбинаций. Анализатор 15{16 плотности оши74бок содержит последовательно соединенные регистр 20 (21), реверсивный счетчик 22 (23) и декодер 24 (25). Устройство работает следующим образом. Импульсы информации с информационных выходов блоков 1 и 2 повышения достоверности записываются в накопители 4 и 5, но в регистр 17 выдачи информации и далее на выход устройства информация поступает только в моменты, когда открыты ключевые блоки: 18 и 19. Управление ключевыми блоками 18 и 19 осуигествляет логическая схема 7. При обнаружении ошибок в сообщениях на управляющем входе соответствующего блока 1 или 2 повышения достоверности возникйет единичный сигнал, который через элементы ИЛИ-НЕ 11 или 12 запирает соответствующий ключевой блок 18или 19. При этом, если ошибки обнаружены Б обоих каналах, то осуществляется переспрос кодовой комбинации за счет сигнала, возникающего на выходе элемента И 9 и через элемент ИЛИ 10 воздействующего на блок 3 управления повторением кодовых комбинаций. Одновременно с записью накопиуели 4 и 5 информация с выходов блоков 1 и 2 повышения достоверности поступает для сравнения на сумматор 6 по модулю два. Возникающий на выходе сумматора 6 импульс несравнения указывает на появление необнаруженной ошибки. Этот импульс через элемент ИЛИ 10 осуществляет переспрос кодовой комбинации. Если в одном из параллельных каналов резко возрастает вероятность п х пенкя необнаруженных ошибок, то существенно увеличится количество сигналов на выходе сумматора 6, а следовательно, и число переспросов. Несмотря на то, что в другом канале информация может проходить без искажу НИИ, больщое число переспросов, по существу, заблокирует качественный канал. Для предотвращения этого в устройство введены анализаторы 15 и 16 плотности ошибок, которые следят за количеством ошибок в заданной выборке знаков . При достижении установленного лимита ошибок в выборке, анализатор 15 (16) плотности ошибок вырабатывает сигнал, отключающий вывод результата сравнения информации на сумматоре 6. Число разрядов регистра 2О(21), входящего в состав анализатора 15(16) плотности ошибок, определяется длиной 5S выборки знаков tt , а количество разрядов К реверсивного счетчика 22(23) определяется ид соотношения . Ошибкн, обнаруженные блоком 1(2) повышения достоверности, с его управляющего выхода в виде единичных сигналов поступают на вход Ц -разрядного регистра 20(21) и на вход сложения реверсивного счетчика 22(23). Когда на реверсивный счетчик 22(23) поступит уста новленное число ошибок, на выходе декодера 24(25) возникает сигнал, который снимается только тогда, когда число оши бок, зафиксированных реверсивным счетчиком 22(23), будет меньше нормы (сигнал на выходе декодера существует при числе ошибок, равном или превышающем норму). Сигнал с выхода декодера 24(25) через элемент ИЛИ 13(14) поступает на запрещающий вход элемента 8, выключая вывод результатов сравнения, а следо вательно, предотвращая переспросы, Сигналы с выхода и -разрядного регистра 20(21) поступают на вход вычитания реверсивного счетчика 22(23), уменьшая на единицу записанное в нем число. В результате этого анализатор 15(16) плотности ошибок непрерывно следит за числом ошибок в заданной выборке знаков, т.е. за плотностью ошибок. Технико-экономическая эффективность гфедложенного устройства заключается в том, что в устройстве осуществлен анализ состояния каналов, на основе которого обеспечивается управление поэлементным сравнением информации, что приводит к резкому снижению числа переспросов 76 в системе при ухудшении качества одного из каналов, т.е. к повышению производительности системы в целом. Формула изобретения 1.Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью по авт. св. № 473314, отличаю,шееся тем, что, с целью повышения быстродействия системы путем уменьшения количества переспросов введены в каждый анализатор плотности ошибок и элемент ИЛИ, выход которого подсоединен к дополнительному входу логической схемы, первый вход элемента ИЛИ объединен с управляющим выходом блока повышения достоверности и входом анализатора плотности ошибок, выход которого подключен ко входу элемента ИЛИ. 2.Устройство по п. 1, отличающее с я тем, что анализатор плотности ошибок содержит последовательно соединенные регистр, реверсивный счетчик и декодер, выход которого является выходом анализатора плотности ошибок, вход регистра объединен с дополнительным входом реверсивного счетчика и является входом анализатора плотности ошибок, а на входы Сброс регистра поданы тактовые импульсы. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 473314, кл. Н О4 U 1/16, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решаюшей обратной связью | 1977 |

|

SU657635A2 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Устройство для приема информации по двум параллельным каналам связи | 1979 |

|

SU873437A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью | 2018 |

|

RU2696329C2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU655081A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ С ПОВЫШЕННОЙ ДОСТОВЕРНОСТЬЮ | 2013 |

|

RU2530335C1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1972 |

|

SU473314A1 |

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1981 |

|

SU1008918A2 |

| Устройство для приема дискретной информации | 1977 |

|

SU649156A1 |

Авторы

Даты

1981-09-23—Публикация

1979-12-17—Подача