00

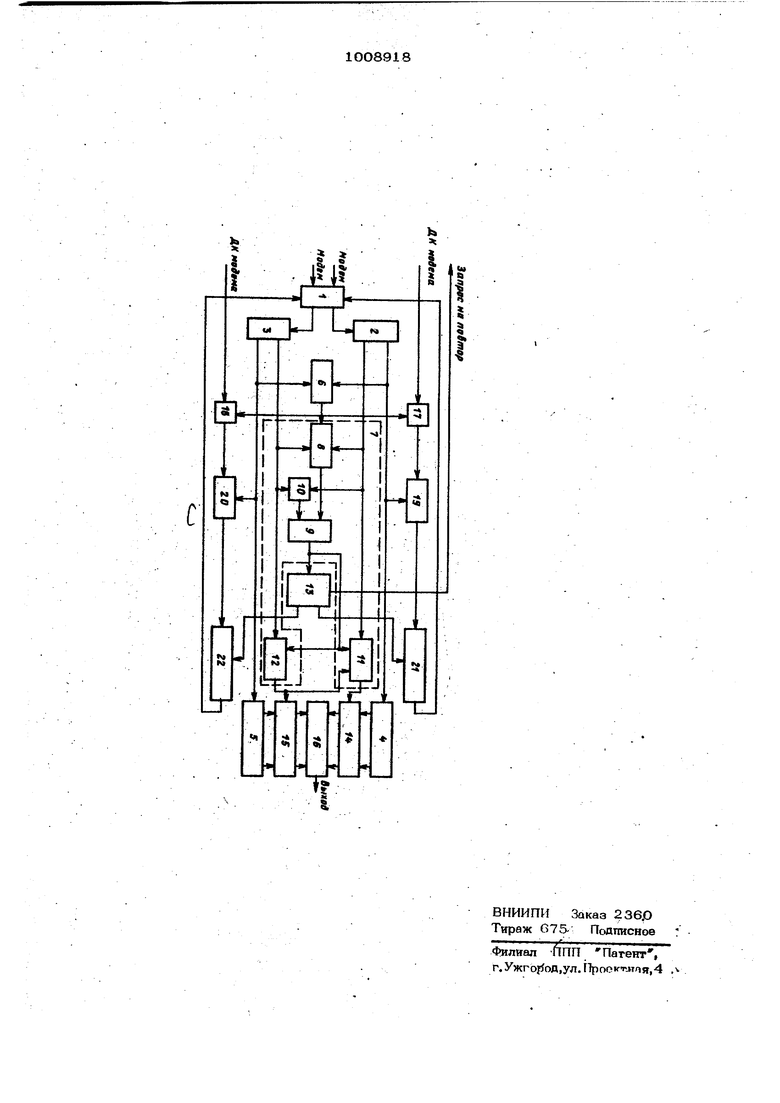

00 Изобретение относигся к технике передачи данных и может быть использовано в аппаратуре передачи данных с решакяпей обратной Связью. По основтжлу авт. св. № 473314 . известно устройство для гфкема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью, содержащее блок повышения достоверности в каждом канале связи и блок управления повторением кодовых комбинаций, при этом информационный №«ход каждого блока повышения достовер ности подключен к входу соответствующего накопителя и к соответствующему входу сумматора по модулю два, а управляющий вход - к соответствующему входу логического блока, включенного на выход сумматора по , при этом выхо ды каждого накопителя подключены к соответствующим входам регист{м выдачи информации через ключевой блок, управляемый логическим блОКСЯЛ; один ВЗ ВЬ1ХОДО которого подключен к управляющему вход блока управления повторением кодовых комбинаций, кроме того, логический блок состоит из элемента запрета, элемента ИЛИ, двух элементов ЙЛИ-НЕ, первого .элемента И, первый и второй входы которого объединены соответственно с, первым и вторым входами элемента запрета к первыми входами двух элементсэв ИЛИНЕ, к вторым объединенным входам которых подключен выход элемента ИЛИ, к входам которого подключены выходы первого элемента И и элемента запрета, а выход второго элемента ИЛИ-НЕ подключен к третьему входу первого элемента ИЛИ-НЕ, причемвходы запрета являются входами логичесжого блока, выходами которого являются выходы элементов ИЛИ и ИЛИ-НЕ l . Однако известное устройство обладает низкой помехоустойчивостью из-за значительного уменьшения скорости передачи в каналах низкого качества, обусловленного частыми перезапросами кодовых блоков. Цель изобретения - повышение помехоустойчивости.. Поставленная цель достигается тем, что устройство для .приема информации по двум параллельным каналам связи в системе передачи данных с решающей обрат. .ной связью, содержащее блок повышения достоверности в каждом канале связи и блок управления повторением кодовых комбинаций, при этом информационный ВЫХОД каждого блока повыщения достоверности подключен к входу соответствующего накопителя и к соответствук щему входу сумматора по модулю два, а управляющий вХод - к соответствующему входу логического блока, включенного на выходе сумматора по модулю два, при этом выхода 1 каждого накопителя подключены к соответствующим входам регистра:ВЫ дач и информации через клк чевой блок, управляемый логическим блоком, один из выходов которого подклк чен к управляющему входу блока управления повторением кодовых комбинаций, кроме того, логический блок состоит из элемента запрета, элемента ИЛИ, двух элементов ИЛИ-НЕ и первого элемента И, первый и второй входы которого объединены соответственно с первым и вторым входами элемента запрета и первыми входами двух элементов ИЛИНЕ, к вторым объединенным входам которых подключен выход элемента ИЛИ, к входам которого подключены выходы первого элемента И и элемента запрета, а выход второго элемента ИЛИ-НЕ подключен к третьему входу первого элемента ИЛИ-НЕ, причем входы элемента запрета являются входами логического блока, выходами которого являются выходы элементов ИЛИ и ИЛИ-НЕ, введены коммутатор и последовательно соединенные второй элемент И, второй сумматор по модулю два и третий накопитель, а также последовательно соединенные третий элемент И, третий сумматор по модулю два и четвертый накопитель, к вторс ду входу которого, а также к второму входу третьего накопителя подклк. чены выходы блока управления повторением кодовых комбинаций, при этом вторые входы второго н третьего сумматоров по модулю два объединены соответственно с первым и вторым входами первого сумматора по модулю два, выход которого подключен к первым входам второго и третьего эл ентов И, вторые входы которых являются входами стирания устройства, а выходы третье) и четвертого накопителей подключены cooi ветственно к первому и второму входам коммутатора, выходы которого подклк чены к входам первого н второго блоков повышения достоверности, причем третий И четвертый входы коммутатора являются информационными входами устройства. Н4 чертеже представлена структурная электрическая схема предлагаемого устройства. Усггройство содержит ком1М утатор 1, - блоки 2 в 3 повышения достовервсюти, первый и второй накопите;1И 4 и 5, первый сумматор6 по. модулю два, погический бпок 7, состоящий из элемента 8 запрета, элемента ИЛИ 9, первого элемента И 1О, двух элементов ИЛИ-НЕ 11 и 12, блокр 13 управления повторением кодовых комбинаций, ключевые блоки 14 и 15, регистр 16 выдачи иифрмаани, второй и третий элементы И17 и 18, второй и третий сумматоры 19 и 2О по модулю два, третий и четвертый накопители 21 и 22. Устройство работает следующим образом. В режиме приема двоичных символов кодовой комбииаиии из каналов связи к шутатор 1 обеспечивает прием и выдачу двоичных символов из каналов связ на выходы блоков 2 и 3 повышения достоверности (БПД) и блокирует два других входа соединенные соответственно с выходами третьего и четвертого накопителей 21 И 22, Двошиые символы информации с выходов БПД 2 и 3 поступают од 1юв|)еменво в первый,и второй накопители 4 и 5, на входы первого сумма тора 6 по модулю два, где происходит п зрядное сравнение кодовых комбшшций, и на входы второго и третьего сумматоров 19 и 20 по модулю два. Параллельно двоичным си дволам кодовых комбинаций синфазно и синхронно на входы второго и третьего элементов И 17 18 поступают последовательности сигналов условных стираний. Первый сумматор 6 по модулю два, вторс элемент И 17, второй сумматор 19 по модулю два и первый сумматор 6 по модулю два, тре:тий элемент И 18, третий сумматор 2О по модулю два обеспечивают исправление ошибок по критерию большинства два нз трех, используя совокупность пвух параллельно поступающих койовых комбинаций и последовательности сигналов условных стираний. С вьгходбв второго и третье1Ч сумматоров 19 и 20 по модулю, два исправлеиюле кодовые комбинации поступают соответственно b третий и четвертый накопители 21 и 22. Сигна Несравнение с выхода первого суммаToi 6 по модулю два проходит на входы блока 13 управления повторением кодовых комбинаций и элементов ИЛИ-НН 11 и 12 только тогда, когда суправляющих выходов БПД 2 и 3 Ие 1ю Ьтупают сигна ЕЫОшибка в комбинации . По сигналу Несравнение с выходов элементов ИЛИ-НЕ 11 и ИЛИ-НЕ 12 на выходы ключевых блоков 14 и 15 поступают блокирующие сигналы, и информация, поступигалая с информационных выходов БПД 2 и 3, не переписывается в регистр. 16 выходной .информации на вход и получателю не поступает. Одновременно по сигналу Несргшнёние блок 13 управления повторением кодовых комбинаций на входы третьего и четвертого вакопителей 21и 22 выдает сигналы, по которым исправленные кодовые комбинации с их . выходов через коммутатор 1 1юступают на входы БПД 2 и 3. Запрет перезаписи информации из первого и второго накоп телей 4 и 5 поступит в регистр. 16 выдачи информации через ключевые блоки 14 и 15, считывание информации в БПД 2 и 3 с третьего и четвертого накопителей 21 и 22через коммутатор 1 по сигналам с блока 13 управления повторением кодо-; вых ксФдбннаций происходит и тогда, когда одновременно на управляющих входах БПД 2 и 3 появляются сигналы Ошибка в кодовой комбинации, которые объединяются на первом элементе И 1О и через элемент ИЛИ 9 поступают на вхо- ДЬ1. блока 13 управления щдаторений«( кодовых комбинаций и входы элементов ИЛИ-НЕ 11 и 12 Кодовые комбинации, портуцившие из перюго и второго накопителей 4 и 5 в БШГ 2 и 3, вновь декодируются. И если на управляющем вь ходе хотя бы одного БПД 2 или 3 Ошибка в комбинации от- сутствует, то информация из Первого или второго накопителя 4 или 5 перепишется в регистр 16 выдачи и юрмашга и поступит на вход получателя. Во ос- тальных случаях на вхся блока 13 уп- . равления повторени@ « кодовых комбииа- ций поступит повторно сигнал Несра&нение или Ошибка в кодовой комбинации. Б этом случае с выхода блока 13 управления повторением кодовых комбишций поступит запрос на повторную передачу искаженной кодовой комбинации. Если при первом декодщюваиии принима и(ой koaoBcxI к %4бинации отсутствует на управляющем выходе хотя бы , одного БПД 2 и 3 сигнал ОшибкгГ в ко щэвой комбинации , то информ йия с выхода первого или второго на&опителя 4 или 5 перепишется в регистр 16 выдачи информации и поступит к получателю. В этом случае декодиршание исправлекн ных кодовых ксмбинаДий, находящихся

5i008&.84

в первом и втором накопителях 4 и 5,личивает вероятность правильного приема

не происходит н устройство готово ккодовых комбинаций за счет исправпеприему спедуклцих кодовых комбинаций.ния ошибок с использованием сигналов

Использование предлагаемого устрой- s личению эффективной скорости передачи ства повышает помехоустойчивость, уве- информации.

условных стираний, что приводит к увеk

Ь

at

с

§

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU655081A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU660288A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ С ПОВЫШЕННОЙ ДОСТОВЕРНОСТЬЮ | 2013 |

|

RU2530335C1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решаюшей обратной связью | 1977 |

|

SU657635A2 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Устройство для приема информации по двум параллельным каналам связи | 1979 |

|

SU873437A1 |

| Система передачи информации с решающей обратной связью | 1984 |

|

SU1167746A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью | 2018 |

|

RU2696329C2 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ ПО ДВУМ ПАРАЛЛЕЛЬНЫМ КАНАЛАМ СВЯЗИ В СИСТЕМЕ ПЕРЕДАЧИ ДАННЫХ С РЁШАЮШЕЙ ОБРАТНОЙ СВЯЗЬЮ по авт. св. № 473314, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены коммутатор и последовательно соединенные второй элемент И, второй сумматор по модулю два и третий накопитель, а также последовательно соединенные третий элемент И, третий сумматор по модулю два и четвертый накопитель, к второму входу которого, а также к второму входу третьего накопителя подключены выходы блока управления повторением кодовых комбинаций, при этом вторые входы второго и третьего сумматоров по модулю два объединешл соответственно с пегюым и вторым входаMTI первого сумматора по модулю два, выход которого подключен к первым входам второго и третьег о элементов И, вторые, входы которых являются входами стирания устройства, а выходы третьего и четвертого накопителей пошелючены соответственно к первому и второму вхоV дам коммутатора, выходы которого под- ключенЫ к входам первого и второго блоков повышения достоверности, причем третий и четвертый входы коммутатора являются инфор 1ационнь ми входами устройства.,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1972 |

|

SU473314A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-03-30—Публикация

1981-11-13—Подача