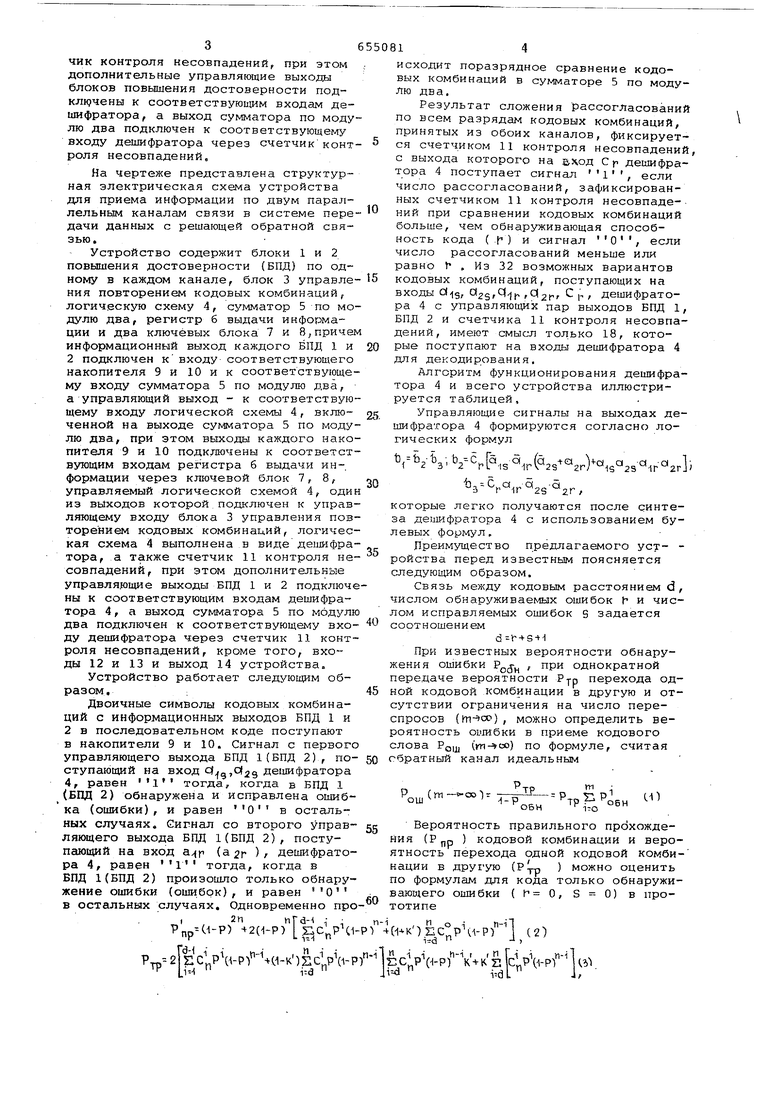

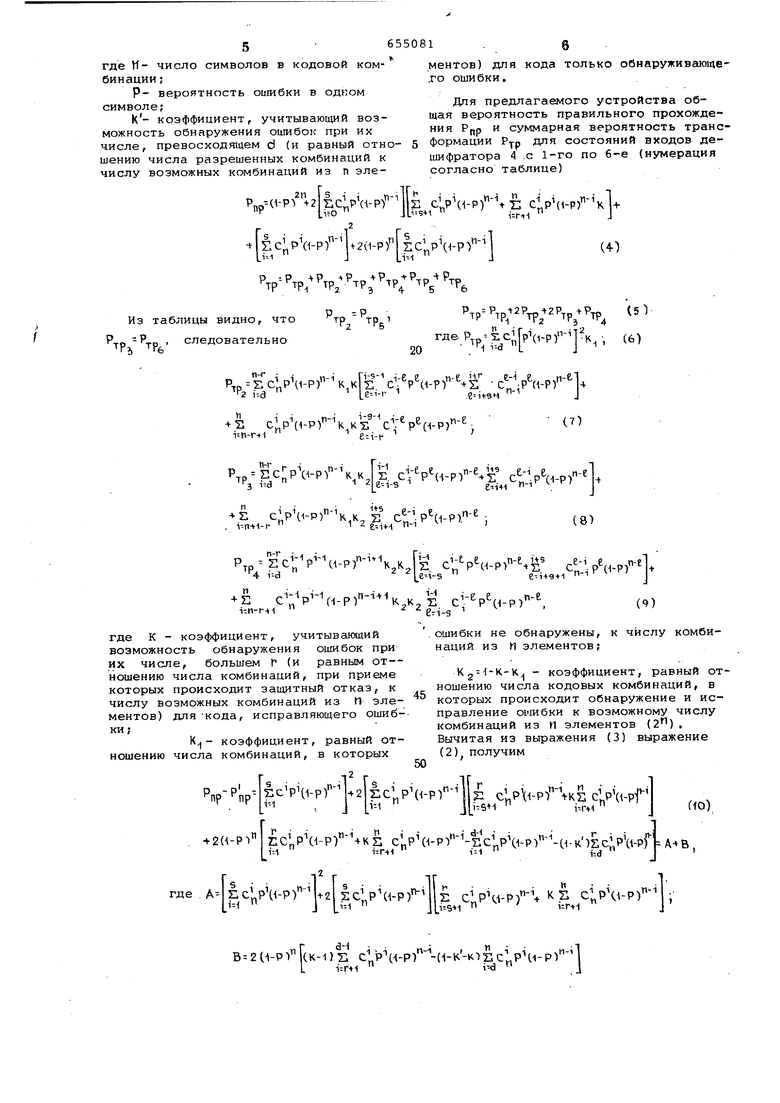

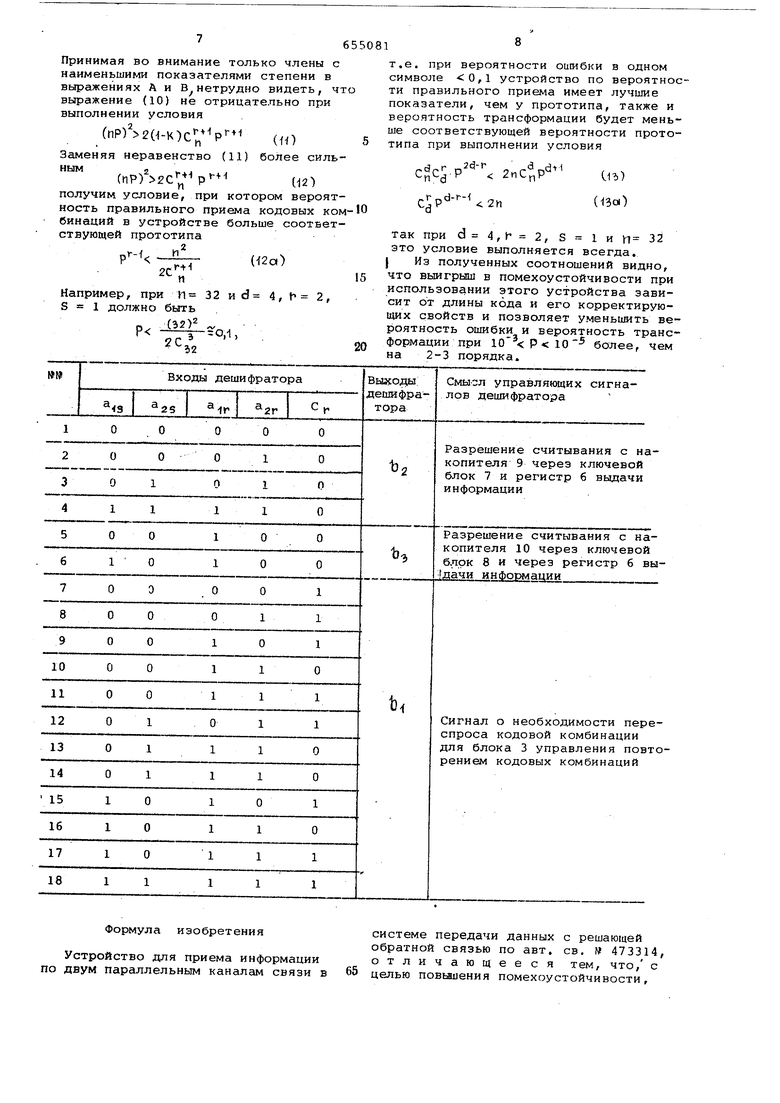

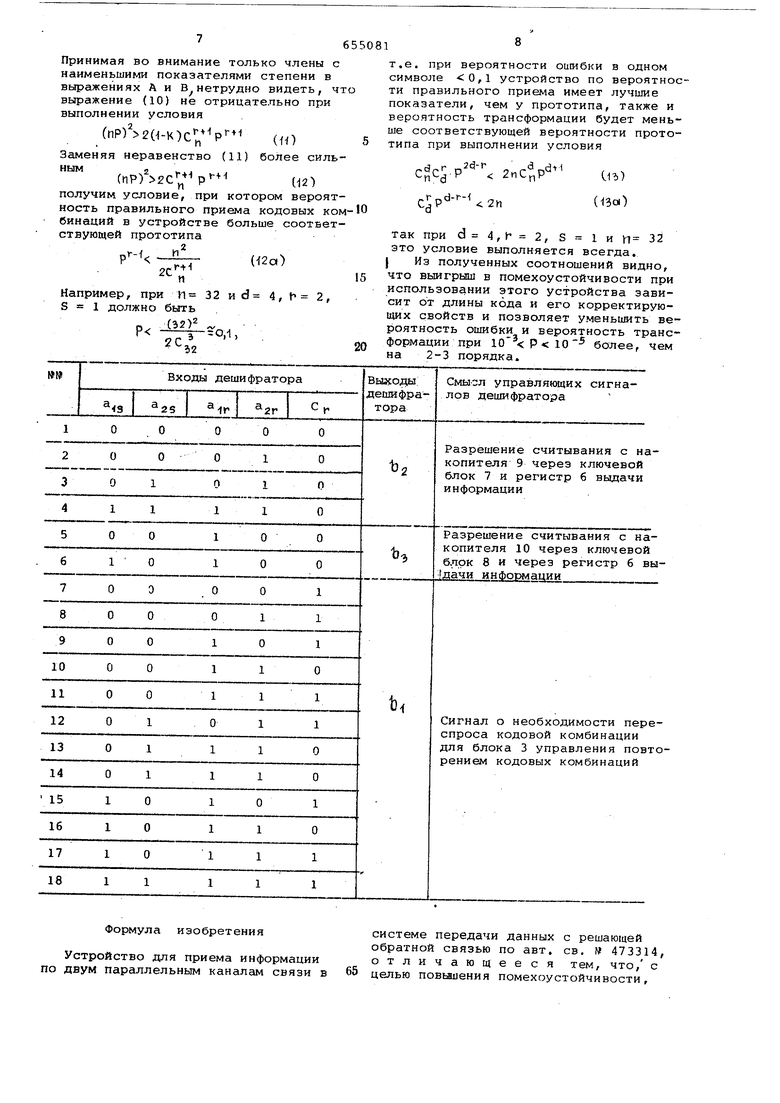

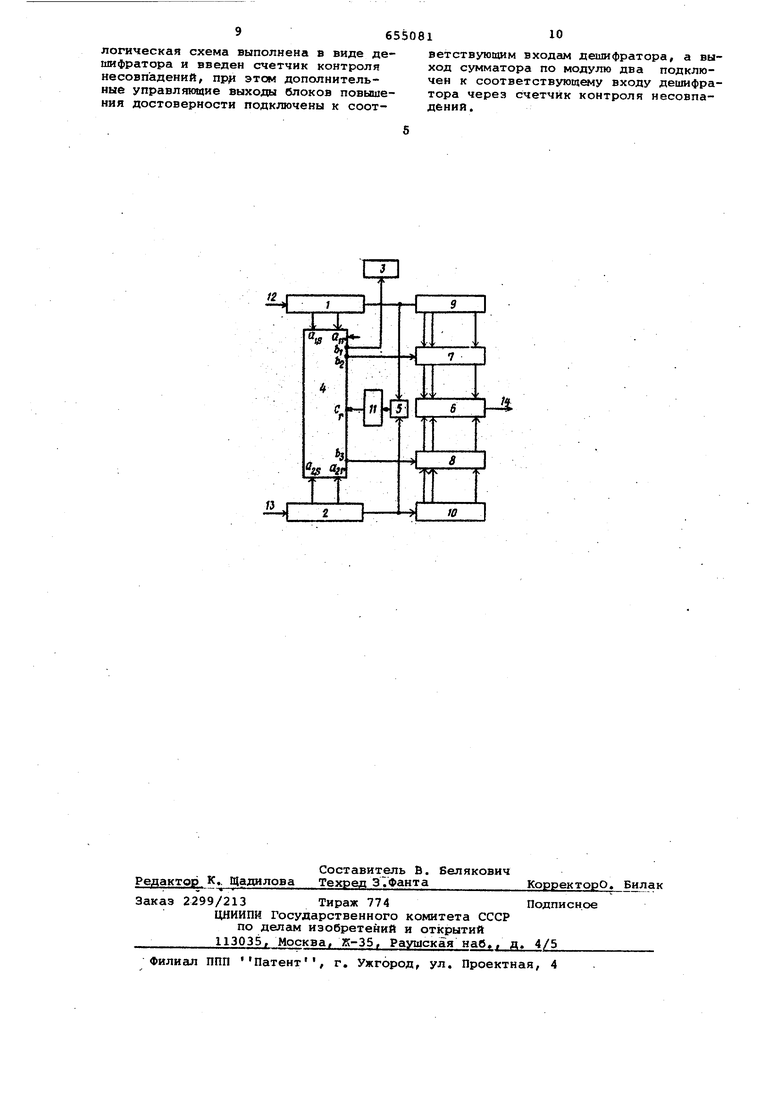

36 чик контроля несовпадений, при этом дополнительные управляющие выходы блоков повЕлшения достоверности подклнрчены к соответствующим входам дешифратора, а выход сумматора по модулю два подключен к соответствующему входу дешифратора через счетчикконтроля несовпадений, На чертеже представлена структур ная электрическая схема устройства для приема информации по двум параллельным каналам связи в системе пере дачи данных с решающей обратной связью. Устройство содержит блоки 1 и 2 повышения достоверности (БПД) по одному в каждом канале, блок 3 управления повторением кодовых комбинаций, логическую схему 4, сумматор 5 по модулю два, регистр б выдачи информации и два ключевых блока 7 и 8,причем информационный выход каждого БПД 1 и 2 подключен к входу соответствующего накопителя 9 и 10 и к соответствующему входу сумматора 5 по модулю два, а управляющий выход - к соответствующему входу логической схемы 4, включенной на выходе сумматора 5 по модулю два, при этом выходы каждого накопителя 9 и 10 подк.лючены к соответствующим входам регистра б выдачи информации через ключевой блок 7,8, управляемый логической схемой 4, один из выходов которой,подключен к управляющему входу блока 3 управления повторением кодовых комбинаций, логическая схема 4 выполнена в виде де1лифра тора, .а также счетчик 11 контроля несовпадений, при этом дополнительные управляющие выходы БПД 1 и 2 подключе ны к соответствующим входам дешифратора 4, а выход сумматора 5 по модулю два подключен к соответствующему вхо ду дешифратора через счетчик 11 контроля несовпадений, кроме того, входы 12 и 13 и выход 14 устройства. Устройство работает следующим образом, ; Двоичные символы кодовых комбинаций с информационных выходов КПД 1 и 2 в последовательном коде поступают в накопители 9 и 10, Сигнал с первого управляющего выхода БПД 1(БПД 2), поступающий на вход c)g, дешифратора 4, равен тогда, когда в БПД 1 (БПД 2) обнаружена и исправлена ошибка (ошибки), и равен О в остальных случаях. Сигнал со второго управлякицего выхода БПД 1(БПД 2), поступающий на вход ( )г дешифратора 4, равен тогда, когда в БПД 1(БПД 2) произошло только обнаружение ошибки (ошибок), и равен О в остальных случаях. Одновременно про , 2П nfd-i i . Pnp l-Р 2(1-Р) I SC РЧ1гp --2 sc;p i-P чt1-к) Li--l r-d 1исходит поразрядное сравнение кодовых комбинаций в сумматоре 5 по модулю два. Результат сложения Рассогласований по всем разрядам кодовых комбинаций, принятых из обоих каналов, фиксируется счетчиком 11 контроля несовпадений. с выхода которого на С дешифратора 4 поступает сигнал , если число рассогласований, зафиксированных счетчиком 11 контроля несовпаде-. НИИ при сравнении кодовых комбинаций больше, чем обнаруживающая способность кода ( .f-) и сигнал О, если число рассогласований меньше или равно У . Из 32 возможных вариантов кодовых комбинаций, поступающих на входы , , ,0|2гг С |, , дешифратора 4 с управляющих пар выходов БПД 1, БПД 2 и счетчика 11 контроля несовпадений, имеют смысл только 18, которые поступают на входы дешифратора 4 для декодирования. Алгоритм функционирования дешифратора 4 и всего устройства иллюстрируется таблицей. Управляющие сигналы на выходах дешифратора 4 формируются согласно логических формул 2-Ч-. ,з,р()« в 25«1Г 2г ; , которые легко получаются после синтеза децифратора 4 с использованием буевых формул. Преимущество предлагаемого уст- ройства перед известным поясняется следующим образом. Связь между кодовым расстоянием d, числом обнаруживаемых ошибок h и числом исправляемых ошибок s задается соотношением d V-vs-H При известных вероятности обнаружения ошибки , при однократной передаче вероятности Р-рр перехода одной кодовой комбинации в другую и отсутствии ограничения на число переспросов (() , можно определить вероятность оишбки в приеме кодового слова РОЩ () по формуле, считая обратный канал идеальным РОШ - -РОБНВероятность правильного прохождеНИЯ (Р j,p ) КОДОВОЙ комбинации и вероятность перехода одной кодовой комбинации в другую ( ) можно оценить по формулам для кода только обнаруживающего ошибки ( t О, 3 0) в прототипеИ о i n-Л ()21С„р - -Р) (2) i-,3 п -1 ) ёc;p -p кI: c;pVpfl i--d i,dL i, 5 65508 где М- число символов в кодовой ком- бинации; Р- вероятность ошибки в одном символе; k- коэффициент, учитывающий возможность обнаружения ошибок при их числе, превосходящем d (и равный отно- 5 шению числа разрешенных комбинаций к числу возможных комбинаций из п элеr-(vP..) )- с;р,-р)

ЧР

L -JU-s ii:p -( J

l;4pVprl2(i-P)i:c;p H-p)- (4)

U--1 J Li-i J

Р - Р то

Из таблицы видно, что Р,о -РТО следовательно

Гэ, Рб

ц--|c;p 1-P)-ч к |:;c7 p)

s )

-s.

i n-r+i e-i-|.

Vp;|c:;pVP.,,p, t.e,,n-el

;.,..),s c5; PVp „;|сГР Ч,.Р,--к,к,| с«р„.р,«,,..„-

п

c:p c -P) r.l-eг,. „.n-e

+ S

itn-r-t-i где К - коэффициент, учитывающий возможность обнаружения ошибок при их числе, большем Y (и равным от - ношению числа комбинаций, при приеме которых происходит защитный отказ, к числу возможных комбинаций из И элементов) длякода, исправляющего ошиёки; коэффициент, равный отношению числа комбинаций, в которых

i;cP4i-pVj.).K c;pWf )))4pVpfl где A--U:cLp bPr Mt2

B 20-Pi4(K-i)s c p i-pr-d-K-KisctpHi-Pi

i--d

p VV;ЧЧ

),, (6)

,n-E

(8)

K2K2 s, )(9

fio)

, )-i 1Ы с;РЧ1-Р)- к )- |; 1 . Q ментов) для кода только обнаруживающего ошибки. предлагаемого устройства вероятность правильного прохожде я РПР суммарная вероятность трансФормации для состояний входов дешифратора 4 .с 1-го по 6-е (нумерация согласно таблице) сшибки не обнаружены, к числу комбинаций из И элементов; - коэффициент, равный отношению числа кодовых комбинаций, в которых происходит обнаружение и исправление ошибки к возможному числу комбинаций из И элементов (2) , Вычитая из выражения (3) выражение (2) получим

Принимая во внимание только члены с наименьшими показателями степени в выражениях А и В нетрудно видеть, что выражение (10) не отрицательно при выполнении условия

(ПР) 20-K)C V

(iO Заменяя неравенство (11) более силь (пр) ня получим условие, при котором вероят ность правильного приема кодовых ко бинаций в устройстве больше соответ ствующей прототипа ,2 32 и d 4, h 2, Например, при И S 1 должно быть (32)

т.е. при вероятности ошибки в одном символе 0,1 устройство по вероятности правильного приема имеет лучшие показатели, чем у прототипа, также и вероятность трансформации будет меньше соответствующей вероятности прототипа при выполнении условия pdpr p2c3-f Cn-d так при ,, 8 это условие выполняется всегда. I Из полученных соотношений видно, что выигрыш в помехоустойчивости при использовании этого устройства зависит от длины кода и его корректирующих свойств и позволяет уменьшить вероятность ошибки и вероятность трансформации при более, чем на 2-3 порядка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в кодовой комбинации | 1991 |

|

SU1830616A1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1984 |

|

SU1202057A1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1115055A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема сообщений вСиСТЕМАХ пЕРЕдАчи иНфОРМАции C РЕшА-ющЕй ОбРАТНОй СВязью | 1979 |

|

SU849517A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

Формула изобретения

Устройство для приема информации по двум Параллельным каналам связи в

системе передачи данных с решающей обратной связью по авт. св. W 473314, отличающееся тем, что, с целью повышения помехоустойчивости.

логическая схема выполнена в виде дешифратора и введен счетчик контроля несовпадений, пр этом дополнительные управляющие выходы блоков повышения достоверности подключены к соотулиг

V

jg огг

fj

ветствующим входам дешифратора, а выход сумматора по модулю два подключен к соответствующему входу дешифратора через счетчик контроля несовпадения.

НЗСХ }I-J

I

Авторы

Даты

1979-03-30—Публикация

1977-06-10—Подача