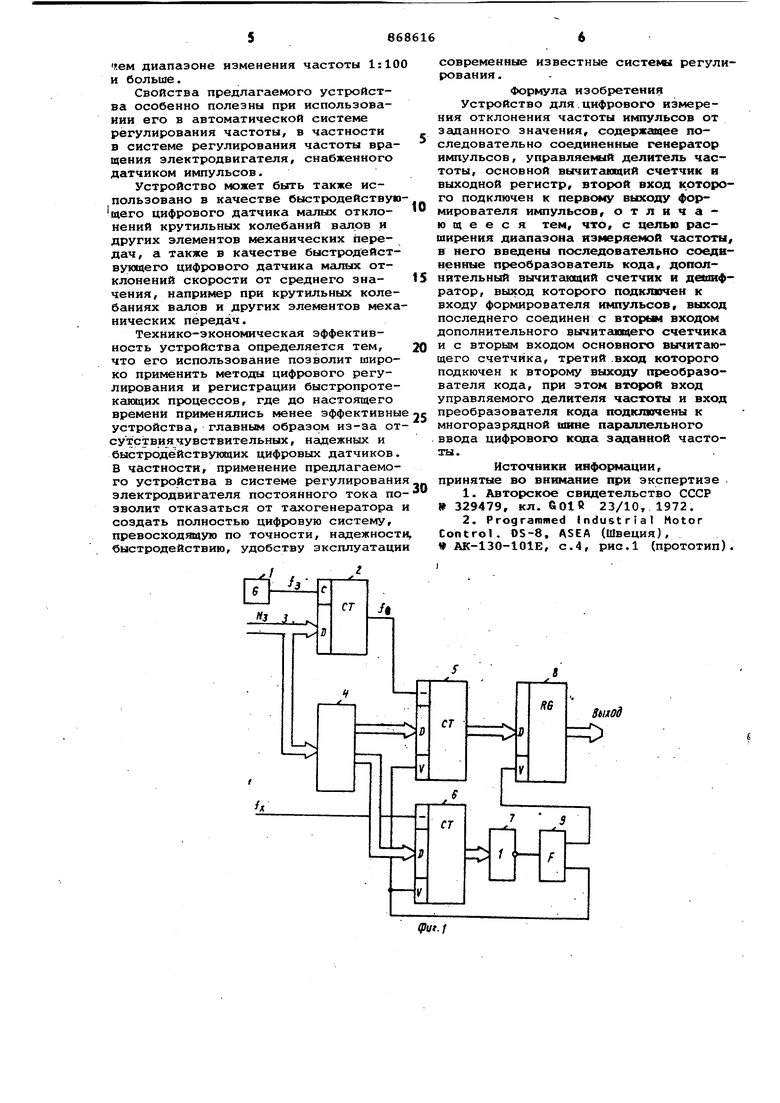

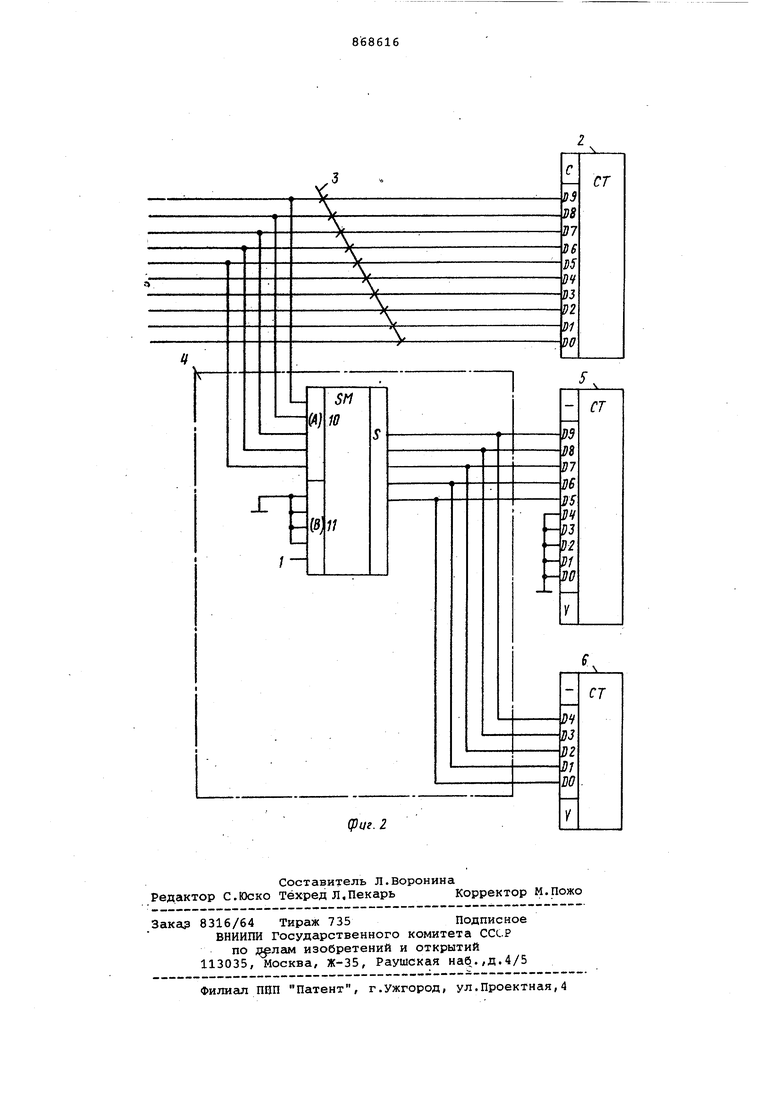

Устройство содержит генератор 1 импульсов стабильной частоты, управляемый делитель 2 частоты, многоразрядную шину 3 параллельного ввода .цифрового кода, комбинационный преобразователь 4 кода, представляющий собой комбинационный сумматор, вычитающий счетчик 5, вычитающий счетчик б, дешифратор 7 нуля, выполненный в виде многовходовой схемы ИЛИ-НЕ, вы-у ходной регистр 8 и формирователь 9 импульсов. Первый выход формирователя 9 подключен к управляющему входу регистра 8, а второй выход - к управлянадим входам ачетчиков 5 и 6.

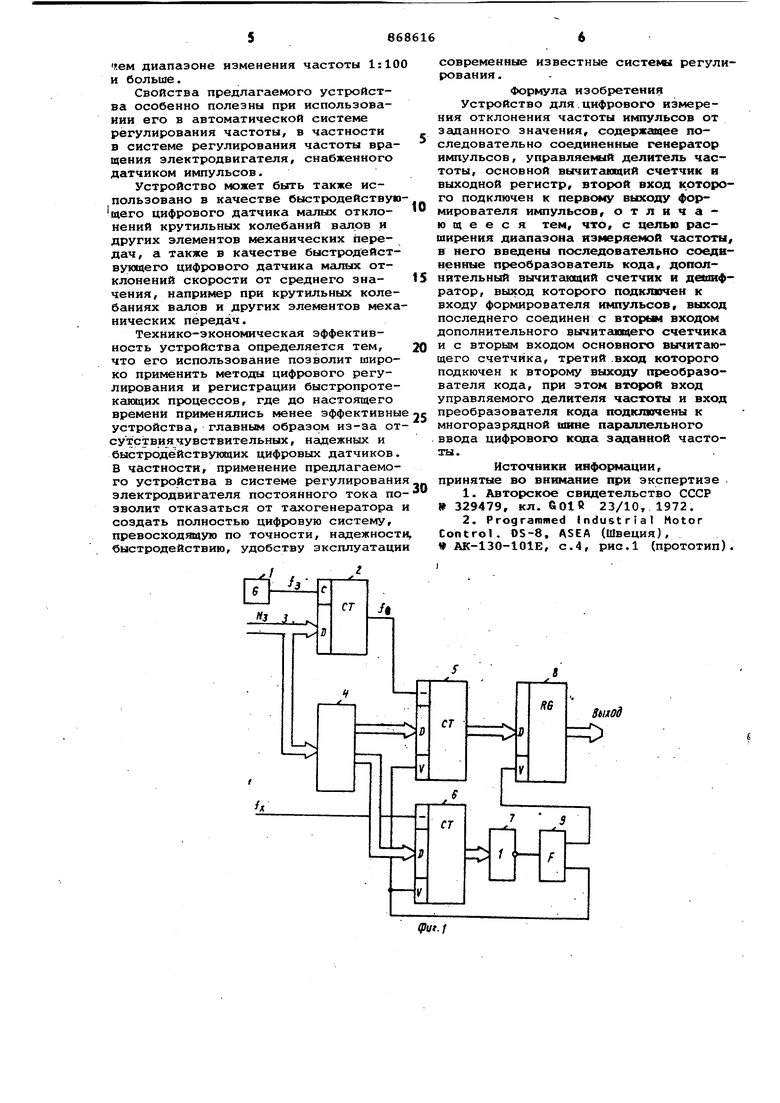

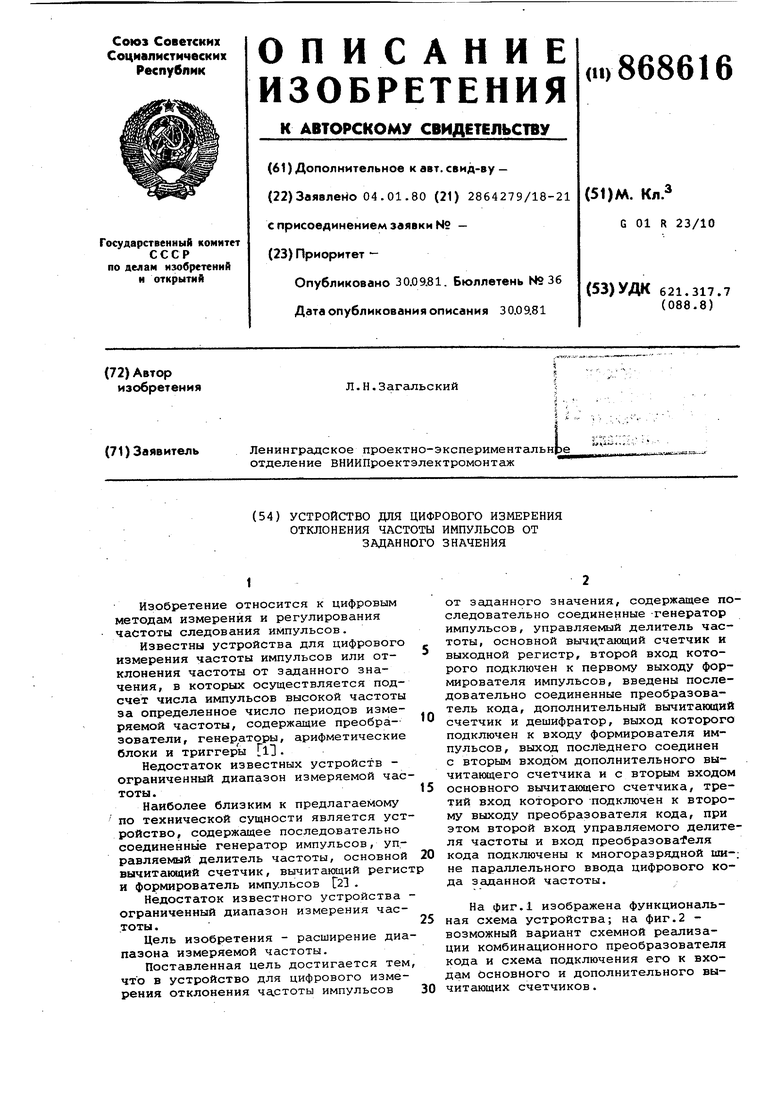

В качестве примера реализации преобразователя 4 кода на фиг.2 показан комбинационный сумматор, вход и выход которого определеннным образом, поясняемым ниже,подключены к шине 3 и счетчикам 5 и 6«

Устройство работает следующим образом.

По многоразрядной шине 3 на вход управляемого делителя 2 частоты и пробразователя 4 кода подается код числа N-j , пропорционального заданной частоте f . Частота импульсов f на выходе управляемого делителя 2 частоты пропорциональна числу Ni, , а следовательно заданной частоте f,j

(1).

A.f

&

На выходах преобразов формируются коды чисел К чем число К представляет ленное в болы1 ую сторону деления N на А мэг Цэ

+ 1

к L А

гдеГ- - целая часть дробного чисN-). . ла М .

Число К вводится в дополнительный счетчик 6, а число АК - в основной счетчик 5.

Схемная реализация преобразователя кода осуи ствляется весьма просто, если выбрать число А равным

А Z, где а - целое число.

На фиг.2 приведен пример осуэдествле1| ия преобразователя кода при выбранном числе А 32, Для представления числа NUпринят десятиразрядный двоичный код. Двоичный код числа К формируется в соответствии с формуло (2) (комбинационным сулййахором, на вхо; 10 (А) кот.орого по многоразрядной шине 3 поступают пять старших разрядов числа N-i, , а на вход 11 (В) код числа 1.

Число к поступает на вход дополнительного счетчика 6 непосредственно, а на вход основного счетчика 5 со сдвигом влево на пять разрядов, что эквивалентно умножению его на , А 32.

На вычитающий вход основного счетчика 5 поступают импульсы с частотой fg от управляемого делителя частоты, а на вход дополнительного счетчика 6 - импульсы измеряемой частоты f. е Цикл измерения начинается в момент появления импульса на втором выходе формирователя 9, который осуществляет ввод в счетчик 5 числа АК, а в счетчик 6 - числа К. В течение 0 цикла измерения содержимое счетчиков 5 и 6 уменьшается с частотей f. и f соответственно. Когда содержимое счетчика 6 становится равнь1м нулю срабатывает дешифратор 7 нуля и формирователь 9. Импульс на первом выходе формирователя 9 производит перепись содержимого первого счетчика 5 в регистр 8, импульс на втором выходе вновь вводит числа АК и К в счет- Ч1КИ 5 и 6, т.е. инициирует новый цикл 0 измерения.

Длительность цикла измерения равна

Т - fxU)«

Результат измерения выражается 5 (число, записанное в регистре 8)

W..)

т(.)

%

где С-коэффициент пропорциональности

между Nj и fj . Из уравнения (2) следует, что АК N 3 . Если отклонение измеряемой частотны от заданной мало, т.е. fg f jr , то имеет место приближенное равенство

(5).

с lf,- fjt

Из формул (4) и (5) следует, что выходное число Ny, пропорционально разности измеряемой и заданной частоты. Хотя коэффициент пропорциональности непостоянен но его вариации тем меньше, чем больше число К и чем меньше рассогласование измеряемой и заданной частоты. В частности устройство фиксирует без погрешности равенство fj и fx (при этом выходное число N„5, 0) .

Из описания следует, что при изменении измеряемой частоты в широком диапазоне длительность цикла измерения меняется незначительно, так ка с ростом заданной частоты пропорционально возрастает число К периодов измеряемой частоты. Отсюда вытекает, что установленное быстродействие устройства сохраняется неизменным в широких пределах.

При практической реализации на серийных интегральных микросхемах можно достичь достаточно высокого быстродействия (длительность цикла измерения составляет 1-2 мс) в рабоS66нем диапазоне изменения частоты 1:10 и больше. Свойства предлагаемого устройства особенно полезны при использовании его в автоматической системе регулирования частоты, в частности в системе регулирования частоты вращения электродвигателя, снабженного датчиком импульсов. Устройство может быть также использовано в качестве быстродействую щего цифрового датчика малых отклонений крутильных колебаний валов и других элементов механических передач, а также в качестве быстродействующего цифрового датчика малых отклонений скорости от среднего значения, например при крутильных колебаниях валов и других элементов меха нических передач. Технико-экономическая эффективность устройства определяется тем, что его использование позволит широко применить методы цифрового регулирования и регистрации быстропротекающих процессов, где до насто$пцего времени применялись менее эффективны устройства, главньм образом из-аа от сутствия чувствительных, надежных и быстродействующих цифровЕ к датчиков. В частности, применение предлагаемого устройства в системе регулировани электродвигателя постоянного тока по зволит отказаться от тахогенератора создать полностью цифровую систему, превосходяцую по точности, надежност быстродействию, удобству эксплуатаци современные известные система регулирования. Формула изобретения Устройство для.цифрового измерения отклонения частоты импульсов от заданного значения, содержспцее последовательно соединенные генератор импульсов, управляекий делитель частоты, основной вычитающий счетчик и выходной регистр, второй вход которого подключен к первенцу выходу формирователя икшульсов, отличающееся тем, что, с целью расширения диапазона измеряемой частоты, в него введены последовательно соединенные преобразователь кода, дополнительный вычитсцощий счетчик и дешифратор, выход которого подключен к входу формирователя импульсов, выход последнего соединен с вторым входе дополнительного зычитахщего счетчика и с вторым входом основного вычитающего счетчика, третий .вход которого подкючен к второму выходу преобразователя кода, при этом второй вход управляемого делителя частоты и вход преобразователя кода подключены к многоразрядной шине параллельного ввода цифрового кода заданной частоты. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 329479, кл. GOlft 23/10, 1972. 2.Programmed industrial Motor Control. OS-8, ASEA (Швеция), W AK-130-101E, C.4, рис.1 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| Устройство для ввода информации | 1986 |

|

SU1439568A2 |

| Аналого-цифровой преобразователь с цифровой коррекцией | 1982 |

|

SU1069157A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1272509A1 |

| Преобразователь частота-код | 1983 |

|

SU1129543A1 |

| Устройство для ввода информации | 1986 |

|

SU1339541A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

ст

ft} 3.

Я6

Выход

СТ

ьо

Авторы

Даты

1981-09-30—Публикация

1980-01-04—Подача