подключены к входам обнуления второй группы D-триггеров и к пятому выходу процессора управления и индикации, аход разрешения синхронизации первой группы Т) vJpnrrepoB с.оединен с входами обнуления первой и второй групп двухразрядных двоичных счетчиков и с первым выходом процессора управления и индикации, выходы первой группы D-триггеров, объединенные монтажным ИЛИ, подключены к D-входам второй .группы 1Э-триггеров и к входу элемента задержки, выход которого подключен к входам разрешения синхронизации первой и второй групп двухразрядных двоичных счетчиков, выход генератора образцовой частоты соединен с входом пятого расщепителя фаз, прямые и инверсные выходы которого подключены к первым входам соответственно первой и второй половины второй группы элементов ИЛИ-НЕ, входы разрешения синхронизации второй группы -О-триггербв соединены с шестым выходом процессора управления и индикации, выходы второй группы -триггеров, объединенные монтажным ИЛИ, подключены к вторым входам первой и второй групп элементов ИЛИ-НЕ, выходы которых соединены со счетными входами соответственно первой и второй групп двухр.азрядных двоичных счетчиков, выходаа которых подключены к информационным входам соответственно первого и второго комбинационных дешифраторов, а также к входам соответственно первого и второго формирователей сигналов переноса, выход первого формирователя переноса соединен с входом коррекции первого комбинационного дешифратора и со счетным входом первого многоразрядного счетчика, выход второго формирователя переноса соединен с входом коррекции второго комбинационного дешифратора и со счетным входом второго многоразрядного счетчика, выходы первого и второго комбинационных дешифраторов подключены соответт ственно к третьему и четвертому входам процессора управления и индикации .

2. Частотомер по п. 1, отли чающийся тем,, что в нем при п-разрядных делителях частоты . ервый, второй, третий и четвертый асщепители фаз- последовательносей содержат по 2 -п - 1 счетных риггеров fA - 1-ступенчатой структуы, при этом количество триггеров -й ступени равно - 1, входы ри-ггеров с-и ступени подключены к рямым и инверсным выходам триггеов t- 1-й ступени и.к входу расщеителя фаз последовательностей, срдиненному с инверсным выходом

С-го разряда делителя частоты, а выходы расщепителя фаз последовательностей соединены с выходами триггеров последней п- 1-й ступени.

3.Частотомер по п. 1, отличающийся тем, что пятый расщепитель фаз последовательностей содержит 2 - 1 последовательно соединенные элементы задержки, при этом вход первого элемента задержки подклю,чен к входу расщепителя фаз последовательностей, выход предыдущего элемента задержки соединен с входом последующего элемента задержки, вход пятого расщепителя фаз последовательностей и выход каждого элемента задержки подключен к входу соответствующего им одного из 2 буфера, прямые и инверсные выходда которого соединены с выходами расщепителя фаз последовательностей.

4.Частотомер поп, 1, отличающийся тем, что первый и второй комбинационные дешифраторы содержат комбинационный сумматор, элемент ИЛИ, логический корректирующий элемент, первый вход которого

соединен с входом коррекции комбинационного дешифратора, информационные входы которого подключены к входам комбинационного сумматора и к вторым входам логического корректирующего элемента, выходы которого соединены с первыми входами элемента ИЛИ, вторые входы которого соединены с выходами старших разрядов комбинационного сумматора, выходы элемента ИЛИ и выходы младших разрядов комбинационного сумматора соединены с выходами соответственно старших и младших разрядов комбинационного дешифратора.

5.Частотомер по п. 1, отличающийся тем, что процессор управления и индикации содержит пульт задания режимов, управляющий автомат, блок индикации и арифметическое устройство, первый и второй входы /операндов которого подключены соответственно к первому и второму входам процессора управления и индикации, управляющий вход арифметического устройства соединен с первым выходом управляющего автомата, выходы признаков результата арифметического устройства подключены к первым входам условий управляющего автомата, выходы результата арифметического устройства соединены с информациокными входами блока индикации, управляющий вход которого соединен с вторым выходом управляющего автомата, третий, четвертый, пятый

и шестой выходы которого подключены срответственно к первому, четвертому, пятому и шестому выходам процессора управления и индикации, вторые

входы условий управляющего автомата подключены к первым выходам пульта задания режимов, второй и третий

выходы которого соединены соответственно с вторым и третьим входами процессора управления и индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для измерения отношения частот | 1988 |

|

SU1661664A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Фазометр | 1978 |

|

SU765750A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

1. ЦИФРОВОЙ ЧАСТОТОМЕР, содержащий первый делитель частоты, генератор образцовой частоты, первый входной формирователь, дйа многоразрядных счетчика, процессор управления и Индикации, первый и второй входы которого соединены соответственно с выходами первого и вто-. рого многоразрядных счетчиков, а первый выход процессора управления и индикации подключен к входам обнуления первого и второго многоразрядных счетчиков, отличающийся тем, что, с целью pacmiiрения функциональных возможностей, в него введены второй входной форкирователь, второй, третий и четвертый делители частоты, пять расщепителей фаз последовательностей, коммутатор , две группы D-триггеров, элемент задержки, две группы эпементов ИЛИ-НЕ, две группы двухразрядных двоичных счетиксв, два формирователя сигналов переноса, два комбинационных дешифратора, причем первые входы первого и второго входных формирователей подключены соответственно к первой и второй входным шинам устройства, вторые входы первого и второго входных формирователей соединены соответственно с вторым и третьим выходами процессора управления и индикации, прямой и инверсный выходы первого входного формирователя соединены соответственно с входами первого и второго делителей частоты, прямой и инверсный выходы второго входного формирователя подключены соответственно к входам третьего и четвертого делителей частоты, выходы старших разрядов первого, второго, третьего и четвертого делителей частоты соединены соответственно с первым, вторым, i третьим и четвертым входами коммутатора, инверсные выходы младших разрядов первого, второго, третьего и четвертого делителей частоты подключены соответственно через первый, второй, третий и четвертый расщепители фаз последовательностей соответственно к пятому, шестому, седьмому и восьмому входам коммутатора, управлякишй вход которого соединен с четвертым выходом процессора управления и индикации, первая группа прякых и инверсных выходов коммутатора соединена с входами синхронизации соответственно первой и второй половины первой группы D -триггеров, вторая группа выходов коммутатора соединена с входами синхронизации первых половин второй группы О-триггеров и первыми входами первой группы элементов ИЛИ-НЕ, вторая группа инверсных выходов коммутатора соединена с входами синхронизации вторых половин второй группы Т)-триггеров и первыми входами первой группы элементов ИЛИ-НЕ, D-входы первой группы О-триггеров подключены к шине логической единицы, входы обнуления -первой группы Т) -триггеров

Изобретение относится к информационно-измерительной технике и может быть использовано для.автоматического измерения частоты, периода, интервалов и длительностей сигналов произвольной формы.

Известен цифровой частотоккр, содержащий декадные счетчики, генератор образцовой частоты, коммутатор блок управления, формирователи Cll.

Однако этот цифровой частотомер отличается низким быстродействием, обусловленным применением декадных счетчиков с обратными связями, а также проблемами коммутации сигналов и стробообразования.

Наиболее близким к изобретению являетсй цифровой частотомер ,.содержащий первый делитель частоты, генератор образцовой частоты, первый входной формирователь, два многоразрядных счетчик,, процессор управления и индикации, первый и второй входы которого соединены соответственно с выходами первого и второго многоразрядных счетчиков, а первый выход процессора управления и индикации подключен к входам обнуления первого и второго многоразрядных счетчиков t2j

В известном частотомере достигнуто максимальное быстродействие, однако при этом существенно сужены функциональные возможности - производится только измерение частЧэты и периода входного сигнала и невозможна реализация таких традиционных режимов, как измерение интервалов, длительностей импульсов, отношения частот двух сигналов, непосредственный счет входных импульсов и т.д.

Цель изобретения - расширение функциональных возможностей.

Поставленная цель достигается тем, что в цифровой частотомер, содержащий первый делитель частоты, генератор образцовой частоты, пер- .вый входной формирователь, два многоразрядных счетчика, процессор управления и индикации, первый и второй входы которого соединены соответственно с выходами первого и второго многоразрядных счетчков, а первый выход процессора управления и-индикации подключен к входам обнуления первого и второго многоразрядных счетчиков, введены второй

входной формирователь, второй, третий и четвертый делители частоты, пять расщепителей фаз последовательностей, коммутатор, две группы

5о-триггеров, элемент задержки, две группы элементов ИЛИ-НЕ, две группы двухразрядных двоичных счетчиков, два формирователя сигналов переноса, два комбинационных дешифратора,

0причем первые входы первого и второго входных формирователей подключены соответственно к первой и .второй входным шинам устройства, вторые входы первого и второго входных формирователей соединены соответственно с вторым и третьим выходами процессора управления и индикации,прямой и инверсный выходы первого входного формирователя соединены соответственно с входами первого и второго делителей частоты, прямой и инверсный выходы второго входного формирователя подключены соответственно к входам третьего и четвертого делителей частоты, выходы старших разрядов

5, первого, второго, третьего и четвертого делителей частоты соединены соответственно с первым, вторым,третьим и четвертым входами коммутатора, инверсные выходы младших разрядов 0 первого, второго, третьего и четвер ого делителей частоты подключены

соответственно через первый, второй, третий и четвертый расщепители фаз последовательностей соответственно

к пятому, шестому, седьмому и восьмому входам коммутатора, управляющий вход которого соединен с четвертым выходом процессора управления и л индикации,первая группа прямых и инверсных выходов коммутатора соединена с входами синхронизации соответственно первой и второй половины

первой группы Т) -триггеров,- вторая 5 группа прямых выходов коммутатора соединена с входами синхронизации первых половин второй грыппы Э-триггеров и первыми входами первой группы элементов ИЛИ-НЕ, вторая группа 0 инверсных выходов коммутатора соединена с входги ли синхронизации вторых половин второй группы D-триггеров и первыми входами первой группы элементов ИЛИ-НЕ, Т)-входы перЁой груп5 пы О-триггеров подключены к шине логической единицы, входы обнуления первой группы D-триггеров подключены к входам обнулениявторой группы J -триггеров и к пятому выходу процес сора управления и индикации, вход разрешения синхронизации первой груп пы Ъ-триггеров соединен с входами обнуления первой и второй групп двух раэрядных двоичных счетчиков и с пер вым выходом процессора управления и индикации, выходы первой группы D-триггеров, объединенные монтажным ИЛИ, подключены кD-входам второй группы D -триггеров и к входу элемен та задержки, выход которого подключен к входам разрешения синхрониэаций первой и второй групп двухразряд ных двоичных счетчиков, выход генера тора образцовой частоты соединен с входом пятого расщепителя фаз, прямы и инверсные выходы которого подключены к.первым входам соответственно первой и второй половины второй груп пы элементов ИЛИ-НЕ, входы разрешения синхронизации второй группы Т5 триггеров соединены с шестым выходом процессорна управления и индикации, выходы второй группы и-триггеров, объединенные монтажным ИЛИ, подключены к вторым входам первой и второй групп элементов ИЛИ-НЕ, выходы которых соединены со счетными входами соответственно первой и второй групп двухраэрядных. двоичных счетчиков, выходы которых подключены к информационным входам соответственно первого и второго комбинационных дешиф раторов, а также к входам соответственно первого и второго формирователей сигналов переноса, выход первого формирователя переноса соединен с входом коррекции первого комбинационного дешифратора и со счетным входом первого многоразрядного счетчика, выход второго формирователя переноса соединен с входом коррекции второго комбинационного дешифратора и со счетным входом второго многоразрядного счетчика, выходы пер вого и второго комбинационных дешифраторов подключены соответственно к третьему и четвертому входам процессора управления и индикации. Причем при г -разрядных делителях частоты первый, второй, третий и чет вертый расщепители фаз последователь ностей содержат по / -п- 1 счетных триггеров г - 1-ступенчатой структу ры, при этом количество триггеров 1-и ступени равно 2 -1, входы триг-ггеров I-и ступени подключены к пря1уим и инверсным выходс1М триггеров c-i-й ступени и к входу расщепителя фаз последовательностей, связанному с инверсным выходом 1 -го разряда делителя частоты, а выходы расщепителя фаз последовательностей.соединены с выходами триггеров последней Л - 1-й ступени. Пятый расщепитель фаз последовательностей содержит 2 - 1 последовательно соединенные элементы задержки, при этом вход первого эле мента задержки подключен к входу .расщепителя фаз последовательностей, выход предыдущего элемента задержки соединен с входом последующего элемента задержки, вход пятого расщепителя фаз последовательностей и выход каждого элемента задержки подключен к входу соответствующего им одного из буфера, прямые и инверсные выходы которого соединены с выходами расщепителя фаз последовательностей . Причем первый и второй комбинационные дешифраторы содержат комбинационный сумматор, элемент ИЛИ и логический корректирующий элемент, первый вход которого соединен с входом коррекции комбинационного дешифратора, информационные входы которого подключены к входам комбинационного сумматора и к вторым входам логического корректирукадего .элемента, выходы которого соединены с первыми входами элемента ИЛИ,вторые входы которого соединены с выходами старших разрядов комбинационного сумматора, выходы элемента ИЛИ и выходы младших разрядов комбинационного сумматора соединены с выходами соответственно старших и младших разрядов комбинационного дешифратора. При этом процессор управления и индикации содержит пульт задания режимов, управляющий автомат, блок индикации и арифметическое устройство, первый и второй входы операндов которого подключены соответственно к первому и второму входами процессора управления и индикации, управляючдай вход арифметического устройства соединен спервым выходом управляющего автомата, выходы признаков результата арифметического устррйства подключены к первым входам условий управляющего автомата, выходы результата арифметического устройства соединены с информационными входами блока индикации, управляю 1Д1й вход которого соединен с вторым выходом управляющего автомата, третий, четвертый, пятый и шестой выходы которого подключены соответственно к первому, четвертому, пятому и шестому выходам процессора управления и индикации, вторые входы условий управляющего автомата подключены к первым выходам пульта задания режимов, второй и третий выходы которого соединены соответственно с вторым и третьим входами процессора управления и индикации. На фиг. 1 приведена блок-схема цифрового частотомера; на фиг. 2 функциональные схеки вариантов реализации первого, второго, третьего 5 и четвертого расщепителей фаз пос лёдовательностей для случаев «л 2 (фиг. 2а)и П 3 Хфиг. 2S); на фиг.Зфункциональные схемы вариантов реализации пятого расщепителя фаз пос- 10 ледовательностей для случаев п 2 (фиг. За) и П 3 (фиг. 3S:}, на фиг. 4 - функциональная схема комбинационного дешифратора; на фиг. функциональная схема про- 15 цессора управления и индикации; на г. б - процесс расщепления-преобразования одной из исходных последовательностей uL или (J , или J5) , или ; на фиг. 7 - процесс расщеп- 20 Ленин фаз последовательностей для пятого расщепителя; на фиг, 8 - реализация функции коррекции f (в ; на фиг. 9 - временная диаграмма циклов измер,ения в режимах Частота - 25 Период ; на фиг. 10 - временная диаграмма циклов измерения в режиме Интервал ; на фиг. 11 - временная диаграмма циклов измерения в режимах Длительность импульса ; на фиг. 12- 30 временная диаграмма циклов измерения в режимах Непосредственный счет.

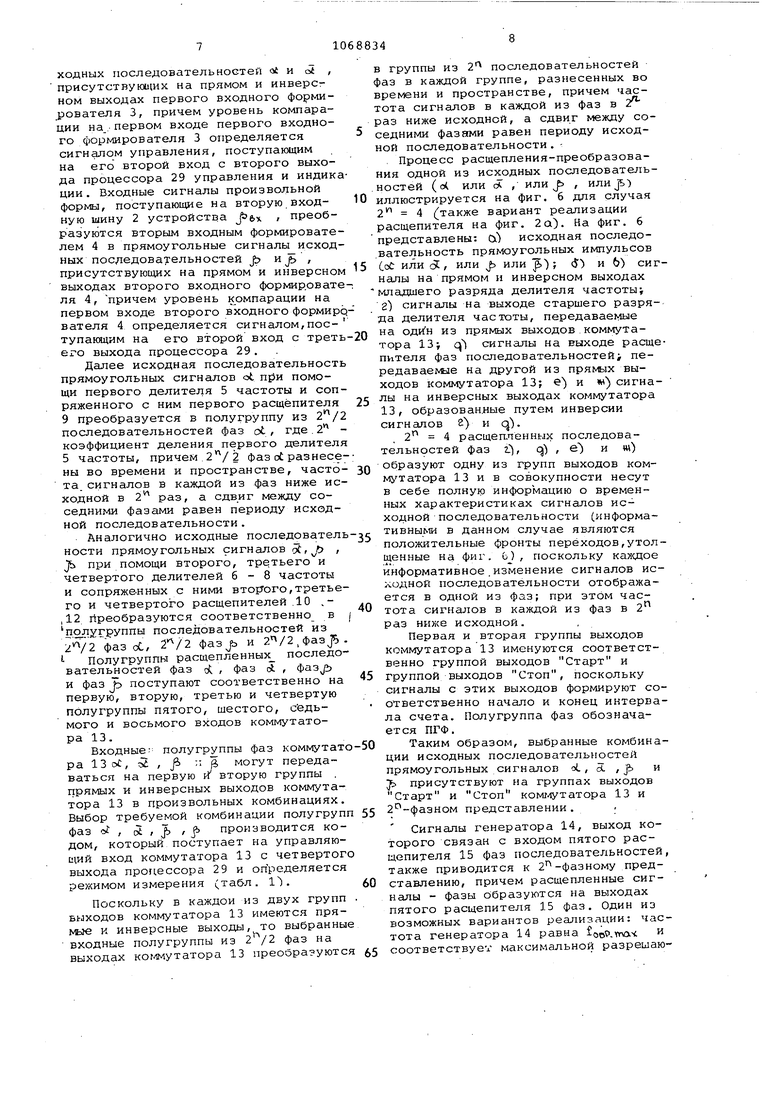

. Цифровой частотомер содержит первую и вторую входные шины 1 и 2, соединенные с первыми входами соот- з5 ветственно первого и второго входных форишрователей 3 и 4, прямой и инверсный выходы первого входного формирователя 3 соединены с входами соответственно первого и второго дели- л тел ей 5. и б час.тоты, прямой и инверсный выходы второго входного формирователя 4 соединены с входами соответственно третьего и четвертого

делителей 7 и .8 частоты, инверсные выходы младших разрядов первого,второго, третьего и четвертого делителей 5-8 частоты подключены соответственно через первый, второй, третий и четвертый расщепители 9 - 12 фаз последовательностей соответственно к 50 пятому, шестому, седьмому и восьмому входам коммутатора 13, первый, вто рой, третий и четвертый входы которого соединены с выходами старших разрядов первого,- второго, третьего 55 и четвертого делителей 5-8 частоты, генератор 14 образцовой частоты соединей с входом пятого расщепителя 15 фаз последовательностей, первая группа прямох и инверсных выходов комму- 60 татора 13-соединена с входами синхронизации первой группы 16 D-триггерров, вторая группа прямых и инверсых выходов коммутатора 13 соединена входами синхронизации первой груп- 65

пы 16 Х -триггеров,вторая группа пря;мых и инверсных выходов коммутатора ДЗ соединена с входами синхронизации второй группы 17 D -триггеров, вьЬсоды первой группы 16 D-триггеров подключены к входу элемента 18 задержки,а вторая группа прямых и инверсных выходов коммутатора 13 соединена с первыми входами первой группы 19 элементов ИЛИ-НЕ, первые входы второй группы 20 элементов;, ИЛИ-НЕ соединены с пря мыми и инверсньми выходами пятого расщепителя 15 фаз, счетные входы первой и второй групп 21 и 22 двухразрядных счетчиков соединены с выходами соответственно первой и второй групп 19 и 20 элементов ИЛИ-НЕ, входы первого и второго формирователей 23 и 24 сигналов переноса соединены с выходами соответственно первой и второй групп 21 и 22 двухразрядных двоичных счетчиков и с входами первого и второго комбинационных дешифраторов 25 и 26, входы перврго и второго многоразрядных счетчиков 27 и 28 соединены соответственно с выходами соответственно первого и второго формирователей 23 и 24 сигналов переноса, первый и второй входы процессора 29 управления и индикации соединены, с выходами соответственно первого и второго многоразрядных счетчиков. 27 и 28, а третий и четвертый входы процессора 29 соединены с выходами соответственно первого и второго комбинационных дешифраторов 25 и 26..

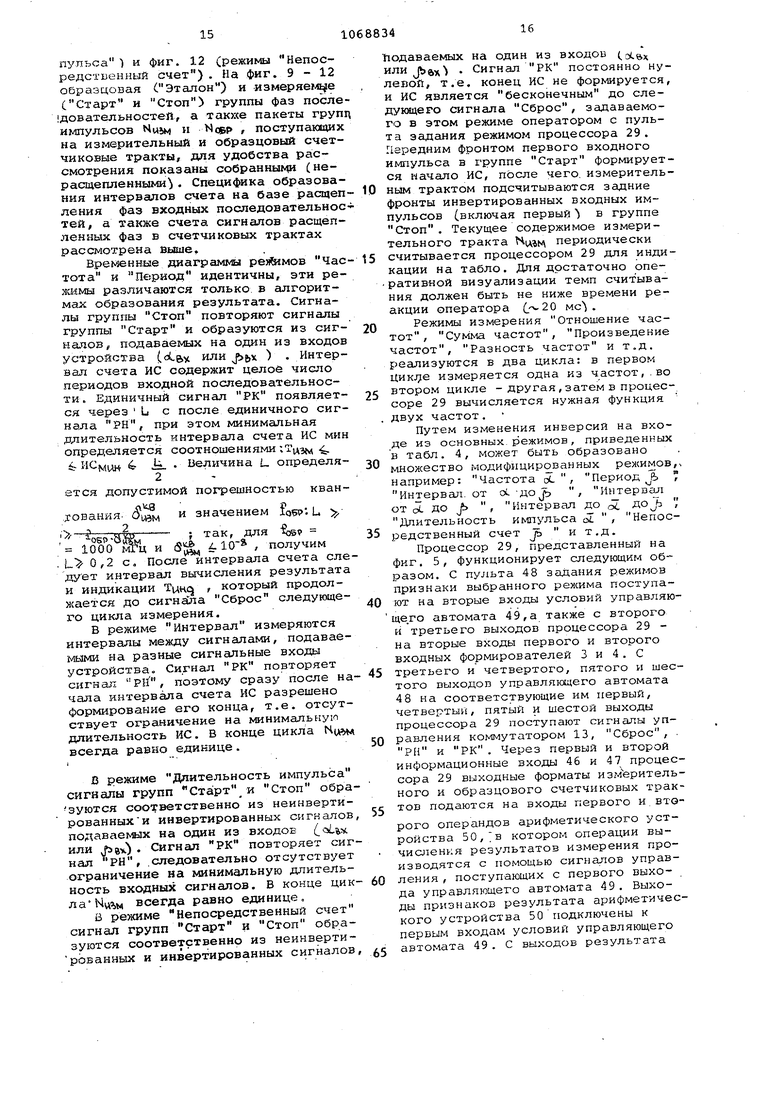

Первый, второй, третий и четвертый расщепители 9 - 12 содержат делитель 30 частоты, имеющий выход 31 старшего разряда делителя и инверсный выход 32 младшего разряда делителя, соединенный со счетным Триггером 33, а также выходаз 34 расщепителей (фиг. 2).

Пятый р.асщепитель 15 фаз содержит вход 35, элемент 36 задержки, буферы 37, выходы 38. ,

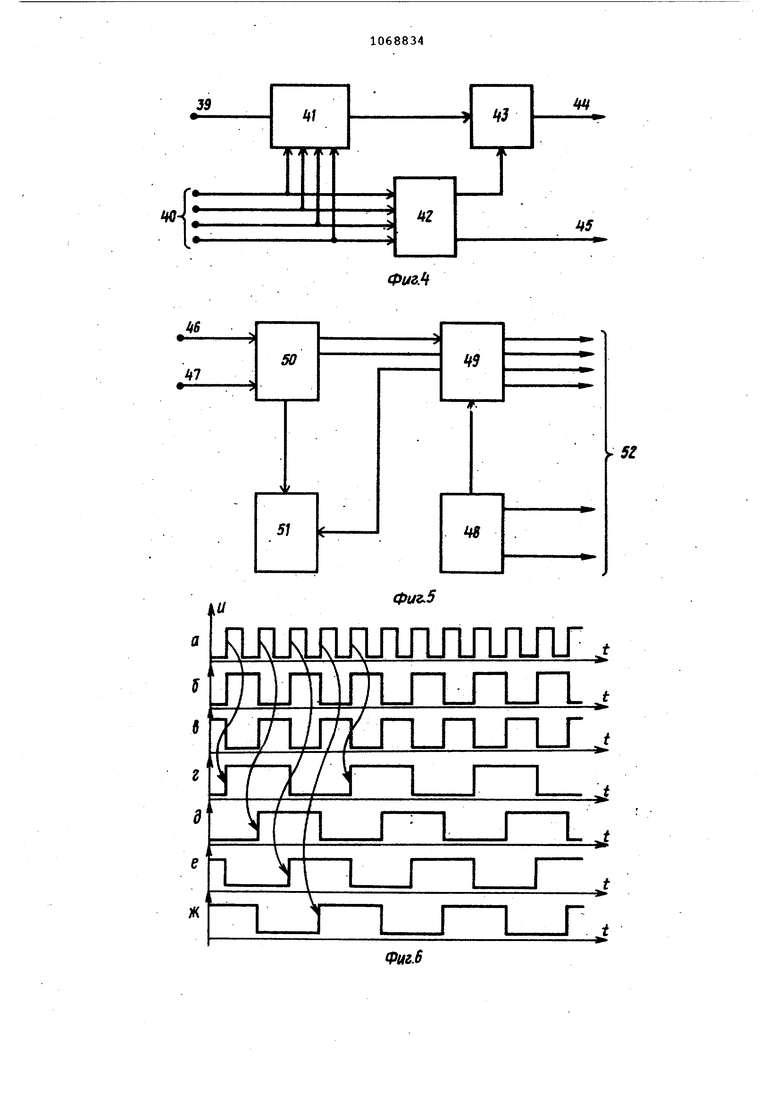

Первый и второй комбинационные дешифраторы 25 и 26 содержат;вход 39 коррекции, информационные входы 40, логический элемент 41 коррекции, комбинационный сумматор 42, элеменгпл ИЛИ 43, выходы 44 и 45 соответственно старших и шaдшиx разрядов.

Процессор 29 содержит первый и второй входы 46 и 47, пульт 48 задания режимов, управляющий автомат 49, арифметическое устройство 50, блок 51 .индикации, выходы 52. ,

Цифровой частотомер работает следующим образом.

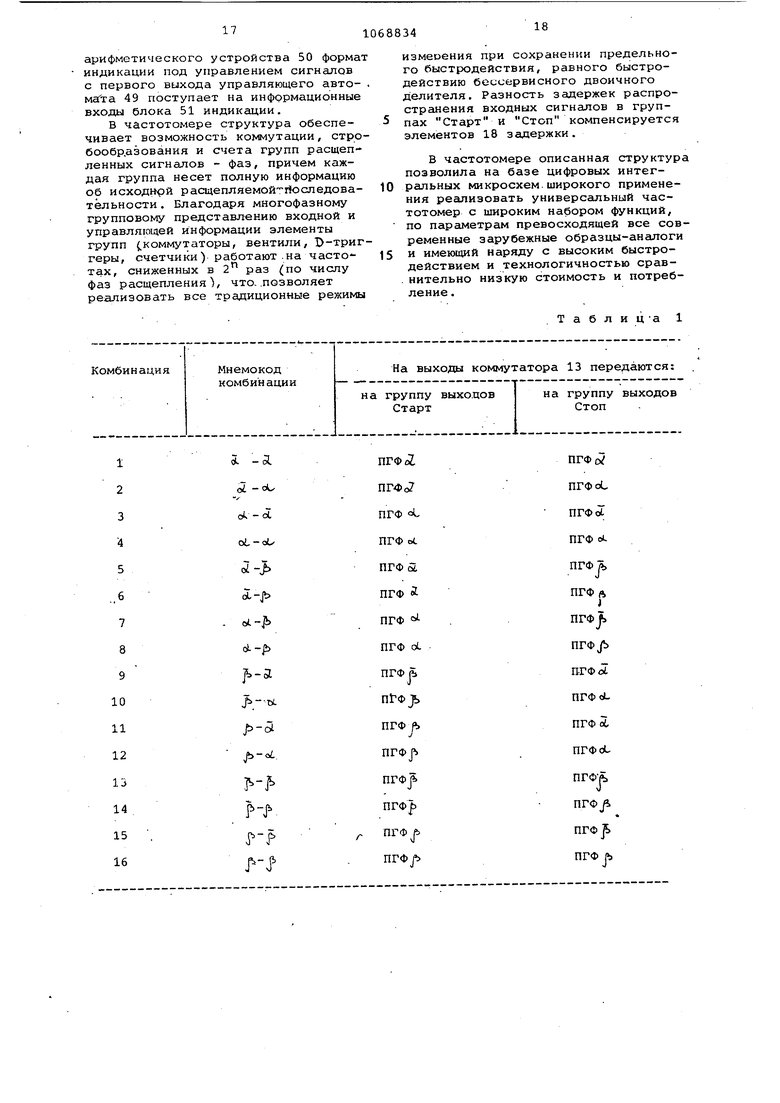

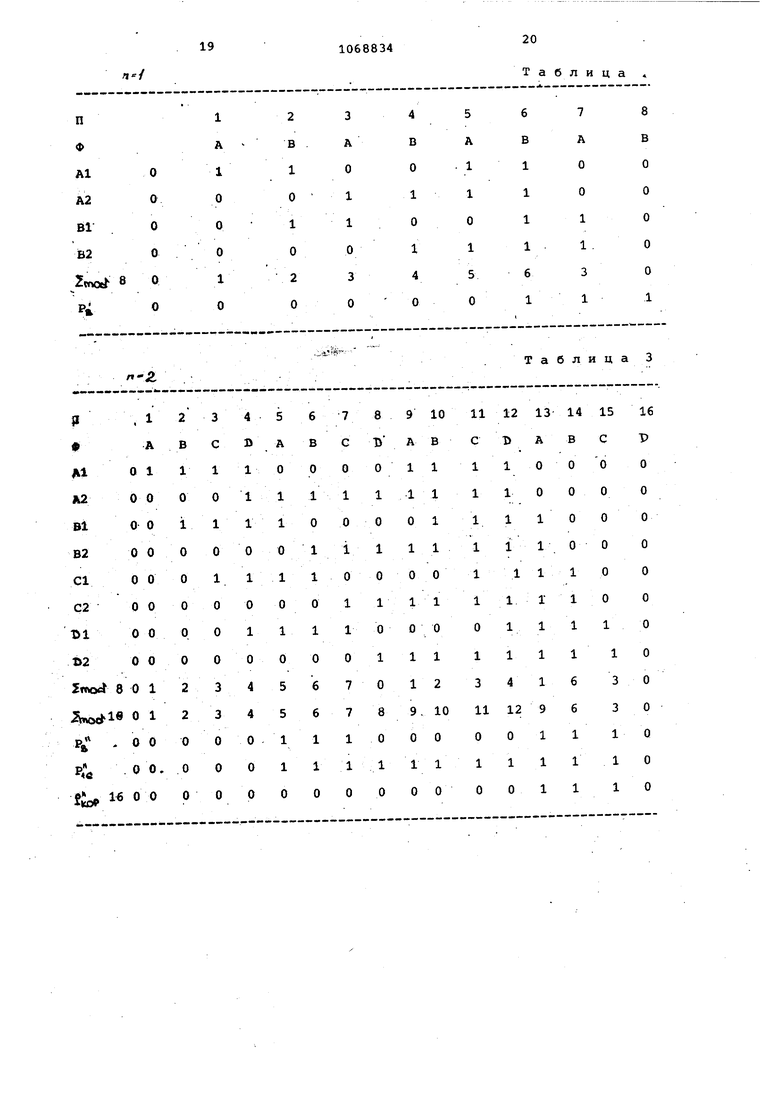

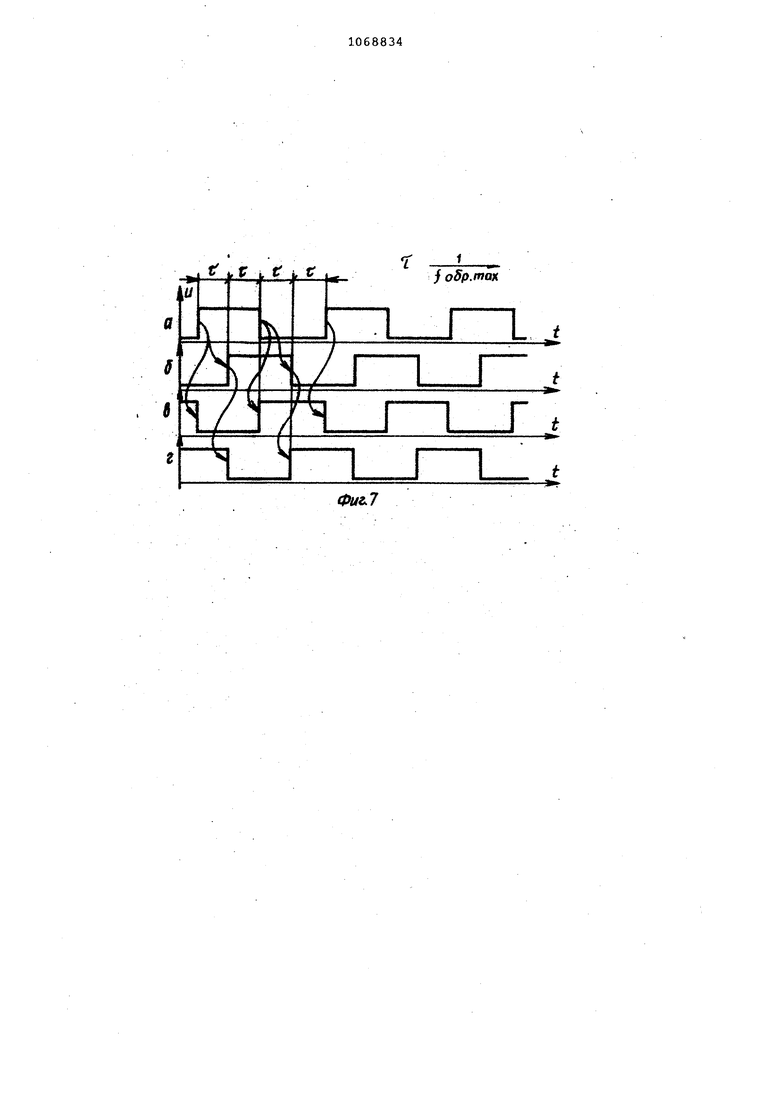

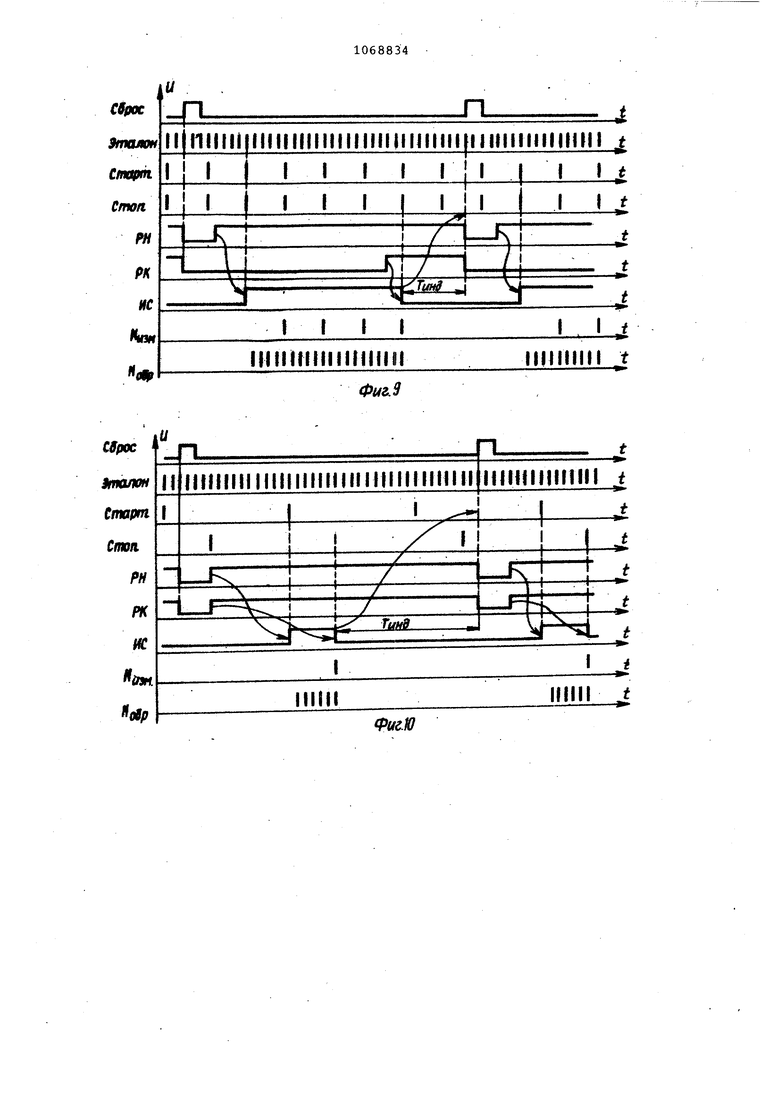

Входные сигналы произвольной формы, поступающие на первую входную шину 1 устройства / преобразуются первым входным формирователем 3 в -прямоугольные сигналы исходных последовательностей oi и ot , присутствующих на прямом и инверсг ном выходах первого входного формирователя 3, причем уровень компарации на , первом входе первого входного формирователя 3 определяется сигналом управления, поступающим на его второй вход с второго выхода процессора 29 управления и индик ции. Входные сигналы произвольной формы, поступающие на вторую входную шину 2 устройства jbj, , преобразуются вторым входным формирователем 4 в прямоугольные сигналы исходных последовательностей Jb , присутствующих на прямом и инверсном выходах второго входного формировате ля 4, причем уровень компарации на первом входе второго входного формир вателя 4 определяется сигналом,поступающим на его второй вход с треть его выхода процессора 29. Далее исходная последовательность прямоугольных сигналов ot П15и помощи первого делителя 5 частоты и соп ряженного с ним первого расщепителя 9 преобразуется в полугруппу из последовательностей фаз ot , где. 2 коэффициент деления первого делителя 5 частоты, причем фаз ot разнесе ны во времени и пространстве, частота, сигналов в каждой из фаз ниже исходной в 2 раз, а сдвиг между соседними фазами равен периоду исходной последовательности. Аналогично исходные последователь ности прямоугольных сигналов oi,J , Jb при помощи второго, третьего и четвертого делителей 6-8 частоты и сопряженных с ними второго,третьего и четвертого расщепителей .10 ,,12 йреобразуются соответственно в полугруппы последовательностей из оС, фaзJЬ и ,фазJ5 - Полугруппы расщепленных последовательностей фаз ct , фаз dt , и фаз Ъ поступают соответственно на первую, вторую, третью и четвертую полугруппы пятого, шестого, седьмого и восьмого входов коммутатора 13. Входные- полугруппы фаз коммутато ра 13оС, и , Ji п Э могут передаваться на первую rf вторую группы . прямых и инверсных выходов коммутатора 13 в произвольных комбинациях. Выбор требуемой комбинации полугруп фаз , ot / J / jb производится кодом, который поступает на управляющий вход коммутатора 13 с четвертог выхода процессора 29 и определяется режимом измерения (табл. 1. Поскольку в каждой из двух групп выходов коммутатора 13 имеются прямые и инверсные выходы, то выбранные входные полугруппы из фаз на выходах когмутатора 13 преобразуютс в группы из 2 последовательностей фаз в каждой группе, разнесенных во времени и пространстве, причем частота сигналов в каждой из фаз в 2 раз ниже исходной, а сдвиг между соседними фазами равен периоду исходной последовательности. Процесс расщепления-преобразования одной из исходных последовательностей (о или (J , или , ) иллюстрируется на фиг. 6 для случая 2 4 (также вариант реализации расщепителя на фиг. 2а). На фиг. 6 представлены: Сх) исходная последовательность прямоугольных импульсов Cot или cJ, или или J,); (5) и 6) сигналы на прямом и инверсном выходах младшего разряда делителя частоты 2) сигналы на выходе старшего разряда делителя частоты, передаваемые на один из прямых выходов коммутатора 13; а( сигналы на выходе расщеп tтeля фаз последовательностей передавае ые на другой из прямых выходов коммутатора 13; е) и ) сигналы на инверсных выходах коммутатора 13, образованные путем инверсии сигналов 2) и q). . 2 4 расщепленных последовательностей фаз 2.), с , &) и w) образуют одну из групп выходов коммутатора 13 и в совокупности несут в себе полную информацию о временных характеристиках сигналов исходной последовательности (информативными в данном случае являются положительные фронты переходов,утолщенные на фиг. G), поскольку калуцое информативное изменение сигналов исходной последовательности отображается в одной из фаз; при этом частота сигналов в каждой из фаз в 2 раз ниже исходной. Первая и вторая группы выходов коммутатора 13 именуются соответственно группой выходов Старт и группой выходов Стоп, поскольку сигналы с этих выходов формируют соответственно начало и конец интервала счета. Полугруппа фаз обозначается ПГФ. Таким образом, выбранные комбинации исходных последовательностей прямоугольных сигналов Ы., 5. , ji и J присутствуют на группах выходов Старт и Стоп комг татора 13 и 2- -фазном представлении . Сигналы генератора 14, выход которого связан с входом пятого расцепителя 15 фаз последовательностей, также приводится к 2 -фазному представлению, причем расщепленные сигвалы - фазы образуются на выходах пятого расщепителя 15 фаз. Один из возможных вариантов реализации: частота генератора 14 равна foeP.rwx и соответствует максимальной разрешающей способности tp 1 .лпа. частотомера, при этом пятый расщепи тель 15 может быть образован, напри мер, объединением делителя частоты, подобного первому делителю 5 частоты расщепителем, подобным первому расщепителю 9, и с дополнительными выходными инверторами. Пятый расщепитель 15 поедетавлен функциональными схемами на фиг. 3. При этом Частота генератора 14 выбирается равной ° (т.е. равна частоте каждой из выходных фа а расщепдение фаз производится путем задержек и .инверсий исходных сигналов генератора 14, что проиллюстрировано, для случая2 4 фаз диаграммами на фиг. 7, где: а) фаза, идентичная исходному сигналумеандру генератора , образованная путем задержки исходного сигнала-меандра на время t g-; ) фаза, инверсная фазе а); г) Фаза, инверсная фазе () . В предлагаемом частотомере имеют ся два идентичных счетчиковых тракта - измерительный и образцовый. Из мерительный тракт включает в себя первую группу элементов ИЛИ-НЕ 19, первую группу двухразрядных двоичны счетчиков 21, первьай формирователь 23 сигналов переноса/ первый комбинационный дешифратор 25, первый мно горазряднйй счетчик 27. Образцовый тракт содержит вторую группу элемен тов ИЛИ-НЕ 20, вторую группу двухразрядных двоичных счетчиков22, второй формирователь 24 сигналов пе ренрса, второй комбинационный дешиф ратор 26, второй многоразрядный счетчик 28. Каждый из счетчиковых трактов имеет по 2 параллельньлх счетных входов, (по числу расщепленных фаз) и подсчитывает сумму поступивших н его входы импульсов в 2 рас.щеплен ных фазовых последовательностях. Подсчитанная сумма подается с выходо тракта на информационные входы процессора 29 в позиционном коде. Рассмотрим функционирование счет чиковых трактов. В каждом из них имеется по два счетчика: 2 -вхо.довой параллельный счетчик с позиционным представлением младших разрядов тракта, включающий группу дву разрядных двоичных счетчиков, форми рователь сигналов переноса, комбина ционный дешифратор; последовательный многоразрядный счетчик старших разрядов тракта. . Основой 2 -входового параллельн го счетчика служит группа из 2 дву разрядных двоичных счетчиков, кажды из которых производит счет по модул поступающих на его счетный вход сигналов одной из 2 фаз. При произвольном, но. повторяющемся на интервале счета порядке следования расепленных фаз, состояния триггеров группы повторяются с периодом повторения в 4 2 2 входных сигналов. На базе такой группы из 2 двухразрядных двоичных счетчиков построен счетчик входных сигналов по модулю 2 (или 2 V , в котором выделяется сигнал переноса по переполнению и позиционный код состояния по выбранному модулю ( или . Рассмотрим дляслучаев 1Г 1 (расщепление на 2 фазы) реализацию счетчика по модулю 2 В табл. 2) . Рассмотрим для случая ГУ 2 (расщепление на 4 фазы) реализацию счетчиков по модулю 2 8. и по модулю 2 16 (табл. 3). Начальные состояния всех триггеров - нулевые Г В табл. 2 и 3 в верхней строке П приведены номера сигналов исходной последовательности, каждому из которых по столбцу соответствует содержание остальных строк, где: Ф фаза, к которой отнесен данный сигнал исходной последовательности (А, В, С и ТЭ) ; А1, В1, С1 и D1 состояйия младших разрядов двухразрядных двоичных счетчиков сигналов соответствукядах фаз (вес младшего разряда - 1) ; Л2, В2, С2 и состояния старших разрядов/двухразрядньох двоичных счетчиков сигналов соответствующих фаз (вес старшего разряда - 2) f Ztr)oJ;&, Lv-noQhAS Nsa no модулю 8 и по модулю 16 содержимого всех разрядов группы двухразрядных двоичных счетчиков. О сигналах р ; р ; р будет сказано далее. Как видно из табл. 2 и 3, сигналы переноса по переполнению в явном виде в состояниях разрядов не видны, а попытка вьщелить требуемый позиционный код путем суммирования содержимого всех разрядов групп двухразрядных двоичных счетчиков оказывается удачной, за исключением следующих аномалий, отмеченных в табл.2 и 3 кружками: в таСл. 2 вместо числа 7 суммирование дает число 3 или в двоичном коде 011 вместо 11,1, т.е. требуется коррекция в разряде с.весом 4 (нужна 1 вместо О) в табл. 3 для счетчика по модулю 8 вместо 5 и 7 суммирование дает соответственно 1 и 3 или в двоичном коде flOl вместо 101, 011 вместо 111, т.е. требуется коррекция в разряде с весом 4 (нужна 1 вместо 0) ; в табл. 3 для счетчика по модулю 16 вместо 13, 14 и 15 суммирование дает 9 , 6 и 3 или в двоичном коде igOl вместо 1101, QUO вместо 1110 QOll вместо 1111, т.е. требуется коррекция в разрядах с весом 4 и 8 {нужна 1 вместо О) . Первый и ВТОРОЙ формирователи 23 и 24 сигналов переноса, в частности, могут бытб реализованы путем следукддах логических преобразований для случая , Р Ад АИ. V В В2; дпя случая rv Q - pj, %- Ь. 2г. t)2. V A-i 84- GI Т5 , для случая г 2rnod 16 - Р A vB-tVO vD :, Сигналы переноса pjj ; р и р реализованные по предлагаемым форм лам, отображены в нижних строках табл. 2 и 3, а соответствующие фор мирователи сигналов переноса функционально представлены на фиг. 8. Для рассматриваемых случаев ( 1 и п 2 вариант реализации первого и второго комбинационных дешифратрров 25 и 26, представленный на фиг. 4 имеет интерпретацию. Сигналы переноса Р от формировател сигналов переноса через вход коррекции 39 подаются на первый вход логического элемента 41 коррекции. Сигналы состояний разрядов групп двухразрядных двоичных счетчиков че рез информационные входы 40 поступа ют в общем случае на входы комбинационного «Ьумматора 42 и «а вторые входы логического элемента 41 коррекции. На выходе элемента 41 обра зуется исполнительный сигнал коррек ции / поступающий на вторые вхо ды элементов ИЛИ 43, Сигналы выходо младших разрядо.в комбинационного су матора 42 2||дд- поступают непосредственно на выходы 45. Сигналы выходов старших разрядов комбинацнонного сумматора 42 .подаются на ne вые входы элементов ИЛИ 43, с выходов которых скорректированные сигна лы старишх разрядов поступаю на выходы 44. Для рассмотренных слу чаев могут быть предложены следующие соотношения: ДЛЯ случая п 1, nvxr 8, г 2 Scr4Vfe-SCT4VP4 коррекдия старшего разряда с весом 4) } для случая п 2, «Yvoci8, (,|р f .,,,.2.,,vPe ,,рр,, ция старшего разряда с весом 4); для случая П 2, rood i и , (A -A2VbietVC,CzVl,DiV. функция коррекции корлв представлена в табл. 3, а ее реагшзация - на фиг. 8;, Vf 5 ч/ . icT8-- eTeVl«o « (коррек- . ция Старших разрядов с весгъми 4 и 8 . Для случаев П 1, IYXJ 8 и п 2 , lYOdJ 8 исполнительный сигнал коррекции тождественен сигналу переноса, в этих случаях логический элемент 14 выро:з дается в транслятор сигнала Во вйех приведенных формулах образования сигналов переносов и сумм функции преобразования симметричны относительно одноименных разрядов различных двухразрядных двоичных/ счетчиков группы. Это говорит о том, что результаты преобразования будут верными независимо от начальной привязки фаз сигналов входной последовательности; так в табл. 2 вместо привязки 1-А, 2-В, 3-А, 4-В,... допустима привязка 1-В, 2-А. 3-В, 4-А в табл. 4 вместо привязки 1-А, 2-В, 3-е, 4-11, 5-D, ... допустимы другие начальные привязки фаз 1-В, 2-С, 3-D, 4-А, 5-В,... или 1-е, 2-t , 3-А, 4-В, 5-С,... или l-D, 2-А, 3-В, 4-С, Б-и,... Выходы первого или второго комбинационных дешифраторов 25 и 26 представляют младшие разряды.тракта, а вйходы первого или второго многоразрядного счетчика 27 и 28 - старшие разряды .тракта. Совместно младшие и старшие разряды тракта образуют формат, в котором в позиционном коде представлена сумма импульсов фаз, поступающих после обнуления на входы тракта. Формат поступает на информационные входы процессора 29 . Счетчики измерительного тракта на интервале счета подсчитывают количество импульсов в 2 фазовых последовательное.тях группы Стоп, поступаКЩИх на первые входы первой группы элементов ИЛИ-НЕ 19 (счетные входы измерительного тракта) со второй группы выходов коммутатора 13 (группы выходов Стоп) . Счетчики образцового тракта на интервале счета подсчитывшот количество импульсов в 2 фазовых последовательностях группы Эталон, поступающих на первые входы второй группы элементов ИЛИ-НЕ 20 (счетные входы образцового тракта) с выхода пятого расщепителя 15. Интервал счета (ИС) является об--щим для обоих счетчиковых трактов и образуется как функция состояний первой и второй групп 16 и 17 триггеровU(l-(T -4vTV vTVi T.) X .YT2.3 vT.,, - vT,-vT, где Тд - состояния выходов первой группы 16 D-триггеров; - состояния выходов второй I у группы 17 1 -триггеров J . if - дизъюнкция состояния вы, V .j,v t ходов первой группы 16 . D-триггеров; уТг- Ъ-1 Тг-гУ- дизъюнкция состояний выvTj-svTz/i ходов второй группы 17 В-триггеров. Интервал счета существует в то время, когда все JD -триггеры второй группы ,17 находятся в нулевых Состояниях и хотя бы один изВ-триггеров первой группы 16 находится в единичном состоянии. Сигналы дизъюн кции VT(L и УФ2.-1 образуются путем монтахшого объединения (монтажного ИЛИ) выходов D -триггеров в каждой из групп. Функционально первая и вторая группы 16 и 17 В-триггеров служат для формирования соответственно начала и конца интервала счета ИС. После предварительного обнуления ТЭ-триггеров обоих групп: , Q и 0; ИС V Т.. f- , О-б Ol 0. Далее переход в единичное состояние хотя бы одного из триггеров первой группы 16 формирует начало ИС: , 1 и VT,i.L 0; ИС 1-0 1-1 1. Дсшее переход в единичное состояние хотя бы одного из D-триггеро второй группы 17 формирует конец ИС; УТд: 1 и vTi-i. Ij ИС 1-1 IO 0. Выходной си гнал VT,-i, первой группы 16 О-триггеров разрешает ин терпал счета ИС единичным уровнем, поступающим через элемент 18 згщерж ки на входы разрешения счета ,(Срвходы) первой и второй групп 21 тл 22 двухразрядных двоичных счетчиков Выходной сигнал V Т2 вт.орой группы 17 D -триггеров разрешает ин тервал счета нулевым уровнем, посту пающим на вторые входы первой и вто рой групп 19 и 20 элементов ИЛИ-НЕ При единичном уровне , сигнал групп Стоп и Эталон, подаваемые на первые входы первой и второй гру 19 и 20 элементов ИЛИ-НЕ (.на счетны входы измерительного и эталонного трактов) блокируются и не поступают на С-входы первой и второй групп 21 V. 22 двухразрядных двоичных счетчиков. Перед началом цикла измерения си .пал, поступающий с второго выхода процессора 29 на -входы обеих груп р-триггеров и счетчиков обоих трак TOD, обнуляет все й-триггеры и счет чики . В единичное состояние О-триггеры первой группы 16 при наличии услови; перехода переводятся ближайшими из сигналов фаз группы Старт, поступающих с первой группы выходов коммутатора 13 на входы первой группы 16 )-триггеров. Поскольку на Т)-входы D-триггеров первой группы 16 постоянно подан уровень логической единицы, то условием перехода служит единич- Ный сигнал РН (разрешение начала) в начале цикла измерения с третьего выхода процессора 29 на входы разрешения синхронизации (Ср-входы) пер-г вой группы 16 Ъ-триггербв. В единичное состояние Ь-триггеры.. второй группы 17 при наличии ус-., ловий перехода переводятся ближайшими из сигналов фаз группы Стоп , поступающих с второй группы выходов коммутатора 13 на входы (С-входы) второй группы 17 15-триггеров. Условиями перехода служат: единичный сигнад подаваемый с выходов первой группы 16 Ъ-триггеров на 0-входы второй группы 17 I)-триггеров и говорящий о том, что интервал счета ИС начат; и единичный сигнал РК (разрешение конца), поступающий с четвертого выхода процессора 29 на входы разрешения синхронизации второй группы 17 И-лгриггеров. Таким образом, интервал счета ИС начинается после появления единичного сигнала РН по ближайшему сигналу из фаз группы Ст&рт и заканчивается после появления единичного сигнала РК по ближайшему- сигналу из фаз группы Стоп. Сигнал РН во всех режимах измерения появляется в начале цикла непосредственно после сигнала обнуления Сброс . Тип режима измерения определяется тремя признаками: вариантом коммутации полугрупп расщепленных пЬследовательностей - фаз oi, ct. , jb, и на выходы групп сигналов, Старт и Стоп коммутатора 13 Стабл. 1)} моментам появлениясигнала РК относительно сигнала алгорктмом образования в продессоре результата измерения М из оценок NWJ и ЫОБР накопленных в измерительном и образцовом счетчиковых трактах,и значения частоты foso суммарной образцовой последовательности, образованной из суммы сигналов фаз группы Эталон. Основные режимы измерения и характеризукядае их признаки представлены в табл. 4. Временные диаграммы циклов измерения в основных режимах приведены на фиг. 9 (режимы Частота.- Период , фиг. 10 (режимы Интервал , фиг. lij(режимы Длительность импульса Ч и фиг. 12 (режимы Непосредственный счет) , На фиг. 9-12 образцовая (Эталон) и -HSMepHefJuje С Старт и Стоп) группы фаз после довательностел, а также пакеты груп импульсов NWJM и МОБР , поступающих на измерительный и образцовый счетчиковые тракты, для удобства рассмотрения показаны собранными (нерасщепленными . Специфика образова ния интервалов счета на базе расщеп ления фаз входных последовательнос тей, а также счета сигналов расщепленных фаз в счетчиковых трактах рассмотрена выше. Временные диаграм реи&1мов Час тот а и идентичны, эти релсимы различаются только в алгоритмах образования результата. Сигналы группы Стоп повторяют сигналы группы Старт и образуются из сигналов, подаваемых на один из входов устройства ( или ,)t ) . Интервал счета ИС содержит целоб число периодов входной последовательности. Единичный сигнал РК появляется через L с после единичного сиг- нала РН, при этом минимальная длительность интервала счета ИС мин определяется соотношениями . -4 is, Величина L определяется допустимой погрешностью квани значением foSP. L 5, тования .-- , так, для tost онр-йЖ, S /, 10 , получим 1000 МГЦ и 1 0,2 с. После интервал а счета сле дует интервал вычисления результата и индикации t который продолжается до сигнала Сброс следующего цикла измерения. В режиме Интервал измеряются интервалы между сигналами, подаваемыми на разные сигнальные входы устройства. Сигнал РК повторяет сигнал , поэтому сразу после на чала интервала счета ИС разрешено формирование его конца, т.е. отсутствует ограничение на минимальную длительность ИС. В конце цикла 1Ч(д всегда равно единице. В режиме Длительность импульса сигналы групп Старт и Стоп обра эуются соответственно из неинвертированных и инвертированных сигнгшов подаваемых на один из входов . или .fsBiO . Сигнал РК повторяет сиг нал РН, .следовательно отсутствует ограничение на минимальную длительность входных сигналов. В конце цик лаН«9,м всегда равно единице. в режиме Непосредственный счет сигнал групп Старт и Стоп образуются соответственно из неинвертированиых и инвертированных сигналов Тюдаваемых на один из входов (,э1.&х или Jbftx Сигнал РК постоянно нулевой, т.е. конец ИС не формируется, и ИС является бесконечным до следующего сигнала Сброс, задаваемого в этом режиме оператором с пульта задания режимом процессора 29. Передним фронтом первого входного импульса в группе Старт формируется начало ИС, после чего, измерительным трактом подсчитываются задние фронты инвертированных входных импульсов (включая первый в группе Стоп. Текущее содержимое измерительного тракта периодически считывается процессором 29 для индикации на табло. Для достаточно рперативной визуализации темп считывания должен быть не ниже времени реакции оператора ( мс . Режимы измерения Отношение частот, СуМма частот, Произведение частот, Разность частот и т.д. реализуются в два цикла: в первом цикJ7e измеряется одна из частот,, во втором цикле - другая,затем в процессоре 29 вычисляется нужная функция двух частот. Путем изменения инверсий на входе из основных.режимов, приведенных в табл. 4, может быть образовано множество модифициро ванных рех(,ч например: Частота 5. , Период ft, Интервш:. от оС До Ъ , Интервал от (5. до Jb , Интервал до , Длительность импульса ы , Непосредственный счет jb и т.д. Процессор 29, представленный на фиг. 5, функционирует следующим образом. С пульта 48 задания режимов признаки выбранного режима поступают на вторые входы условий управляюще го автомата 49,а также с второго и третьего выходов процессора 29 на вторые входы первого и второго входных формирователей 3 и 4. С третьего и четвертого, пятого и шестого выходов управляющего автомата 48 на соответствующие им первый, четвертый, пятый и шестой выходы процессора 29 поступают сигнала управления коммутатором 13, Сброс, . РН и РК. Через первый и второй информационные входы 46 и 47 процессора 29 выходные форматы измерительного и образцового счетчиковых трактов подаются на входы первого и.второго операндов арифметического устройства 50,в котором операции вычисления результатов измерения производятся с помощью сигналов управления , поступающих с первого выхода управляющего автомата 49. Выходы признаков результата арифметического устройства 50подключены к первым входам условий управляющего автомата 49. С выходов результата

арифметического устройства 50 формат индикации под управлением сигналов с первого выхода управляющего автомата 49 поступает на информационные входы блока 51 индикации.

В частотомере структура обеспечивает возможность коммутации, стробообр.азования и счета групп расщепленных сигналов - фаз, причем каждая группа несет полную информацию об исходнрй расцепляемой йоследоватёльности. Благодаря многофазному групповому представлению входной и управляющей информации элементы групп (.коммутаторы, вентили, D-TPHI- геры, счетчики) работают.на частотах, сниженных в 2 раз (по числу фаз расщепления V что. .позволяет реализовать все традиционные режимы

i -а

5

- ok -d

oL-oU

- oL-jb ot-Jb d-Jb

jb-3 -K

-ы

Jb-oL.

- p-J. -

r

измерения при сохранении предельного быстродействия, равного быстродействию бессервисного двоичного делителя. Разность задержек распространения входных сигналов в группах Старт и Стоп компенсируется элементов 18 задержки.

В частотомере описанная структура позволила на базе цифровых интегральных микросхем.широкого применения реализовать универсальный частотомер с широким набором функций, по параметрам превосходящей все современные зарубежные образцы-аналоги и имеющий наряду с высоким быстродействием и технологичностью срав. нительно низкую стоимость и потребление .

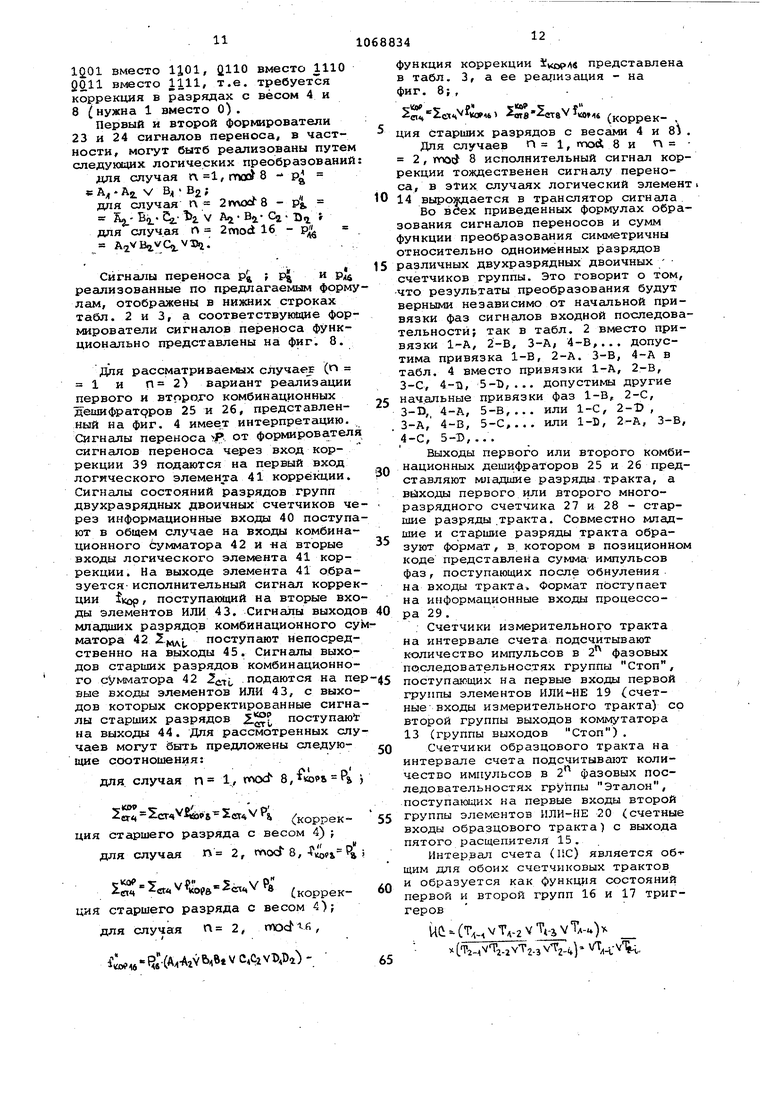

.Таблиц-а 1

пгф(2.

пгФсх;

ПГ4)о7

ПГФоС ПГФ of ПГФ oL ПГФ01. ПГФ oC ПГФ ПГФй ПГФ i ПГФ ft

ПГФ. ПГФ ПГФJЬ ПГФ oL ПГФоГ ПГФ S

J

ПtФjЬ ПГФоЬ ПГФЫ, ПГФ fe ПГФоС

пгФр ПГф-ft,

о

ПГФ

ПГФр

ПГФ

nrOJb ПГФ (Ъ 191068834 .

ц а 20 Т а б л и

Непосредственный- счет 3. ПГФ о«- ПГФ

J

ПГФ1

ПГФ

Таблица 4

NuiM

РК не появляМется

РК не появляМется

Г

30

JJ

we.2

35

F

37

hi

37

Фиг.З

39

Ц

J t 1 rj I J (

W1(6

50

41

51

iU

РШДЛПШШЯГ

Я

Kl

ЧЧ

J

Л

4Z

45

ФигМ

-« - -

48

Фиг.5

еЧг t С . i

Фиг.7

Фиъ.8

Cffpoe

imofiM Старт

Стл РН РК

т

Озл.

Нар

Фиъ.3

Сдрос Зталон

Старт Стоп.

Сброс

Спкцип

Стоп

РН

П

ФигЛ

ии-LJ

НС

азн

ЛL

LJL

(Риг.12

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Швецкий Б.И | |||

| Электронные измерительные приборы с цифровым отсчетом | |||

| Киев, Техника, 1964, с | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ электролитического выделения иода из растворов | 1925 |

|

SU5305A1 |

Авторы

Даты

1984-01-23—Публикация

1981-08-20—Подача