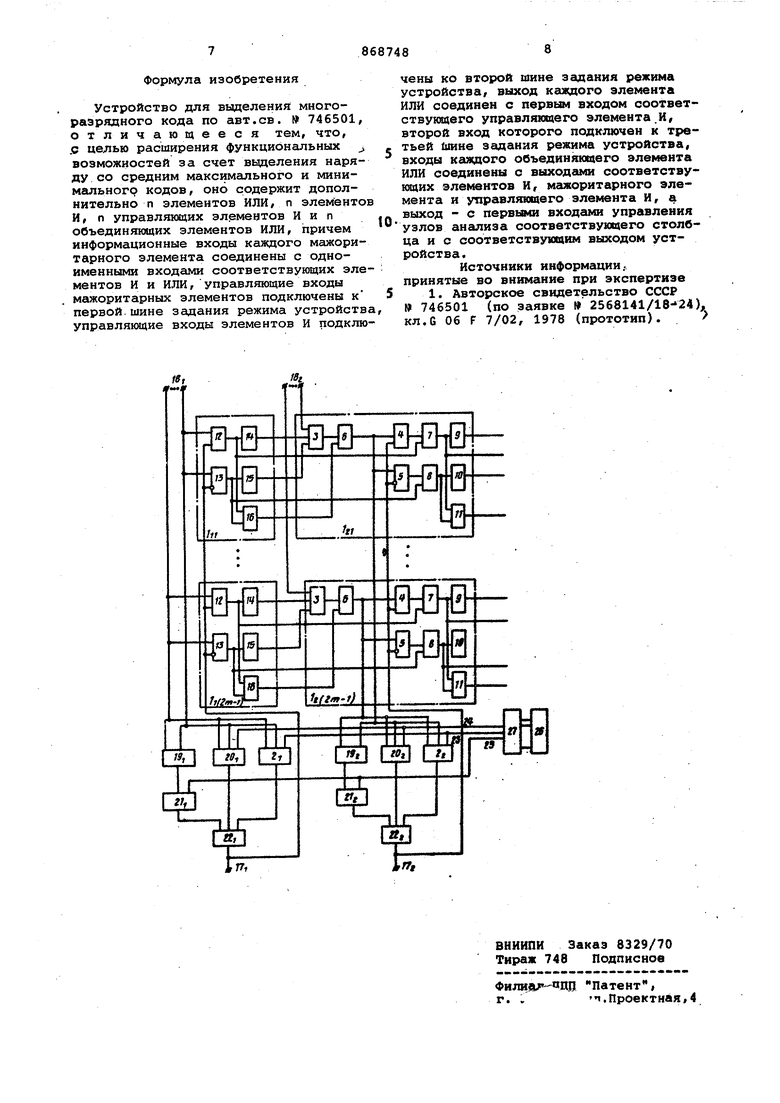

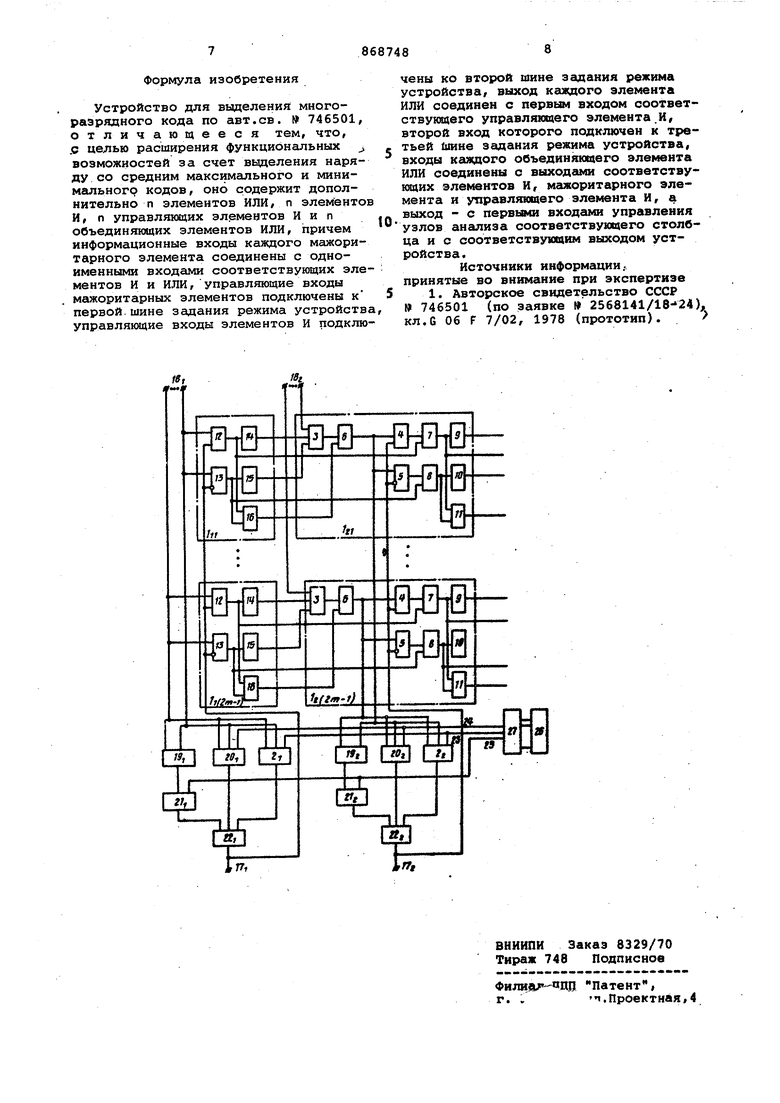

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при создании цифровых систем переработки информации По основному авт.св. 746501 известно устройство для вьщеления многоразрядного кода, содержащее nx(2m-l) узлов анализа мажоритарных элементов, причем информационный вход каждого (ixj)-oro узла анализа соединен с j-ым входом i-ой группы входов устройства, где i 1,2,...п j 1,2,.,,{2m-l), выход i-oro мажоритарного элемента подключен к первому входу управления (ixl), (1x2), Г|х(2т-1)-ого узлов анализа, первый второй, третий, четвертый и пятый вы ходы каждого (Ixj)-oro узла анализа соединены со вторым, третьим, четвер тым, ПЯТЫМ..И шестым входами управле ния lH-1)xj-oro узла анализа, выход результата узла анализа подключен к j-ому входу 1-ого мажоритарного элемента, при згтом Кс1ждый их)-ый узел анализа, где i 2, 3,...n;j 1,2.. . .(2m-1), содержит элементы И, ИЛИ НЕ, элемент неравнозначности, элемент запрета, приче первый вход первого элемента И соед нен с информационным входом узла, выход первого элемента И подключен к первому входу первого элемента ИЛИ, выход которого соединен с первыми . входами элемента неравнозначности и элемента запрета и с выходом, результата узла анализа, выходы элемента неравнозначности и элемента запрета подключены к первым входам второго и третьего элементов ИЛИ соответственно-, второй и третий входы первого элемента И соединены со вторым и четвертым входами управления узла анализа, второй вход элемента неравнозначности и второй вход элемента запрета подключены к первой шине управления узла анализа, второй вход второго элемента ИЛИ соединен с третьим входом управления узла анализа, вторые входы первого и третьего элементов ИЛИ подключены к шестому и пятому входам управления узла анализа соот-. ветственно, выход элемента ИЛИ соединен с первым входом второго элемента И, со вторым выходом узла анализа и через первый элемент НЕ с первым выходом узла анализа выход третьего элемента ИЛИ подключен ко второму входу второго элемента И, к четвертому выходу узла ангшиэа и через второй элемент НЕ - к третьему входу узла анализа, выход второго элемента И соединен с пятым выходом узла анализа, а каждый (1xj)-ый. узел анализа, где j 1,2, ...(2m-1) , содержит элемент неравнозначности, эле мент запрета, элементы И,НЕ, причем первые входы элемента неравнозначнор -ти и элемента запрета соединены с информационным входом узла анализа, вторые входы элемента неравнозначности и элемента запрета подключены к первому входу управления, выход элемента неравнозначности соединён с первым входом элемента И, со вторым выходом узла анализа и через пер вый элемент НЕ - -с первым выходом узла анализа,выход элемента запрета подключен ко второму входу элемента И, к четвертому выходу узла анализа и через второй элемент НЕ - к третьему выходу узла ансшиза, выход элемента И соединен с пятым выходом узла анализа. Это устройство позволяет формировать на выходе код среднего значения совокупности входных кодов l. Недостатком указанного устройства является невозможность выделения наряду со средним минимального и макси мального кодов. Цель изобретения - расширение функциональных возможностей за счет выделения наряду со средним максимального и минимального кодов. Поставленная цель достигается тем, что устройство для вьщеления многоразрядного кода содержит дополнительно п элементов ИЛИ, п элементов И п управляющих элементов И п объединяющих элементов ИЛИ, причем информационные входы каждого мажоритарного элемента соединены с одноименными вхояамк соответствующих элементов И и ИЛИ, управляняцие входы мажоритарных элементов подключены к первой шине задания режима устройства, управляющие входы элементов И подключены ко второй шине задания режима устройства, выход каждого элемента ИЛИ соединен с первьм входом соответствующего управляющего элемента И, второй вход которого под ключен к третьей шине задания режима устройства, входы каждого объединяющего элемента ИЛИ соединены с выходами COOT: этствующир элементов И, ма жоритарного элемента и управляющего элемента И, а выход - с первьаш входами управления узлов анализа соответствующего столбца и с соответству ющим выходом устройства. На чертеже показана функциональная схема предлагаемого устройства для случая п 2. Устройство содержит nx(2m-l) уз 1 (2т-1), 2, лов анализа 1 1(2т-1),...,п мажоритарных элементов 2,22,..., каждый узел анализа 1-fi (где i 2,...,п J 7 1/ Umсодержит элемент ИЗ, элемент 4 не-, равнозначности, элемент 5 запрета, элементы ИЛИ 6,7 и 8 элеМентьГЙВ у и 10 и элемент И 11. Каяздый узел анализа содержит элемент 12 неравнозначности, элемент 13 запрета, элементы НЕ 14 и 15 и элемент И 16. Устройство имеет и выходов , 17, ..., и п групп входов 18,182,... по (2т-1) входов в ксикдой группу., Устройство дополнительносодержит п элементов ИЛИ 19 , 19,.. . ,п эле - .Ментов И 20 , ..., п управляющих элементов И 21,22,..., п объединяющих элементов ИЛИ 22, 22, ... . Устройство содержит также шины 23,24 и 25 задания режимов, сигналы на которых задаются, например, с помседью регистра 26 режима, выходы которого подключены ко входам дешифратора 27, выходы последнего соединены с шинами 23, 24 и 25 задания режимов. Выход каждого элемента ИЛИ 19ц соединен с первым входом соответствующего управляющего элемента И 21., (k « 1 , . . . ,п). Управляющие входы мажоритарных элементов 2 соединены с шиной 23 задания режимов (появление сигнгша на этих входах мажоритарных элементов позволяет осуществлять прием информации на информационные входы мажоритарных элементов 2) . Управляющие входы элементов И 20|( соединены с шиной 24 задания режимов. Вторые входы элементов И 2IK, соединены с шиной 25 задания режимов. Кдходы элементов И 20, 21vt и мажоритарного элемента 2 соединены со входами элемента ИЛИ 22, выход которого соеди нен с выходом 17ц устройства. При выделении среднего кода единичный сигнал формируется на шине 23 и поступает на управляющие входы мажоритарных элементов 2ц, разрешая прием на них информационных сигналов. На входы 18 устройства поступгиот коды чисел, причем значения первых разрядов кодов поступгиот на входы узлов анализа 1,..., 1(2го-1) и на входы элементов ИЛИ Iftf , И 20, и мажоритарного элемента 2, значения i-x разрядов кодов поступают на входы узлов анализа ,... ,1 (2m-.1 ). Элементы И 2OK и 21к закрыты нулевыми сигналами на шингш 24 и 25, а мажоритарные элементы 2ц открыты сигналом на их управляющих входах, поступающим с шины 23, и, таким образом, к выходу 17ц подключен через элемент ИЛИ 22ц выход мгикоритарного элемента 2. В режиме в 4деления среднего кода предлагаемое устройство работает так же, как и известное. На выходе мгико ритарного элемента 2 (и соответственно на выходе 17 ) образуется значение первого разряда кода, которое затем сравнивается узлами анализа

,..., l(2m-1) с первьши разрядами оответствующих чисел. При совпадении

начений первого разряда J-oro числа выходного разряда (О, О или 1, 1) устройство подготавливает ледующий узел анализа к приему 5 торого разряда соответствующего чу

ла, который проходит на соответствущий j-ый вход мажоритарного элемента 2. Ъ случае несовпадения значений первого разряда числа и выход- Ю ного разряда (0, или j., на соответствующие j-ые входы всех мажоритарных элементов 2,.., подаются соответственно значения О или 1. После поступления на BXOXUJ .с мажоритарного элемента 2j значений разрядов чисел, первые разряды «оторых совпадают по величине с первым разрядом результата, а также значений О или 1 вместо разрядов тех чисел, первые разряды которых не сов- 20 падают по величине с первым разряом результата, этим мажоритарным элементом 2 формируется значение второго разряда результата, которое поступает на выход ITj и сравнивает- 25 ся затем на блоках , .. . , (2т-1), которые соответствуют тем числам, первые разряды которых совпадают по величине с первым разрядом результата. Дсшьнейшая работа устройства по ЗО формированию последующих разрядов результата и их анализу в соответствии с соответствующими разрядами чисел аналогична вышеуказанной. Таким образом, на выходах ,...,17), фор- 35 мируется средний код.

В режиме выделения минимального кода сигнал 1 формируется на шине 24 по потоку к выходам 17. .. ,17, , которые оказываются подключенньвин (через элементы ИЛИ 22,..., 22,). Элементы И , ... ,20и соответственно, элементы ИЛИ 19 ,...,19 и мажоритарные элементы 2 ,..., 2 в это время отключены от выходов 17 , ...,17ц соответственно, так как 45 сигналы на шинах 23 и 25 в это врей равны О.- При анализе первых разрядов всех чисел, поступающих на входы 18 , И 20j срабатывает только в том случае, когда все 50 эти разряды равны 1, в случае же наличия среди первых разрядов чисел хотя бы одного О сигнал на выходе элемента И 20,(и соответственно на выходе 17) равен О. Таким образом- с на выходе 17 формируется первый разряд результата, значение которого совпадает со значением первого разряда минимального числа;

После этого аналогично режиму выделения среднего кода производится 60 сравнение первого разряда результата и первых разрядов сравниваемых чисел (с учетом того, что в даниом случае запрещенной является комбинация, когда разряд числа равен О, а разг 65

ряд результата равен 1, чего не может произойти в правильно работающем устройстве). Таким образом, последующие разряды тех чисел, у которых соответствующий разряд не совпадает с разрядом результата, заменяются при фориишровании последующих разрядов результата значениями 1, а само формирование последующих разрядов результата на элементах И 202. ..., 20f| осуществляется аналогично указанному выше. Таким образом, на каждый из. выходов 1.7 ,...,17j, проходит значение О,если присутствует хотя бы один О среди соответствующих разрядов сравниваемьос чисел, а разряды тех чисел, предыдущие разряды которых не совпадают с разрядами результата, заменяются на значения 1 ив дальнейшем сравнении е участвуют,

В режиме выделения максимального кода сигнал 1 формируется на шине 25 и выходы элементов ИЛИ 19,...,19 через открытые по второму входу.элементы И 21 ,...,21 и элементы ИЛИ 22 ,...f22и оказываются подключенным к выходам 17 ,...,17, соответственно Выходы элементов И 20 , .. ., 20„ и мажоритарных элементов 2 ,...,2 и в это время отключены от соответствующих выходов 17 , ...,17,, так сигналы на шинах 23 и 24 в это время равны О. При ангилизе первых разрядов все чисел, поступающих на входы 1В , элемент ИЛИ 19) передает ,на выход 17 значение 1 в случае наличия ее в первом разряде хотя бы одного из чисел, в дальнейшем производится сравнение первого разряда каждого из чисел с первым разрядом результата с помощью узлов анализа l|,...,( x(2m-l) так же, как было указано ранее (в данном случае запрещенной является такая ситуация, когда разря числа равен 1, а соответствующий разряд результата равен О). В тех из чисел, в которых значения разрядов не совпадают со значением разряда результата, все последующие разряды заменяются значениями О и, таким образом, эти числа в дальнейшем выделении максимального кода не участвуют. Во всех последующих разрядах вьаделение производится аналогично: в случае наличия значения 1 в соответствующем разряде хотя бы одного из сравниваемых чисел это эначение передается на соответствующий выход 17.

Таким образом, предлагаемое устроство по сравнению с известным кроме выделения значения среднего кода позволяет выделять значения минимального и максимального кодов, что ведет к расширению его ф пкциональных возможностей . Формула изобретения Устройство для выделения многоразрядного кода по авт.св. 746501, отличающееся тем, что, S целью расширения функциональных возможностей за счет вьзделения наряду со средним максимального и минимальногр кодов, оно содержит дополнительно п элементов ИЛИ, п элементо И, п управляющих элементов И и п объединяющих элементов ИЛИ, причем информационные входы каждого мажоритарного элемента соединены с одноименными входами соответствующих эле ментов И и ИЛИ, управляющие входы мажоритарных элементов подключены к первой шине задания режима устройств управляющие входы элементов И подклю чены ко второй шине задания режима устройства, выход каждого элемента ИЛИ соединен с первым входом cootнетствукяаего управляющего элемента.И, второй вход которого подключен к третьей ишне задания режима устройства, входы каящого объединяющего элемента ИЛИ соединены с выходами соответствующих элементов И, мажоритарного элемента и управляющего элемента И, а выход - с первьа-ш входами управления узлов анализа соответствующего столбца и с соответствумцим выходом устройства. Источники информации; принятые во внимание при экспертизе 1. Авторское свидетельство СССР I 746501 (по заявке 2568141/1в- 24), КЛ.6 06 F 7/02, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения многоразрядного кода | 1978 |

|

SU746501A1 |

| Устройство для анализа и обработки знаковых разрядов | 1980 |

|

SU962921A1 |

| Устройство для определения среднегоиз TPEX дВОичНыХ чиСЕл | 1979 |

|

SU851401A1 |

| Устройство для определения среднего из @ чисел | 1984 |

|

SU1211717A1 |

| Устройство для определения фазы спектральных составляющих | 1982 |

|

SU1080148A1 |

| Устройство для сравнения последовательных кодов чисел | 1973 |

|

SU486315A1 |

| Устройство для сравнения чисел | 1978 |

|

SU771664A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

Авторы

Даты

1981-09-30—Публикация

1979-04-16—Подача