Изобретение относится к вычислительной технике и предназначено для использования в электронных цифровых вычислительных машинах, в частности в электронных клавиш ных вычислительных машинах (ЭКВМ), в которых числа представлены в последовательном двоично-десятичном коде. Известны последовтельные двоично-десятичные сумматоры-вычитатели, содержащие два сумматора со схемами переноса, четырехразрядный регистр сдвига, схему коррекции с триггером коррекции, а также схему формирования инверсного кода, или имею щие в первое сумматоре схему формирования заема для выполнения операции вычитания 1. Наиболее близким к изобретению является последовательный двоично-десятичный сумматор-вычитатель, содержащий первый и второй сумматоры со схемами формирователя переноса, формирователь инверсного кода, четырехразрядный регистр сдвига, схему коррекции, выполненную на элементах И и ИЛИ, и триггер коррекции 2. Однако последовательный двоично-десятичный сумматор-вычитатель имеет ряд существенных недостатков, а именно: большое количество оборудования, что вызвано необходимостью формирования двух различных корректирующих кодов «ОНО и 1010 соответственно при выполнении операции сложения и вычитания; больщое количество связей в схеме, что является особенно важным критерием при реализации устройства на больших интегральных схемах. Цель изобретения - уменьщение количества оборудования. Поставленная цель достигается тем, что последовательный двоично-десятичнй сумматор-вычитатель, содержащий первый и второй сумматоры, первый и второй узлы формирования переноса, четырехразрядный регистр сдвига, элементы И и ИЛИ, причем вход первого слагаемого подключен к первому входу первого сумматора, выход которого подключен ко входу регистра сдвига, выход которого соединен с первым входом второго сумматора, вторые входы первого и второго сумматора соединены с первыми входами первого и второго узлов формирования переноса соответственно, третьи входы первого и второго сумматоров соединены со вторыми входами, первого и второго узлов формирования переноса соответственно.

выходы второго и третьего разрядов регистра сдвига подключены ко входам первого элемента ИЛИ, выход первого рзряда регистра сдвига подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, третий вход - к первому входу синхронизации сумматора-вычитателя, а выход - к первому входу второго элемента ИЛИ, выходы второго и третьего элементов И соединены со входами третьего элемента ИЛИ, содержит элемент неравнозначности, элемент равнозначности, элемент запрета и элементы задержки, причем входы элемента неравнозначности соединены со входом первого слагаемого и первой управляющей шиной, а выход подключен к третьему входу первого узла формирования переноса, выход которого через первый элемент задержки подключен ко второму входу второго элемента ИЛИ, выход которого соединен с третьим входом первого сумматора, второй вход которого подключен ко входу второго слагаемого, выход третьего элемента ИЛИ через второй элемент задержки соединен со вторым входом второго сумматора, входы второго элемента И подключены к выходу второго элемента ИЛИ и первому входу синхронизации сумматора-вычитателя, входы третьего элемента И подключены ко второму входу синхронизации сумматора-вычитателя и выходу третьего элемента задержки, вход которого подключен к выходу второго элемента задержки, входы элемента равнозначности подключены к выходу регистра сдвига и первой управляющей щине, а выход подключен к третьему входу второго узла -формирования переноса, выход которого соединен со входом элемента запрета, первый вход четвертого элемента И соединен со второй управляющей шиной, управляющий вход элемента запрета и второй вход четвертого элемента И подключены к третьему входу синхронизации сумматора-вычитателя, а выходы подключены ко входам четвертого элемента ИЛИ, выход которого через четвертый элемент задержки подключен к третьему входу второго сумматора.

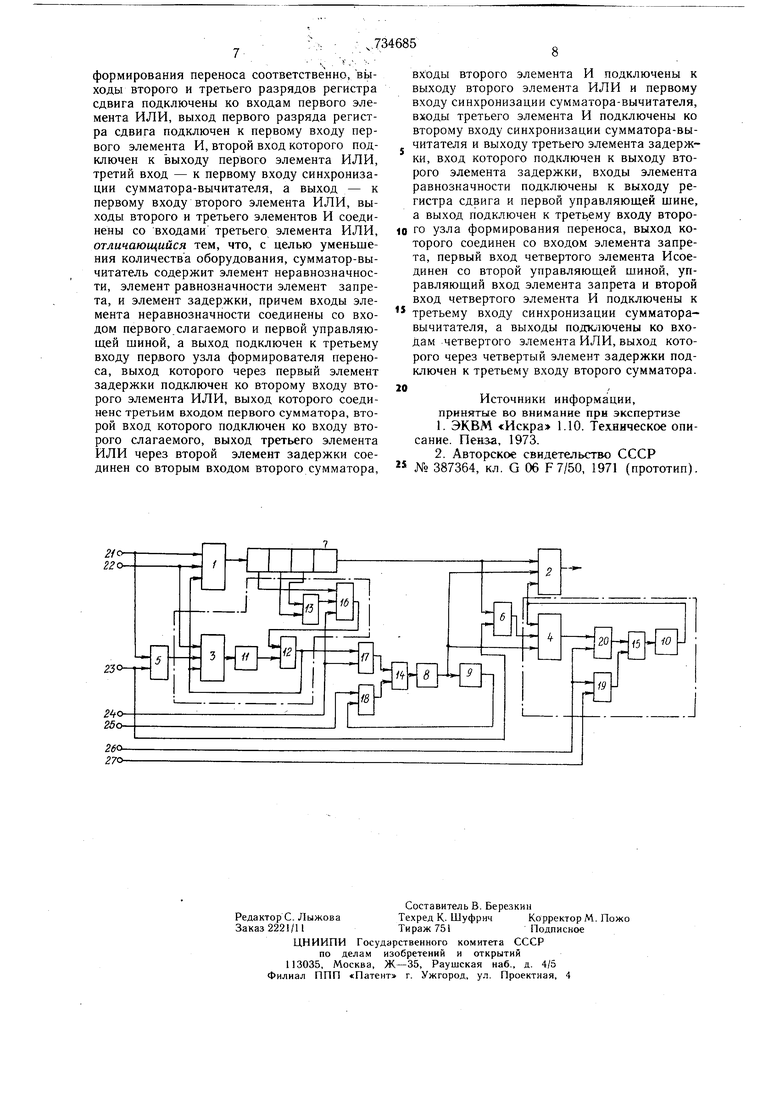

На чертеже представлена блок-схема последовательного двоично-десятичного сумматора-вычитателя.

Устройство содержит первый и второй сумматоры 1 и 2, первый и второй узлы 3 и 4 формирования переноса, элемент 5 неравнозначности, элемент 6 равнозначности, четырехразрядный регистр 7 сдвига, элементы 8 - 11 задержки, элементы 12-15 ИЛИ, элементы 16-19 И, элемент 20 запрета, входы 21 и 22 соответственно первого и второго слагаемого (либо уменьшаемого и вычитаемого), управляющую щину 23, входы 24-26 синхронизации, на которые подаются синхроимпульсы В1, ВЗ, В4 соответственно, управляющую шину 27.

Два числа, представленные в двоичнодесятичном коде, последовательно поступают на входы 21 и 22. Младший разряд каждой тетрады числа (с весом 2) поступает на вход 21 или 22 в течение синхроимпульса В1 (вход 24), второй (с весом 2), третий (с весом 22) и четвертый (с весом 2) разряды тетрады поступают соответственно в течение синхроимпульсов В2 (на чертеже не показан), ВЗ (вход 25 и Б4 (вход 26). При выполнении операции сложения на

управляющей шине 23 устанавливается уровень логического «О , первое слагаемое (вход 21) через элемент 5 неравнозначности и второе слагаемое (вход 22) поступают на входы первого узла 3 формирования переноса, который Б этом случае реализует функцию переноса, на выходе первого сумматора I появляется код нескорректированной суммы.

При выполнении операции вычитания на управляюшей шине 23 установлен уровень

0 логической «1, при этом уменьшаемое через элемент 5 неравнозначности подается на узел 3 формирования переноса, который в этом случае реализует функцию заема, а на выходе первого сумматора 1 появляется

, нескорректированная разность.

Младший разряд (с весом 2°) тетрады нескорректированной суммы (разности) формируется на выходе первого сумматора 1 По синхроимпульсу В1 (вход 24) и записывается в четырехразрядный регистр 7 сдвига, на выходе первого разряда которого этот разряд появляется по синхроимпульсу В2, на выходе второго разряда - в ВЗ (вход 25), на выходе третьего разряда - в В4 (вход 26) и на выходе - в В1 (вход 24. Очевидно, что на выходах первого, второго и третьего разрядов регистра 7 сдвига в течение синхроимпульса В1 (вход 24) определены соответственно разряды тетрады нескорректированной суммы с весами 2, 22, 2.

Код нескорректированной те.трад.ы анализируется элементами ИЛИ 13 и И 16 в том случае, если значение кода (в течение синхроимпульса В - вход 24) превосходит девятку - «9 (код 1001), на выходе элемента 16 И формируется сигнал логической «1, который является признаком коррекции запрещенной комбинации, и через элемент 12 ИЛИ поступает на первый вход элемента 17 И, второй вход которой соединен

0 с входом 24 синхронизации. Сигнал логической «1 с выхода элемента 17 И через элемент 14 ИЛИ поступает на элемент 8 задержки, с выхода которого в течение синхроимпульса В2 поступает на вход второго сумматора 2, а также на вход элемента 9

задержки.

С выхода элемента 9 задержки сигнал логической «1 в течение синхроимпульса ВЗ (вход 25) поступает на вход элемента 18 И, другой вход которого соединен со входом 25 синхронизации. С выхода элемента 18 И логическая «1 поступает на вход элемента 8 задержки, с выхода которого в течение В4 поступает на вход второго сумматора 2. Таким образом, на выходе элемента 8 задержки формируется последовательный двоично-десятичный корректирующий код 1010 («10). Выход элемента 16 И через элемент 12 ИЛИ соединен со входами первого сумматора 1 и узла 3 формирования переноса и при возникновении запрещенной комбинации в тетраде нескорректированной суммы (разности) формируется перенос (заем) в следующую тетраду на первом сумматоре 1. Сигнал переноса (заема) с выхода узла 3 формирования переноса через элемент 11 задержки и элемент 12 ИЛИ поступает на входы первого сумматора 1 и узла 3 формирования переноса. Сигнал переноса (заема) на выходе элемента 11 задержки, совпадающий во времени с синхроимпульсом В1 (вход 24), является межтетрадным переносом (заемом) и через элементы И 17 и ИЛИ 14 поступает на вход элемента 8 задержки, что приводит к формированию корректирующего кода. При выполнении операции сложения (на шине входа 23 - логический «О), на первом сумматоре. 1 узла 3 формирования переноса реализуется операция сложения двух чисел, а на втором сумматоре 2 и узле 4 формирования переноса реализуется вычитание из нескорректированной тетрады суммы корректирующего, кода 1010. Причем, узел 3 формирования переноса реализует логическую функцию переноса, а узел 4 формирования переноса - логическую функцию заема. При выполнении операции вычитания (на щине 23 - логическая «1) на первом сумматоре 1 и узле 3 формирования переноса реализуется операция вычитания двух чисйл, а на втором сумматоре 2 и узле 4 формирования переноса реализуется сложение нескорректированной тетрады разности с корректирующим кодом. Коррекция необходима при появлении запрещенной комбинации (значение тетрады больше 9), а также при возникновении межтетрадного переноса или заеМа. Использование элементов неравнозначности 5 и равнозначности 6 на входах узлов 3 и 4 формирования переноса позволяет в одном автоматном цикле выполнять в предлагаемом последовательном двоично-десятичном сумматоре-вычитателе как операцию сложения, так и операцию вычитания, что особенно важно при выполнении операции умножения и деления. Так, при выполнении операции умножения в одном и том же автоматном цикле (такте) можно производить накопление множимого (на щине 23 - логический «О) и операцию вычитания «1 из множителя. При команде логический «О на щине 23 первый сумматор 1 реализует операцию суммирования, а второй сумматор 2 «настроен на вычитание (второй узел 4 формирования переноса реализует операцию зае.ма) и по команде вычитания «1 из множителя (логическая «1 на щине 27) и синхроимпульсу iB41 (вход 26) вырабатывается сигнал логической «1 на выходе элемента 19 И, которая через элемент 15 ИЛИ и элемент 10 задержки поступает в течение синхроимпульса В1 на входы второго сумматора 2 и узла 4 формирования переноса, реализуя вычитание «1 из множителя. При выполнении операции деления с использовнием обычных алгоритмов, при которых частное и делимое расположены в одЦом последовательном регистре, на первом сумматоре 1 реализуется вычитание делителя из делимого (или его остатка) и при каждом «удачном вычитании осуществляется накопление частного (при этой операции второй сумматор 2 «настроен на сложение) по синхроимпульсу В4 (вход 26) и команде (щина 27). Элемент запрета предназначен для блокирования межтетрадного переноса, возникающего при коррекции. Широкое использование элементов задержки с точки зрения затрат оборудования, количества связей и топологической однородности, что особено важно при проектировании устройств на БИС, выгодно отличает предлагаемое устройство от известного. Возможность проведения в течение одного автоматного цикла обработки множителя и произведения (делимого и частного) расщиряет функциональные возможности устройства и позволяет строить на его основе большой класс вычислительных устройства, имеющих широкие функциональные, возможности при выполнении операций умножения и деления. Формула изобретения Последовательный двоично-десятичный сумматор-вычитатель, содержащий первый и второй сумматоры, первый и второй узлы формирования переноса, четырехразрядный регистр сдвига, элементы И и ИЛИ, причем вход первого слагаемого подключен к первому входу первого сумматора, выход которого подключен ко входу регистра сдвига, выход которого соединен с первым входом второго сумматора, вторые входы первого и второго сумматора соединены с первыми входами первого и второго узлов формирования переноса соответственно,третьи входы первого и второго сумматоров соединены со вторыми входами первого к второго узлов

формирования переноса соответственно, выходы второго и третьего разрядов регистра сдвига подключены ко входам первого элемента ИЛИ, выход первого разряда регистра сдвига подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, третий вход - к первому входу синхронизации сумматора-вычитателя, а выход - к первому входу второго элемента ИЛИ, выходы второго и третьего элементов И соединены со входами третьего элемента ИЛИ, отличающийся тем, что, с целью уменьшения количества оборудования, сумматор-вычитатель содержит элемент неравнозначности, элемент равнозначности элемент запрета, и элемент задержки, причем входы элемента неравнозначности соединены со входом первого,слагаемого и первой управляющей шиной, а выход подключен к третьему входу первого узла формирователя переноса, выход которого через первый элемент задержки подключен ко второму входу второго элемента ИЛИ, выход которого соединенс третьим входом первого сумматора, второй вход которого подключен ко входу второго слагаемого, выход третьего элемента ИЛИ через второй элемент задержки соединен со вторым входом второго сумматора.

входы второго элемента И подключены к выходу второго элемента ИЛИ и первому входу синхронизации сумматора-вычитателя, входы третьего элемента И подключены ко второму входу синхронизации сумматора-вычитателя и выходу третьего элемента задержки, вход которого подключен к выходу второго элемента задержки, входы элемента равнозначности подключены к выходу регистра сдвига и первой управляющей шине, а выход подключен к третьему входу второго узла формирования переноса, выход которого соединен со входом элемента запрета, первый вход четвертого элемента Исоединен со второй управляюш.ей шиной, управляющий вход элемента запрета и второй вход четвертого элемента И подключены к

третьему входу синхронизации сумматоравычитателя, а выходы подключены ко входам четвертого элемента ИЛИ, выход которого через четвертый элемент задержки подключен к третьему входу второго сумматора.

Источники информации, принятые во внимание при экспертизе

1.ЭКВМ «Искра 1.10. Техническое описание. Пенаа, 1973.

2.Авторское свидетельство СССР

№ 387364, кл. G 06 F 7/50, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| БИЬЛИО': | 1973 |

|

SU387364A1 |

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| Устройство для суммирования двоично-десятичных кодов | 1977 |

|

SU684542A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

Авторы

Даты

1980-05-15—Публикация

1978-02-08—Подача