Изобретение относится к области цифровой вычислительной техники и может бить использовано в специализированных цифровых вычислительных маDWHcix СЦВП , применяемых в замкнутых контурах систем автоматического управления и регулирования, например, в системах навигации и гироскопической стабилизации.

В управляющих ЦВМ масштаб величин выбирают из условий обеспечения диапазона изменения в установившемся режиме, который меньше диапазона изменения этих же параметров в переходном режиме. Поэтому в переходном режиме может произойти переполнение разрядной сетки арифметико-логического устройства (АЛУ). Если не принять каких-либо дополнительных мер, то в этих случаях результаты вы- ; слений будут неверны не только по величине, но и по знаку. Поэтому при проектировании СЦВМ следует предусмотреть возможность получения предельных значений результата с соответствующим знаком при переполнении разрядной сетки. Выполнение этого требования позволяет сохранить точность вычислений в установившихся режимах, одновременно обеспечить

нормальное функционирование систе «ы в переходном режиме при некотором допустимом увеличении времени переходного процесса.

Известны АЛУ с фиксированной запятой, имеющие устройства для обнаружения переполнения. Для получения признака переполнения разрядной сетки применяются так называемые моди10фицированные коды. Они отличаются тем, что для представления знака используются два разряда, при этом знак плюс обозначается 00, а знак минус 11.

15

Для обнаружения переполнения, учитывая, что г эдуль суммы 2-х чисел , модуль каждого из которых меньше единицы, всегда меньше |2 (, ис20пользуют один дополнительный разряд знака для получения модифицированно го кода. На переполнение разрядной сетки указывает несовпг.дение цифр в знаковых разрядах. Комбинации 01

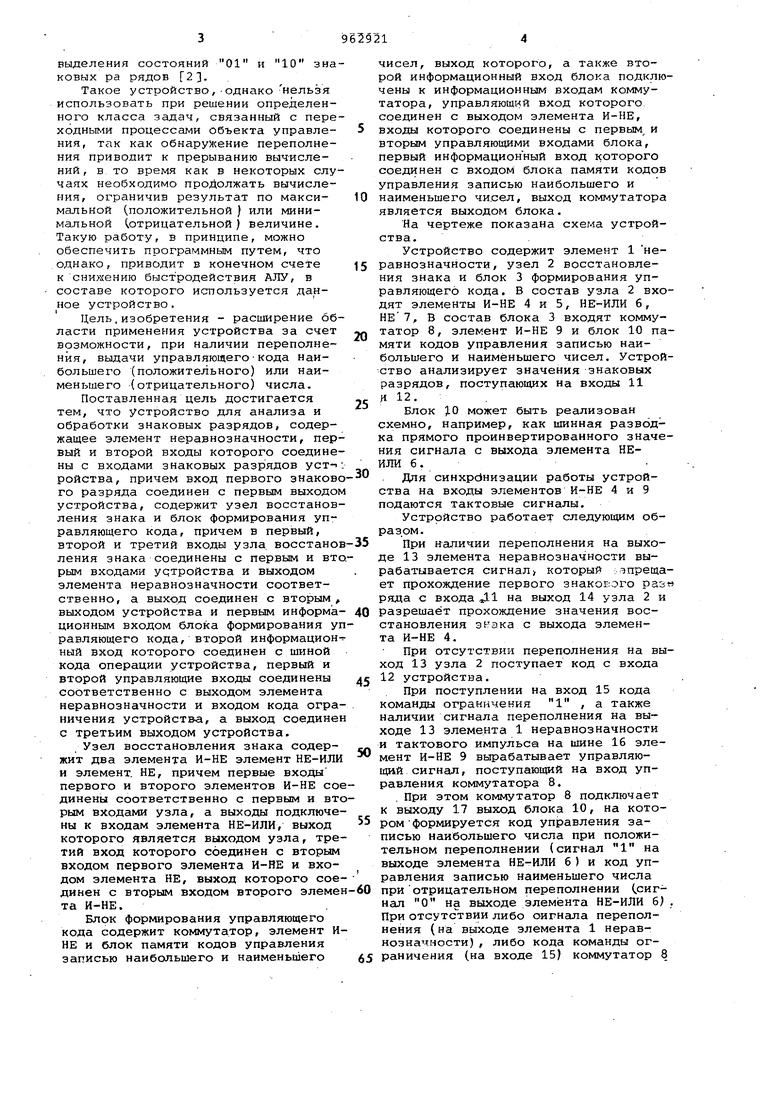

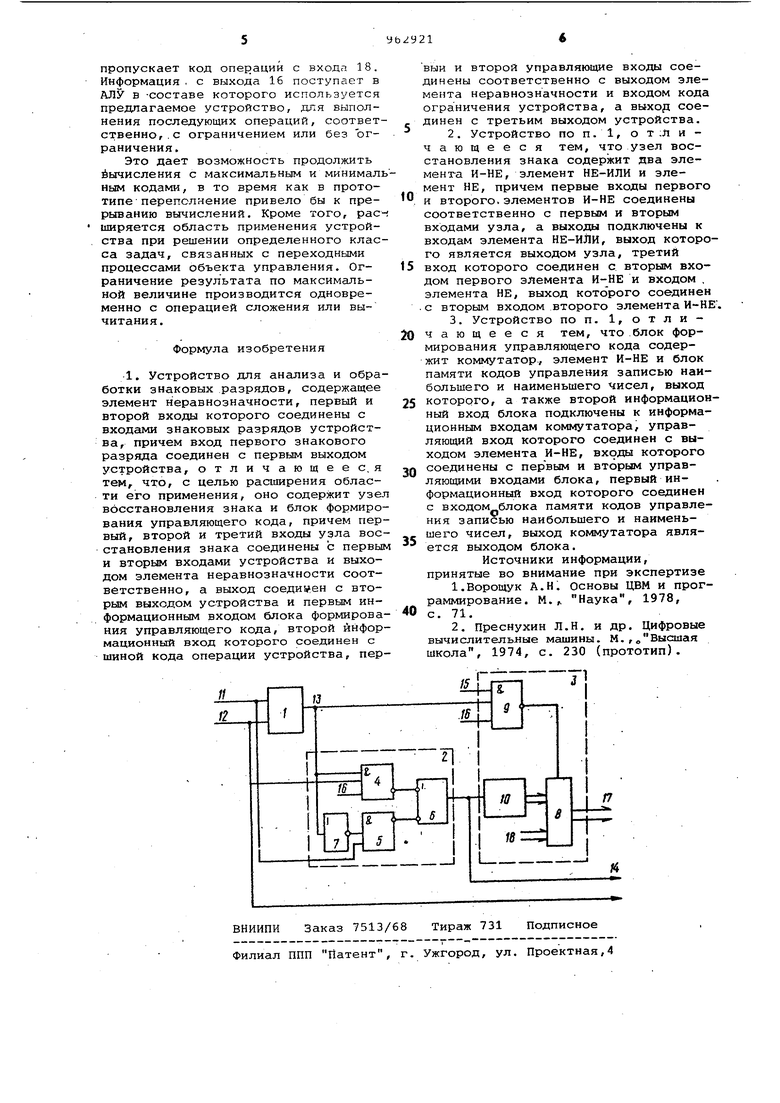

25 соответствует положительное число, а 10 - отрицательное число tl Наиболее близким к предлагаемому является устройство для анализа и обработки знаковых разрядов, содер30Жбццее элемент неравнозначности для выделения состояний 01 и 10 зна ковых ра рядов 2. Такое устройство,-однако нельзя использовать при решении определенного класса задач, связанный с переходными процессами объекта управления, так как обнаружение переполнения приводит к прерыванию выч-ислений, в то время как в некоторых случаях необходимо продолжать вычисления, ограничив результат по максимальной (положительной ) или минимальной (отрицательной) величине. Такую работу, в принципе, можно обеспечить программным путем, что однако, приводит в конечном счете к снижению быстродействия АЛУ, в составе которого используется данное устройство, Цель,изобретения - расширение области применения устройства за счет возможности, при наличии переполнения, выдачи управляющегокода наибольшего (положительного) или наименьшего (отрицательного) числа. Поставленная цель достигается тем, что устройство для анализа и обработки знаковых разрядов, содержащее элемент неравнозначности, первый и второй входы которого соединены с входами знаковых разрядов уст ройства, причем вход первого знаково го разряда соединен с первым выходом устройства, содержит узел восстановления знака и блок формирования управляющего кода, причем в первый, второй и третий входы узла, восстанов Ленин знака соединены с первым и вто рым входами учтройства и выходом элемента неравнозначности соответственно, а выход соединен с вторым выходом устройства и первым информационным входом блока формирования уп равляющего кода, второй информационный вход которого соединен с шиной кода операции устройства, первый и второй управляющие входы соединены соответственно с выходом элемента неравнозначности и входом кода ограничения устройства, а выход соединен с третьим выходом устройства. Узел восстановления знака содержит два элемента И-НЕ элемент НЕ-ИЛИ и элемент. НЕ, причем первые входы первого и второго элементов И-НЕ сое динены соответственно с первым и вто рым входами узла, а выходы подключены к входам элемента НЕ-ИЛИ, выход которого является выходом узла, третий вход которого соединен с вторым входом первого элемента И-НЕ и входом элемента НЕ, выход которого сое динен с вторьом входом второго элеме та И-НЕ. Блок формирования управляющего кода содержит коммутатор, элемент И НЕ и блок памяти кодов управления записью наибольшего и наименьшего чисел, выход которого, а также второй информационный вход блока подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом элемента И-НЕ, входы которого соединены с первым и вторым управляющими входами блока, первый информационный вход которого соединен с входом блока памяти кодов управления записью наибольшего и наименьшего чисел, выход коммутатора является выходом блока. На чертеже показана схема устройства. Устройство содержит элемент 1 неравнозначности, узел 2 восстановления знака и блок 3 формирования управляющего кода. В состав узла 2 входят элементы И-НЕ 4 и 5, НЕ-ИЛИ 6, НЕ 7, В состав блока 3 входят коммутатор 8, элемент И-НЕ 9 и блок 10 памяти кодов управления записью наибольшего и наименьшего чисел. Устройство анализирует значения знаковых разрядов, поступающих на входы 11 fi 12. Блок 5-0 может быть реализован схемно, например, как шинная разводка прямого проинвертированного значения сигнала с выхода элемента НЕИЛИ б. Для синхрбнизации работы устройства на входы элементов И-НЕ 4 и 9 подаются тактовые сигналы. Устройство работает следующим образрм. При наличии переполнения на выходе 13 элемента неравнозначности вырабатывается сигнал который :зпрещает прохождение первого знакового раз« ряда с входа Д1 на выход 14 узла 2 и разрешает прохождение значения восстановления знака с выхода элемента И-НЕ 4. При отсутствии переполнения на выход 13 узла 2 поступает код с входа 12 устройства. При поступлении на вход 15 кода команды ограничения 1 , а также наличии сигнала переполнения на выходе 13 элемента 1 неравнозначности и тактового импульса на шине 16 элемент И-НЕ 9 вырабатывает управляющий сигнал, поступающий на вход управления коммутатора 8. При этом коммутатор 8 подключает к выходу 17 выход блока 10, на котором формируется код управления записью наибольшего числа при положительном переполнении (сигнал 1 на выходе элемента НЕ-ИЛИ б ) и код управления записью наименьшего числа при отрицательном переполнении (.сигнал О на выходе элемента НЕ-ИЛИ 6) , При отсутс твии либо сигнала переполнения (на выходе элемента 1 неравнозначности) , либо кода команды ограничения (на входе 15) коммутатор 8 пропускает код операций с входа 18 Информация , с выхода 16 поступает АЛУ в -составе которого используетс предлагаемое устройство, для выпол нения последующих операций, соответ ственно,, с ограничением или без ограничения. Это дает возможность продолжить ёыгаисления с максимальным и минимал ным кодами, в то время как в прототипе- переполнение привело бы к прерыванию вычислений. Кроме того, рас ширяется область применения устройства при решении определенного клас са задач, связанных с переходными процессами объекта управления. Ограничение результата по максимальной величине производится одновременно с операцией сложения или вычитания. Формула изобретения 1. Устройство для анализа и обра ботки знаковых разрядов, содержащее элемент неравнозначности, первый и второй входы которого соединены с входами знаковых разрядов устройства, причем вход первого знакового разряда соединен с первым выходом устройства, отличающее с, я тем что, с целью расгоирения области его применения, оно содержит узел восстановления знака и блок формирования управляющего кода, причем первый, второй и третий входы узла восстановления знака соединены с первым и вторым входами устройства и выходом элемента неравнозначности соответственно, а выход соединен с вторым выходом устройства и первым информационным входом блока формирования управляющего кода, второй информационный вход которого соединен с шиной кода операции устройства, первыи и второй управляющие входы соединены соответственно с выходом элемента неравнозначности и входом кода ограничения устройства, а выхор соединен с третьим выходом устройства. 2.Устройство по п. 1, о т ;Л и чающееся тем, что узел восстановления знака содержит два элемента И-НЕ, злемент НЕ-ИЛИ и элемент НЕ, причем первые входы первого и второго.элементов И-НЕ соединены соответственно с первым и вторым входами узла, а выходы подключены к входам элемента НЕ-ИЛИ, выход которого является выходом узла, третий вход которого соединен с вторым входом первого элемента И-НЕ и входом элемента НЕ, выход которого соединен с вторым входом второго элемента И-НЕ. 3.Устройство по п. 1, отличающееся тем, что .блок формирования управляющего кода содержит коммутатор., элемент И-НЕ и блок памяти кодов управления записью наибольшего и наименьшего чисел, выход которого, а также второй информационный вход блока подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом элемента И-НЕ, входы которого соединены с первым и вторым управляющими входами блока, первый информационный вход которого соединен с входом блока памяти кодов управления записью наибольшего и наименьего чисел, выход коммутатора является выходом блока. Источники информации, ринятые во внимание при экспертизе 1.Ворощук А.Н. Основы ЦВМ и прогаммирование. М. Наука, 1978, . 71. 2. Преснухин Л.Н. и др. Цифровые ычислительные машины. М.,„ Высшая кола, 1974, с. 230 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Авторы

Даты

1982-09-30—Публикация

1980-02-15—Подача