(54) ДЕЛИТЕТЬ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с регулируемым коэффициентом деления | 1980 |

|

SU924865A1 |

| Устройство для контроля времени работы машин | 1981 |

|

SU949672A2 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Измеритель скважности последовательности прямоугольных импульсов | 1976 |

|

SU742819A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Устройство для определения средне-КВАдРАТичЕСКОгО ОТКлОНЕНия Слу-чАйНОй ВЕличиНы | 1979 |

|

SU849230A1 |

| Устройство для измерения глубины скважины | 1986 |

|

SU1406354A1 |

| Устройство для измерения глубины скважины | 1988 |

|

SU1579991A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

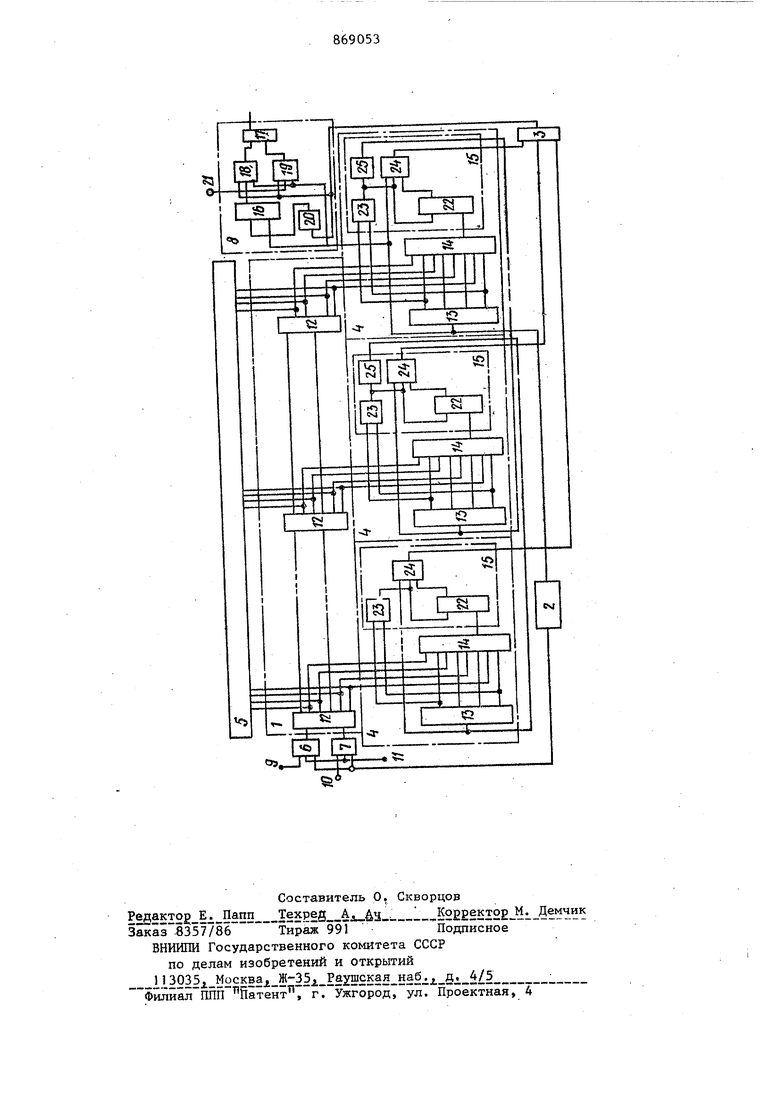

Изобретение относится к автоматике и передаче данных и может быть использовано, например, в различных радиотехнических устройствах для изменения частоты импульсов. Известен делитель частоты импульсов, содержащий формирователь импуль сов, выход которого соединен через элементы И со входом счетчика и со входом узла установки целых чисел, детектор заполнения, узел задания, а также элементы . Недостатками этого устройства являются ограниченные функциональные возможности и относительно большая сложность. Наиболее близким техническим решением к предлагаемому является делитель частоты импульсов, содержащий блок памяти, формирователь импульсов элемент ИЛИ и счетные декады, и блок индикации, входы которого соединейы с выходами блока памяти, а выход фор мирователя импульсов соединен со счетным входом первой счетной декады 121. Недостатком этого делителя частоты импульсов является ограниченность его функциональньос возможностей. Цель изобретения - расширение функциональных возможностей. Поставленная цель достигается тем, что в делитель частоты импульсов, содержащий блок памяти, формировател. импульсов, элег::ент ИЛИ и счетные декады, и блок индикации, входы которого соединены с выходами блока памяти, выход формирователя импульсов соединен со счетным входом перьой счетной декады, введены первый и в- эрой элементы совпадения и блок коррекции, первый вход которого соединея с выходом элемента ИЛИ, входы кбторого соединены с первым1 выходами счетных декад, второй выход каждой из которых соединен со счетным входом следующей счетной декады, информационные входы казкдой счетной декады соединены с соответствующей группой выходов блока памяти, первый и второ входы которого соединены с выходами соответственно первого и второго элементов совпадения, первые входы к торых соединены соответственно с пер вым и вторьм входами делителя частот импульсов, третий вход которого соеди нен с вторьии входами первого и второго элементов совпадения, третьи входы которых соединены с Дополнител ным выходом формирователя импульсов, выход которого соединен с вторым входом блока коррекции. Блок памяти содержит разностные счетчики, выходы которых соединены с группами выходов блока памяти, первый и второй входы которого соединены соответственно с входами .суммирования и вычитания первого разностного счетчика, а входы суммирования и вычитания каждого из остальных разностных счетчиков соединены с выходами соответственно переноса и заема предьщущего разностного счет чика . Каждая счетная декада содержит десятичный счётчик, элемент сравнения и формирователь группы импульсов выход которого соединен с выходом данной счетной декады, счетный вход которой соединен со счетным входом десятичного счетчика, выходы которого соединены с первыми входами элемента сравнения, вторые входы которо го соединены с информационными входа ми данной счетной декады, выходы пер вого и последнего разрядов десятичного счетчика соединены соответственно с первым и вторым входами формирователя группы импульсов, третий вход которого соединен с выходом эле мента сравнения, а дополнительный вы ход формирователя группы импульсов соединен с дополнительным выходом счетной декады, счетный вход счетной декады соединен с четвертым входом формирователя группы импульсов. Блок коррекции содержит первый и второй триггеры, первый и второй эле менты И и инвертор, вход которого соединен с первым входом блока коррекции и первыми входами цервого и второго элементов И, вторые входы : которых соединены с вторым входом блока коррекции и первым входом первого триггера, второй вход которого соединен с выходом инвертора, выход первого триггера соединен с третьим 34 входом первого элемента И, выход которого соединен с первым входом второго, триггера, выход и второй вход которОло соединены соответственно с выходом .блока коррекции и выходом второго элемента И, третий вход которого соединен с дополнительным входом блока коррекции. Каждый формирователь группы импульсов содержит триггер и первый и второй элементы Hj первый и второй входы первого элемента И соединены соответственно с первым и вторым входами формирователя группы импульсов, третий вход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого элемента И и первым входом второго элемента И, второй вход и выход которого соединены соответственно с выходом триггера и выходом формирователя группы импульсов, четвертый вход которого соединен с третьим входом второго зпемента И, а каждый формирователь импульсов, кроме последнего, содержит также инвертор, вход и выход которого соединены соответственно с выходом первого элемента И и дополнительным выходом данного формирователя группы импульсов. На чертеже показана структурная схема делителя частоты импульсов. Делитель частоты импульсов, содержащий блок 1 памяти, формирователь 2 импульсов, элемент ИЛИ 3, счетные декады 4, блок 5 индикации, первый 6 и второй 7 элементы совпадения и блок 8 коррекции, входы блока 5 ин Хйкации соединены с выходами блока 1 памяти, а выход формирователя 2 импульсов соединен со счетньм входом первой счетной декады 4, первый вход блока 8 коррекции соединен с выходом элемента ИЛИ 3, входы которого соединены с первыми выходами счетных декад 4, второй выход каждой из которых соединен со счетным входам следующей счетной декады, информационные входы каждой счетной декады- 4 соединены с соответствующей группой В1 хоДОв блока I памяти, первый и Второй входы которого соединекы с выходами соответственно первого 6 и второго 7 элементов совпадения, первые входы которых соединены соответственно с первым 9 и вторым 10 входами делителя частоты импульсов, третий вход 11 которого соединен с вторыми вхо;ками первого 6 и второго 7 эле5 .ментов совпадения, третьи входы кото рых соединены с дополнительным выхо дом формирователя 2 импульсов, выход которого соединен с вторым входом бл ка 8 коррекции. Блок 1 памяти содержит разностные счетчики 12, выходы которых соединены с группами выходов блока 1 па мяти, первый и второй входы которого соединены соответственно с входами суммирования и вьмитания первого разностного счетчика 12, а входы сум мирования и вычитания каждого из остальных разностных счетчиков 12 соединены с выходами соответственно пет реноса и заема предьщущего разностно го счртчика 12, Каждая счетная декада 4 содержит десятичный счетчик 13, элемент 14 сравнения и формирователь 15 группы импульсов, выход которого соединен с выходим данной счетной декады 4, счетный вход которой соединен со счетным входом десятичного счетчика 13, выходы которого соединены с первыми входами элемента 14 сравнения, вторые входы которого соединены с информационными входами данной счетной декады, выходы первого и последнего разрядов десятичного счет чика 13 соединены соответственно с первым и вторым входами формировател 15 группы импульсов, третий вход которого соединен с выходом элемента 14 сравнения, дополнительный выход формирователя 15 группы импульсов соединен с дополнительным выходом . счетной декады 4, а счетный вход сче ной декады 4 соединен с четвертым входом формирователя 15 группы импульсов. Блок 8 коррекции содержит первый 16 и второй 17 триггеры, первый 8 и второй 19 элементы И и инвертор 20, вход которого соединен с первым входом блока 8 коррекции и первыми входами первого 18 и второго 19 элементов И, вторые входы которых соеди нены с вторым входом блока 8 коррекции и первым входом первого триггера 16, второй вход которого соединен с выходом инвертора 20, выход первого триггера 16 соединен с третьим входом первого элемента И 18, выход которого соединен с первым входом второго триггера 17, выход и второй вхо которого соединены соответственно с выходом блока 8 коррекции и выходом рторого элемента И 19,третий вход 3 крторого соедиген с дополнительным входом 21 блока 8 коррекции. Каждый формирователь -15 группы импульсов содержит триггер 22 и первый 23 и второй 24 элементы И, первый и второй входы первого элемента И 23 соединены соответственно с первым и Btopbw входами формирователя 15 группы импульсов, третий вход которого соединен с первым входом триггера 22, второй вход которого соединен с выходом первого элемента И 23 и первым входом второго элемента И 24, второй вход и выход которого соединены соответственно с выходом триггера 22 и выходом формирователя 15 группы импульсов, четвертьй вход которого соединен с третьим входом второго элемента И 24, а каждый формирователь импульсов, кроме последнего, содержит также инвертор 25, вход и выход которого соединены соответственно с выходом первого элемента И 23 и дополнительным выходом данного формирователя 15 группы импульсов. Делитель частоты импульсов работает следующим образом. В исходном состоянии разностные счетчики 12 блока 1 памяти нахгдятся в нулевом состоянии. Сигналом Подстройка на входе 11 подготавливаются элементы 6 и 7. При поступлении сигнала Добавление на вход 9 открывается элемент 6, через который импульс от формирователя 2 импульсов начинает поступать на вход блока 1 памяти, увеличивая его содержимое. которое отображается на блоке 5индикации. В блоке 1 памяти записывается число, соответствующее требуемой величине подстройки (при поступлении сигнала Вычитание на вход О содержимое блока I памяти уменьшается до требуемой величины, отображаемой на блоке 5 икдикаЦии). РЬшульсы тактовой частоты поступают из формирователя 2 импульсов яа вход первой счетной декады 4. Каждое десятое состояние этой счетной декады 3-1 () декодируется элементов И 23 формирователя }5 группы импульсов. Импульсы, формируемые Элементом И 23, переводят в единичное состояние триггер 22 формирователя 15 группы импульсов и одновреенно через инвертор 25 nocTyi aior а вход ртедующей счетной декады 4. 7 Открытый триггером 22 элемент И 24 соответствующей декады начинает пропускать на вход элемента ИЛИ 3 пакет импульсов. Когда число импульсов, поступающих на вход счетной дек ды, стает равным числу, записанному и в соответствующий разностный счетчик 12 блока 1 памяти, элемент 14 сравнения выдает импульс, переводящий .триггер 22 формирователя 15 группы импульсов в нулевое состояние. При этом закрывается соответствующий элемент И 24 и заканчивается формирование пакета импульсов. За время нахождения триггера 22 в единичном состоянии элемент И 24 фор мирует пакет импульсов, число которых в пакете равно числу, записанному в соответствующий разностный счет чик 12 блока 1 памяти. Аналогично работают остальные счетные декады 4 и формирователь 15 группы импульсов. Таким образом, на выходе элемента ИЛИ 3 за цикл формируется пакет импульсов, равный числу, записанному в блоке 1 памяти. Если необходимо уменьшить процент подстройки частоты, то вмес го сигнала Добавление на вход 10 подается сигнал Вычитани В этом случае разностные счетчики 12 переводятся в режим обратного счета, и число, записанное в блок 1 памяти, уменьщается, а следовательно уменьшается и количество импульсов на выходе элемента ИЛИ 3. С выхода элемента ИЛИ 3 импульсы подстройки поступают на вход блока 8 коррекции. При этом в зависимости от знака подстройки в последовательность импульсов, поступающих на вход блока 8 коррекции из формирователя 2 .импульсов, добавляется или вычитается сформированное элементом ИЛИ 3 ко личество импульсов, и выходная час,тота измеряется на требуемое число дтроцентов (долей процента) относител но номинального значения. Вычитание импульсов осуществляется путем запрета прохождения импульсов, поступающих от формирователя 2 импульсов, импульсами, сформированными элементом ИЛИ 3 на входе тригг ра 16 блока 8 коррекции. Увеличение частоты осуществляется путем добавления сформированных элементом ИЛИ импульсов на входе триггера 17 блок 8 коррекции с одновременным вьгаита нием этих импульсов на входе первог тпмгчвпд 1ft (ппкя 8 коооекиии. 4fo 3 осуществляется только при наличии сигнала на входе блика В коррекции. Таким образом, предлагаемое устройство изменяет частоту следования импульсов на заданную (набранную в блоке памяти и отображаемую блоком индикации) величину в процента , к номинальному значению частоты. Формула изобретения 1. Делитель частоты импульсов, содержащий блок памяти, формирователь импульсов, элемент ИЛИ и счетные декады, и блок индикации, входы которого соединены с выходами блока памяти, выход формирователя импульсов соединен со счетным входом первой счетной декады, отличающийс я тем, что, с целью расширения функциональных возможностей, в него введены первый и второй элементы совпадения и блок коррекции, первый вход которого соединен с вьтходом элемента ИЛИ, входы которого соединены с первыми выходами счетных декад, второй выход каждой из которых соединен со счетным входом следующей счетной декады, информационные входы каждой счетной декады со.едлнены с соответствующей группой выходов блока памяти, первый и второй входы которого соединены с выходами соответственно первого и второго элементов совпадения, первые в:-соды которых соединены соответственно с первым и вторым входами делителя частоты импульсов, третий вход которого соединен с вторыми входами первого и второго элементов совпадения, третьи входы которых соединены с дополнительным выходом формирователя импульсов, выход которого соединен с вторым входом блока коррекции . 2. Делитель по п. 1, отличающийся тем, что блок памяти содержит разностные счетчики, выходы которых соединены с группами выходов блока памяти, первый и второй входы которого соединены соответственно с входами суммирования и вычитания первого разностного счетчика, а входы суммирования и вычитания каждого из остальных разностных счетчиков соединены с выходами соответственно переноса и заема предыдущего раз,ностного счетчика. 3.Делитель поп. -f, отличающийся тем, что каждая счетная декада содержит десятичный счетчик элемент сравнения и формирователь груипы импульсов, выход которого соединен с выходом данной счетной декады, счетный вход которой соединен со счетным входом десятичного счетчика, выходы которого соеди нены с первыми входами элемента срав мения, вторые входы которого соединены с информационными входами данно счетной декады, выходы первого и последнего разрядов десятичного счет чика соединены соответственно с первым и вторым входами формирователя группы импульсов, третий вход которого соединен с выходом элемента сра нения, а дополнительный выход формирователя группы импульсов соединен с дополнительным выходом счетной декады, сч.етный вход счетной декады соединен с четвертым входом формирователя группы импульсов. 4.Делитель по п. 1, о т л и чающийся тем, что блок коррекции содержит первый и второй триг геры, первый и второй элементы И и инвертор, вход которого соединен с первым входом блока коррекции и первыми входами первого и второго элементов И, вторые входы которых ссздинены с вторым входом блока коррекции и первым входом первого триггера, второй вход которого соединен с выходом инвертора, выход первого триггера соединен с третьим входом первого элемента И, выход которого соединен с первым входом второгг триггера, выход и второй вход которого соединены соответственно с выходом блока коррекции и выходом второго элемента И, третий вход которого соединен с дополнительным входом блока коррекции. 5. Делитель по п. 3, отличающийся тем, что каждый формирователь группы импульсов содержит триггер и первый и второй элементы И, первый и второй входы первого элемента И соединены соответственно с первым и вторым входами формирователя группы импульсов, третий вход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого элемента И и первым входом второго элемента И, второй вход и выход которого соедкинены соответственно с выходом триггера и выходом формирователя группы импульсов, четвертый вход которого соединен с третьим входом второго элемента И, а каждый формирователь импульсов, кроме последнего, содержит также инвертор, вход и выход которого соединены соответственно с выходом первого элемента И и дополнительным выходом данного формирователя группы импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 453803, кл. Н 03 К 23/00, 1967. 2.iiBTOpCKoe свидетельство СССР № 242968, кл. Н 03 К 23/00, 1963 (прототип).

Авторы

Даты

1981-09-30—Публикация

1980-01-09—Подача